Ces dernières années, la technologie RDL (Redistribution Layer) a connu un essor considérable. Il s'agit d'une solution d'encapsulation révolutionnaire qui a transformé la manière dont nous encapsulons les circuits intégrés.

Dans cet article, nous allons explorer la définition de la RDL, sa fonction, ses avantages, son processus, son application et sa comparaison avec d'autres technologies d'emballage de circuits intégrés.

Qu'est-ce que la technologie de couche de redistribution ?

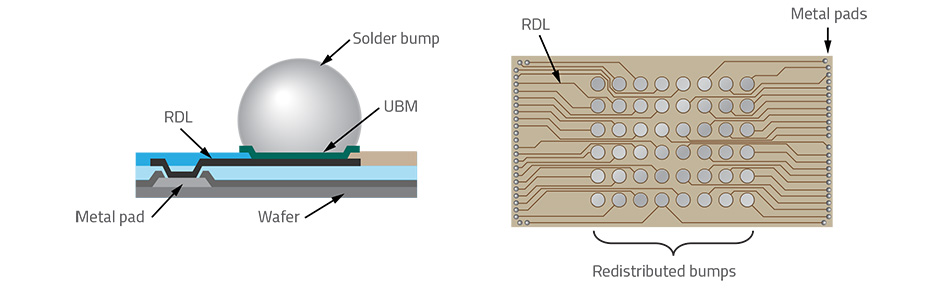

La couche de redistribution, également appelée RDL, est une couche métallique ajoutée à un circuit intégré ou à une micropuce afin de redistribuer les connexions électriques. Cette technologie RDL est une solution d'encapsulation avancée pour les circuits intégrés (CI), qui permet l'intégration de plusieurs puces dans un seul boîtier. Il s'agit d'un processus de création d'une couche métallique structurée au-dessus de la couche diélectrique, qui redistribue les entrées/sorties (E/S) du CI vers un nouvel emplacement. Le nouvel emplacement se trouve généralement au bord de la puce, ce qui permet de connecter le CI à la carte de circuit imprimé (PCB) à l'aide de la technologie de montage en surface (SMT) standard. La technologie RDL permet au concepteur de placer la puce de manière compacte et efficace, réduisant ainsi l'encombrement global du dispositif.

La technologie RDL est essentielle au développement des appareils électroniques modernes, qui sont de plus en plus compacts et complexes. Elle permet de réduire la taille des puces, d'accroître leur vitesse et d'améliorer leur efficacité. Elle est généralement utilisée dans l'encapsulation des dispositifs MEMS, des capteurs, des dispositifs de puissance, des mémoires, des microprocesseurs et des processeurs graphiques.

Fonction de la couche de redistribution

La couche de redistribution (RDL) joue un rôle essentiel dans l'extension et l'interconnexion du plan XY dans la conception et la fabrication des puces.

Redistribuer la connexion E/S

Les plots d'E/S (entrée/sortie) sont des modules de traitement des broches de puces généralement répartis sur le bord ou la périphérie de la puce. Ils peuvent traiter le signal des broches de la puce et transmettre le signal de la puce à la broche après traitement.

Le RDL peut faciliter la redistribution des connexions d'E/S de la puce vers le boîtier. Le RDL relie les plots de connexion de la puce aux broches ou aux billes du boîtier, ce qui facilite l'assemblage et améliore les performances du circuit intégré.

Cela est naturellement pratique pour le processus de câblage, mais quelque peu difficile pour les puces à protubérance. C'est pourquoi le RDL est devenu la clé à ce stade. Il dépose une couche métallique et une couche diélectrique correspondante à la surface de la puce, formant un fil métallique et redessinant les ports E/S vers une nouvelle zone plus spacieuse, formant ainsi une disposition en réseau de surface.

Signaux routiers et alimentation électrique

De plus, le RDL permet également d'acheminer les signaux et l'alimentation au sein du circuit intégré. L'utilisation des RDL est devenue de plus en plus importante à mesure que les circuits intégrés sont devenus plus complexes et nécessitent davantage de connexions d'E/S. Ils sont utilisés dans un large éventail d'applications, telles que les microprocesseurs, les puces mémoire et les capteurs.

Avantages de la couche de redistribution

La technologie RDL offre plusieurs avantages aux concepteurs qui cherchent à créer des appareils électroniques performants, compacts et économiques. Voici quelques-uns des avantages liés à l'utilisation de la technologie RDL dans les boîtiers de circuits intégrés :

Empreinte réduite

La technologie RDL permet d'intégrer plusieurs puces dans un seul boîtier, réduisant ainsi l'encombrement global de l'appareil. Cela permet aux concepteurs de créer des appareils électroniques plus petits et plus compacts, ce qui est essentiel pour des applications telles que les smartphones, les appareils portables et les appareils IoT.

Performances électriques améliorées

La technologie RDL permet au concepteur de placer la puce de manière compacte et efficace, ce qui réduit la longueur des interconnexions. Cela réduit à son tour le retard du signal et améliore les performances électriques du dispositif. La technologie RDL réduit également la capacité et l'inductance parasites, ce qui améliore l'intégrité du signal du dispositif.

Coût réduit

La technologie RDL élimine le besoin de soudure par fil et de soudure flip-chip, qui sont des processus coûteux et chronophages. La technologie RDL réduit également le nombre de composants nécessaires pour le dispositif, ce qui réduit encore davantage son coût. La technologie RDL est une solution rentable pour créer des circuits intégrés haute performance qui nécessitent un format compact.

Types de technologies de couche de redistribution

Il existe deux types de technologie de couche de redistribution (RDL) : fan-in et fan-out. La technologie RDL fan-in est utilisée pour l'encapsulation d'une seule puce, tandis que la technologie RDL fan-out est utilisée pour l'encapsulation de plusieurs puces.

Technologie Fan-in RDL

La technologie RDL fan-in est utilisée pour l'encapsulation d'une seule puce. La technologie RDL fan-in est également connue sous le nom de wafer-level package (WLP), qui est un processus de création d'un boîtier directement sur la plaquette. La technologie RDL fan-in est une solution rentable pour créer des boîtiers petits et minces.

La technologie RDL fan-in convient à des applications telles que les capteurs, les dispositifs MEMS, les dispositifs RF, les microprocesseurs et les dispositifs de mémoire.

Technologie RDL à diffusion

La technologie RDL fan-out est utilisée pour l'encapsulation de plusieurs puces. La technologie RDL fan-out est également connue sous le nom de wafer-level fan-out (WLFO), qui est un processus de création d'un boîtier sur une plaquette reconstituée. La technologie RDL fan-out est une solution rentable pour créer des boîtiers haute performance avec un petit facteur de forme.

La technologie RDL fan-out convient à des applications telles que les processeurs graphiques, les systèmes sur puce (SoC), les dispositifs de mémoire, les dispositifs d'alimentation et les dispositifs LED.

Processus de redistribution

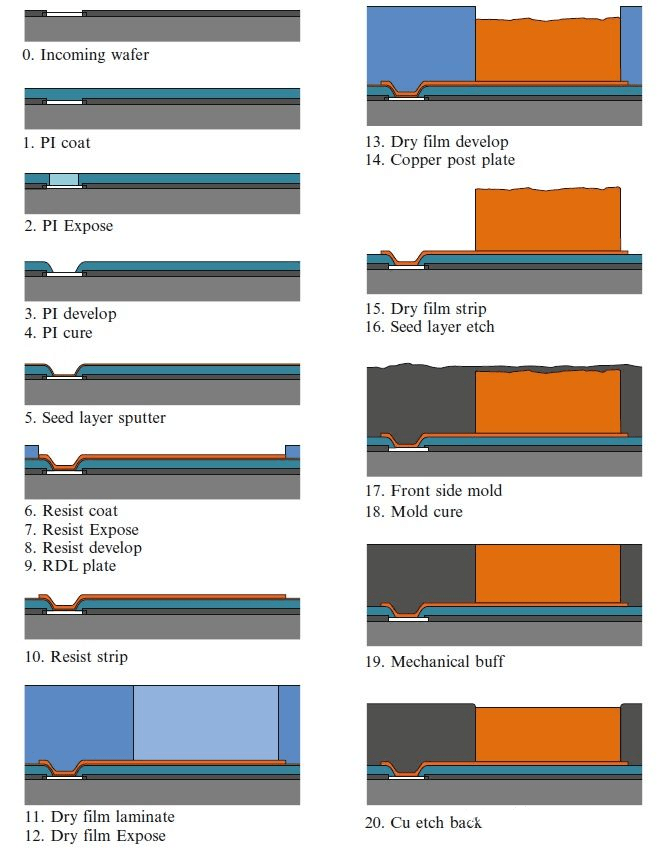

La technologie RDL est un processus complexe qui comprend de nombreuses étapes telles que le dépôt diélectrique, le dépôt métallique, la structuration et la gravure. Vous trouverez ci-dessous le déroulement du processus pour le Fan-in RDL et le Fan-out RDL.

Processus RDL Fan-in

Le processus Fan-in RDL est utilisé dans la production de solutions d'emballage avancées telles que les conceptions WLCSP (Wafer-Level Chip-Scale Packaging) et SiP (System-in-Package). Il permet des niveaux d'intégration plus élevés, des facteurs de forme réduits et des performances améliorées pour les dispositifs à semi-conducteurs. Le processus comprend plusieurs étapes, comme indiqué ci-dessous :

Le processus commence par l'arrivée d'une plaquette, qui est ensuite recouverte de PI (isolant photorésistant) à l'étape 1. Viennent ensuite l'exposition du PI à l'étape 2, le développement du PI à l'étape 3 et le durcissement du PI à l'étape 4.

À l'étape 5, une couche d'amorçage est pulvérisée sur la plaquette, qui est ensuite recouverte de résine photosensible à l'étape 6. La résine photosensible est ensuite exposée à l'étape 7, développée à l'étape 8, et le RDL est plaqué à l'étape 9.

Ensuite, le résist est retiré à l'étape 10 et un film sec est laminé sur la plaquette à l'étape 11. Le film sec est ensuite exposé à l'étape 12 et développé à l'étape 13. Ensuite, des plots de cuivre sont plaqués sur la plaquette à l'étape 14 et le film sec est retiré à l'étape 15.

À l'étape 16, la couche d'amorçage est gravée, et à l'étape 17, un moule avant est créé. Le moule est ensuite durci à l'étape 18, et la plaquette est polie mécaniquement à l'étape 19. Enfin, à l'étape 20, l'excès de cuivre est gravé, ce qui achève le processus Fan-in RDL.

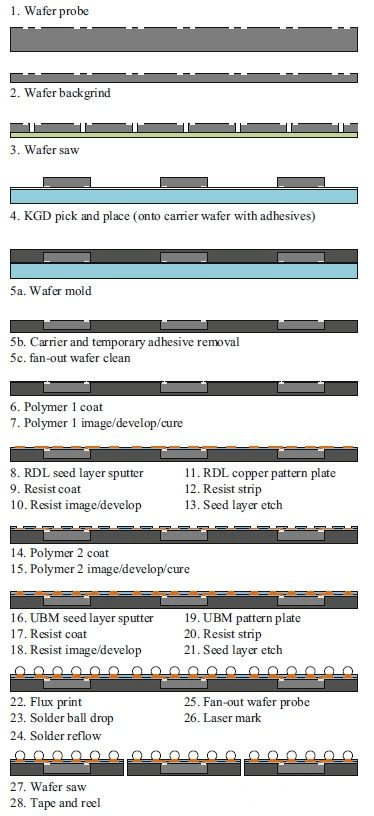

Processus RDL en éventail

Tout comme le processus Fan-in RDL, le processus Fan-out RDL permet également de créer des boîtiers de puces plus petits et plus performants, avec davantage de connexions. Voici les étapes de fabrication :

1. Test des plaquettes : il s'agit du test initial des plaquettes visant à s'assurer qu'elles répondent aux spécifications requises avant de passer aux étapes de traitement suivantes.

2. Rectification arrière de la plaquette : la face arrière de la plaquette est rectifiée jusqu'à une épaisseur spécifiée afin de réduire l'épaisseur du boîtier.

3. Scie à plaquette : la plaquette est découpée en puces individuelles.

4. Sélection et placement des puces KGD (Known Good Die) : les puces en bon état sont sélectionnées et transférées sur une plaquette de support à l'aide d'un adhésif.

5a. Moulage de la plaquette : la plaquette avec les puces fixées à la plaquette de support est moulée avec un matériau diélectrique pour former une structure en éventail.

5b. Retrait du support et de l'adhésif temporaire : la plaquette de support est retirée de la plaquette en éventail, et tout adhésif temporaire utilisé pendant le processus est également retiré.

5c. Nettoyage de la plaquette en éventail : la plaquette en éventail est nettoyée pour éliminer toutes les particules ou impuretés restantes.

6. Couche de polymère 1 : une couche de polymère est appliquée à la surface de la plaquette en éventail pour servir de couche diélectrique.

7. Image/développement/durcissement du polymère 1 : la couche de polymère est structurée à l'aide de la photolithographie afin de créer la forme et la taille souhaitées de la structure RDL.

8. Pulvérisation de la couche d'amorçage RDL : une fine couche de cuivre ou d'un autre matériau conducteur est déposée sur la couche de polymère à l'aide d'un procédé de pulvérisation.

9. Couche de résine photosensible : une couche de résine photosensible est appliquée sur la couche d'amorçage.

10. Image/développement de la résine photosensible : la couche de résine photosensible est structurée à l'aide de la photolithographie afin de créer la forme et la taille souhaitées de la structure RDL.

11. Plaque de cuivre RDL : du cuivre est déposé sur les zones exposées de la couche d'amorçage à l'aide d'un procédé de galvanoplastie, créant ainsi le motif RDL souhaité.

12. Décapage de la résine photosensible : le matériau résistant restant est éliminé, ne laissant que le motif RDL en cuivre.

13. Gravure de la couche d'amorçage : la partie inutile de la couche d'amorçage est éliminée par gravure.

14. Couche de polymère 2 : une autre couche de polymère est appliquée sur la structure RDL pour servir de couche diélectrique.

15. Image/développement/durcissement du polymère 2 : la couche de polymère est modelée à l'aide de la photolithographie afin de créer la forme et la taille souhaitées de la structure UBM.

16. Pulvérisation de la couche d'amorçage UBM : une fine couche de cuivre ou d'un autre matériau conducteur est déposée sur la couche de polymère par pulvérisation.

17. Couche de résine photosensible : une couche de résine photosensible est appliquée sur la couche d'amorçage.

18. Image/développement de la résine photosensible : la couche de résine photosensible est structurée par photolithographie afin d'obtenir la forme et la taille souhaitées pour la structure UBM.

19. Plaque à motif UBM : du cuivre est déposé sur les zones exposées de la couche d'amorçage à l'aide d'un procédé de galvanoplastie, créant ainsi le motif UBM souhaité.

20. Décapage de la résine photosensible : le matériau résistant restant est éliminé, ne laissant que le motif UBM en cuivre.

21. Gravure de la couche d'amorçage : la partie inutile de la couche d'amorçage est retirée par gravure.

22. Impression du flux : un matériau de flux est appliqué sur les pastilles UBM.

23. Dépôt de billes de soudure : des billes de soudure sont placées sur les pastilles UBM.

24. Refusion de la soudure : les billes de soudure sont chauffées pour fondre et former des connexions entre les pastilles UBM et les conducteurs ou bosses externes.

25. Sonde de wafer en éventail : le circuit intégré encapsulé est testé pour s'assurer qu'il répond aux spécifications requises.

26. Marquage laser : un identifiant unique ou un code-barres est gravé à la surface du circuit intégré à l'aide d'un laser.

27. Scie à plaquettes : la plaquette fan-out est découpée en boîtiers individuels.

28. Ruban et bobine : les circuits intégrés emballés individuellement sont montés sur une bobine pour faciliter leur manipulation et leur expédition.

Appliquer la technologie RDL à l'emballage avancé

Dans les emballages avancés tels que les boîtiers fan-in wafer-level (FIWLP) et les boîtiers fan-out wafer-level (FOWLP), la technologie RDL est la plus importante. C'est l'essor de cette technologie qui a permis aux usines d'emballage de rivaliser avec les fonderies de plaquettes dans le domaine de la technologie d'emballage fan-out. Grâce à la technologie RDL, l'IOPad peut être transformé en différents types de boîtiers wafer-level dans les boîtiers FIWLP ou FOWLP. Dans le FIWLP, les bosses sont toutes développées sur la puce, et la connexion entre la puce et le pad dépend principalement de la ligne métallique du RDL. Après l'encapsulation, le circuit intégré a presque la même taille que la surface de la puce. Dans le FOWLP, les bosses peuvent se développer à l'extérieur de la puce, et le circuit intégré après encapsulation est plus grand que la surface de la puce (1,2 fois).

En particulier, dans les boîtiers avancés 2.5D, outre le TSV sur le substrat en silicium, le RDL est également indispensable. Prenons l'exemple de l'InFO de TSMC, un représentant des boîtiers avancés 2.5D. L'InFO utilise une ou plusieurs puces nues sur le support, qui sont ensuite intégrées dans la plaquette reconstituée du composé de moulage. Ensuite, les interconnexions RDL et les couches diélectriques sont fabriquées sur la plaquette, ce qui correspond à un flux de processus « chip first ». L'InFO à puce unique offre un nombre élevé de bosses, et les lignes RDL s'étendent de la zone de la puce vers l'extérieur, formant une topologie « fan-out ».

Quelle technologie de couche de redistribution dois-je utiliser ?

Comme nous l'avons déjà mentionné, il existe deux technologies RDL : Fan-in RDL et Fan-out RDL. Comment choisir la technologie appropriée pour créer des appareils électroniques performants, compacts et rentables ? Cela dépend de plusieurs facteurs, tels que le type d'application, le nombre de puces et les exigences en matière de performances.

Application

La technologie RDL fan-in convient à des applications telles que les capteurs, les dispositifs MEMS et les dispositifs RF. La technologie RDL fan-out convient à des applications telles que les processeurs graphiques, les systèmes sur puce (SoC) et les dispositifs de mémoire.

Nombre de matrices

La technologie RDL fan-in convient à l'encapsulation d'une seule puce, tandis que la technologie RDL fan-out convient à l'encapsulation de plusieurs puces.

Exigences en matière de performance

La technologie RDL fan-in convient à la création de boîtiers petits et fins, tandis que la technologie RDL fan-out convient à la création de boîtiers haute performance avec un facteur de forme réduit.

Comparaison entre la technologie RDL et d'autres technologies d'encapsulation des circuits intégrés

En raison des différents processus, plusieurs technologies d'emballage sont disponibles pour les circuits intégrés. Vous trouverez plus d'informations sur leurs différences dans le tableau ci-dessous :

| IC Packaging | Description | Advantages | Disadvantages | Applications |

|---|---|---|---|---|

| Wire Bonding | Connecting the IC to the PCB using wires | Low cost, flexible, proven technology | Limited performance, not suitable for high-frequency and high-power applications | Consumer electronics, automotive, medical devices |

| Flip-Chip Bonding | Chips are bonded face-down to the substrate, Connecting the IC to the PCB using solder bumps | High performance, high-density, low inductance | Expensive, requires precise alignment and underfilling | High-speed data communication, high-power applications, microprocessors |

| Through-Silicon Via (TSV) | Creating vertical interconnects through the silicon substrate | Shorter interconnect lengths, higher performance, smaller form factor | Complex and expensive manufacturing process, thermal and mechanical stress issues | Memory devices, image sensors, 3D ICs |

| Chip-scale package (CSP) | Replacing the lead frame with a substrate | Small form factor, high density, low cost | Limited I/O, susceptibility to mechanical and thermal stress | Mobile devices, wearable technology |

| Integrated Fan-out (InFO) | Integrated package of multiple chips and the soldering point of the pin is outside of the chip | High density, small form factor, low power consumption | Complex manufacturing process, high cost | Mobile devices, IoT, wearable technology |

| High Bandwidth Memory (HBM) | 3D stacking technology | High bandwidth, low power consumption | Expensive, limited scalability | High-performance computing, graphics processing |

| Chip on Wafer on Substrate (CoWoS) | Integrate chip and silicon wafer (substrate) together | High bandwidth, low power consumption, heterogeneous integration | Complex manufacturing process, high cost | High-performance computing, graphics processing |

| Redistribution Layer (RDL) | Creating a patterned metal layer on top of the dielectric layer | High density, fine pitch, low profile | Limited power handling capability, susceptibility to mechanical and thermal stress | Mobile devices, consumer electronics |

| Bump Technology | Depositing small metal bumps on the chip | Low cost, simple manufacturing process, flexible design | Limited performance, not suitable for high-speed and high-power applications | Consumer electronics, automotive, medical devices |

Entreprises proposant des solutions technologiques de couche de redistribution

Plusieurs entreprises proposent des solutions technologiques de couche de redistribution (RDL), telles que :

Groupe ASE

ASE Group est un fournisseur mondial de services de fabrication de semi-conducteurs. ASE Group propose une large gamme de solutions technologiques RDL pour diverses applications telles que les mémoires, les microprocesseurs et les processeurs graphiques.

Amkor Technology

Amkor Technology est un fournisseur mondial de services d'emballage et de test de semi-conducteurs. Amkor Technology propose une large gamme de solutions technologiques RDL pour diverses applications telles que les capteurs, les dispositifs MEMS et les dispositifs de puissance.

Taiwan Semiconductor Manufacturing Company

TSMC est une fonderie mondiale de semi-conducteurs qui propose une large gamme de solutions technologiques RDL pour diverses applications telles que les systèmes sur puce (SoC), les dispositifs de mémoire et les dispositifs de puissance.

Conclusion

La technologie RDL (Redistribution Layer) est une solution d'encapsulation révolutionnaire qui a transformé la manière dont nous encapsulons les circuits intégrés (CI). Elle permet d'établir davantage de connexions sur une seule puce, réduisant ainsi l'encombrement global du dispositif. Elle est donc utilisée dans diverses applications telles que les smartphones, les appareils portables et les appareils IoT. L'avenir de la technologie RDL dans le domaine des boîtiers de circuits intégrés est prometteur et devrait avoir un impact significatif sur l'industrie électronique dans les années à venir.