Analyse des défaillances des circuits intégrés

Ressource technique complète sur les méthodologies, les outils et les études de cas d'analyse des défaillances des semi-conducteurs

Qu'est-ce que l'analyse des défaillances des circuits intégrés?

L'analyse des défaillances des circuits intégrés (CI) est un processus systématique permettant d'identifier, d'isoler et de déterminer la cause première des défaillances des dispositifs semi-conducteurs. Cette discipline d'ingénierie essentielle combine des techniques d'imagerie avancées, des tests électriques et la science des matériaux pour résoudre les problèmes des circuits intégrés dans divers secteurs industriels.

Une analyse efficace des défaillances améliore la fiabilité des produits, réduit les coûts de fabrication, accélère leur mise sur le marché et garantit la conformité aux normes industrielles. Elle joue un rôle essentiel dans le contrôle qualité, l'ingénierie de la fiabilité et les cycles d'amélioration des produits.

Objectifs clés de l'analyse des défaillances des circuits intégrés

- Identifier les causes profondes des défaillances des circuits intégrés par une enquête systématique

- Déterminer si les défaillances proviennent de la conception, de la fabrication ou de l'application

- Élaborer des mesures correctives pour prévenir les défaillances futures.

- Valider la fiabilité et les performances des circuits intégrés

- Signalement des défaillances et analyse des données de fiabilité

Guides techniques et méthodologies

Organigramme de diagnostic

Approche systématique allant du symptôme de défaillance à l'identification de la cause racine

Chemin d'absence de panne d'alimentation/de sortie

- 1. Vérifier la présence de dommages dus aux décharges électrostatiques à l'aide de l'analyse MEB/EDS

- 2. Vérifier les joints de soudure par inspection aux rayons X 3D

- 3. Test de claquage de l'oxyde de grille à l'aide d'EMMI

- 4 Effectuer des tests de continuité avec OBIRCH

- 5. Analyser l'intégrité du paquet avec C-SAM

Défaillances intermittentes

- 1. Éliminer les microfissures BGA à l'aide du C-SAM

- 2. Vérifier la présence de contraintes thermiques par imagerie infrarouge

- 3. Test de verrouillage lié à la conception par simulation de circuit

- 4. Vérifier l'intégrité du réseau de distribution électrique

Guide d'utilisation EMMI

Flux de travail étape par étape pour l'analyse par microscopie d'émission

Préparation du dispositif

Mettez l'appareil sous tension en mode de reproduction des pannes, assurez-vous d'un refroidissement adéquat

Installation de la chambre noire

Positionnez l'appareil sous le microscope EMMI et assurez-vous d'un alignement correct.

Configuration de la caméra

Réglez le temps d'exposition approprié (généralement de 10 à 60 secondes) et la sensibilité.

Acquisition d'images

Capturez plusieurs images avec des temps d'exposition différents pour des résultats optimaux.

Analyse et superposition

Superposez les zones d'émission au schéma de conception pour identifier les structures défaillantes.

Conseil de dépannage

Si aucun point chaud n'apparaît, vérifiez que la puce est dans un état reproduisant la panne et vérifiez si le mécanisme de panne produit des émissions de photons (les circuits ouverts n'en produisent généralement pas).

Pièges courants de l'analyse des défaillances

Négligence des dommages causés par les décharges électrostatiques

Ne pas tenir compte des dommages causés par les décharges électrostatiques lors de la manipulation, notamment des puces CMOS. Toujours vérifier le bon fonctionnement du bracelet antistatique et les protocoles de mise à la terre.

Déclassement de puissance inadéquat

Risque de surchauffe des résistances suite à un fonctionnement à plus de 80 % de la charge nominale. Il est recommandé de réduire la puissance de 50 % afin de garantir la fiabilité dans des conditions variables.

Reproduction incorrecte de l'échec

Analyser les dispositifs dans des conditions qui ne reproduisent pas fidèlement le scénario de défaillance sur le terrain conduit à une identification incorrecte de la cause première.

Négliger les problèmes d'emballage

Se concentrer exclusivement sur les problèmes au niveau de la puce, en passant à côté des défaillances liées au boîtier comme le délaminage, la corrosion des fils ou la fatigue des joints de soudure.

Documentation insuffisante

Le fait de ne pas documenter chaque étape d'analyse de manière exhaustive rend difficile la reproduction des résultats ou l'analyse des tendances sur plusieurs défaillances.

Problèmes d'étalonnage des outils

L'utilisation d'équipements mal calibrés entraîne des mesures inexactes et des conclusions erronées quant à l'analyse des défaillances.

Études de cas industrielles

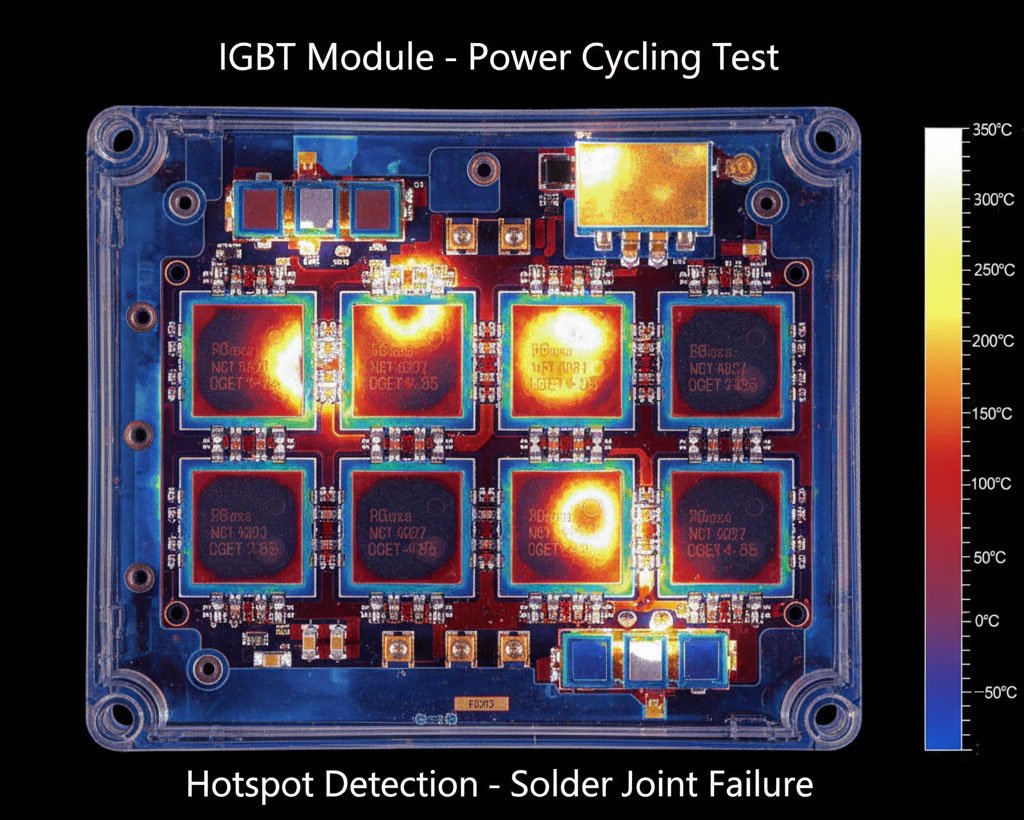

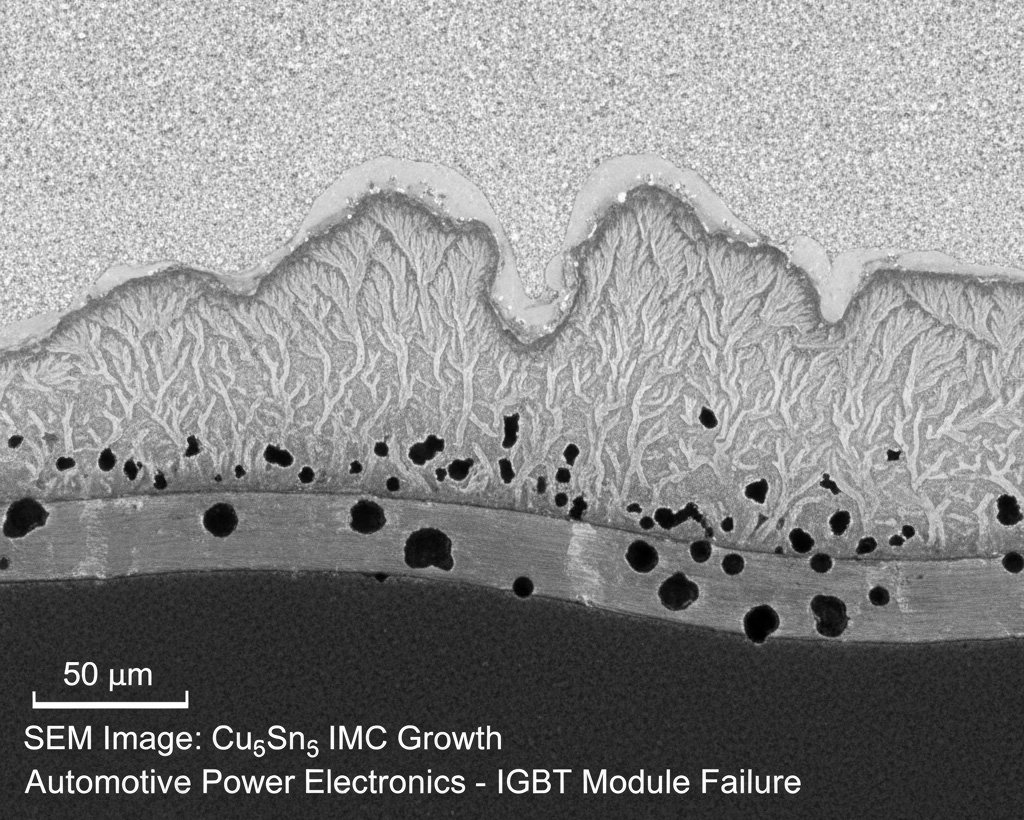

Défaillance du module IGBT dans les véhicules électriques

Symptôme

Perte de puissance soudaine pendant la charge, sans dommage externe visible sur le groupe motopropulseur du véhicule électrique.

Processus d'analyse

- L'imagerie thermique a révélé des points chauds dans le module IGBT lors des cycles de mise sous tension/sous tension

- L'analyse MEB/EDS a révélé une croissance excessive d'IMC (Cu₆Sn₅) dans les joints de soudure.

- L'examen en coupe transversale a révélé la formation de vides de Kirkendall à l'interface soudure-substrat.

- La simulation par éléments finis a établi un lien entre la défaillance et un profil de refusion de soudure insuffisant.

Solution et résultat

Profil de refusion ajusté pour assurer un mouillage correct et ajout de pastilles nickelées pour contrôler la croissance de l'IMC.

Résultat : Le taux de défaillance sur le terrain a diminué de 0,58 % par an, ce qui a permis d'économiser 2 millions de dollars en coûts de garantie.

Normes pertinentes

Résultats de l'imagerie thermique

Image MEB de la croissance IMC

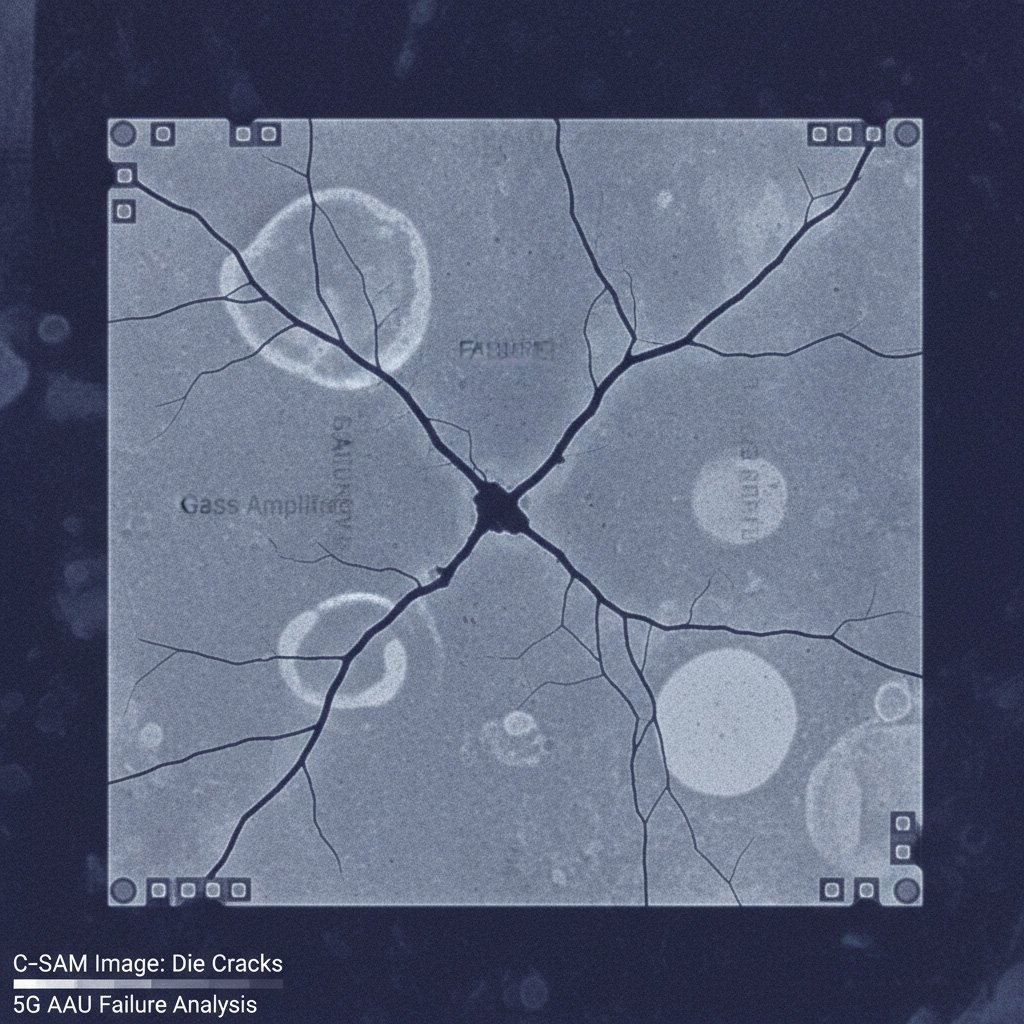

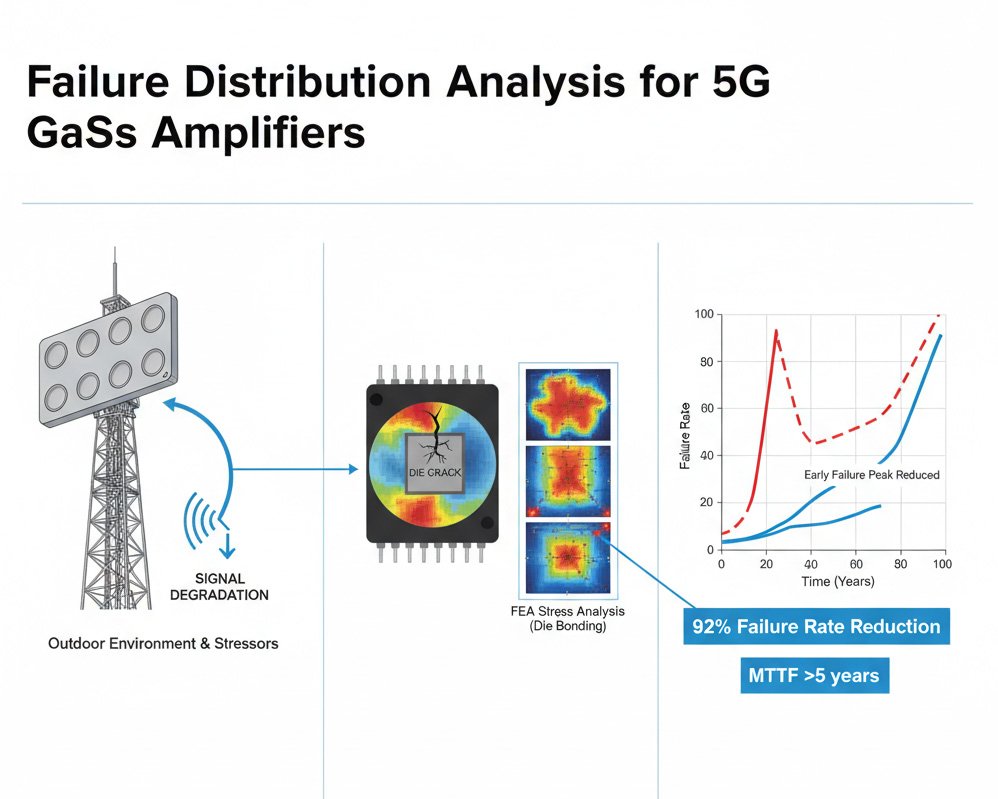

Défaillance des amplificateurs GaAs dans les unités d'amplification 5G

Symptôme

Défaillances sur le terrain des unités d'antennes actives 5G (AAU) dans les 6 mois suivant leur déploiement, entraînant une dégradation du signal.

Processus d'analyse

- L'inspection C-SAM a détecté des fissures dans les puces des amplificateurs de puissance GaAs.

- Un audit d'emballage a révélé des marques d'éjection anormales sur la face arrière de la matrice.

- L'analyse des données de fiabilité a montré que la distribution des défaillances correspondait au mode de défaillance précoce.

- L'analyse par éléments finis a confirmé les contraintes mécaniques lors du collage de la puce.

Solution et résultat

Film bleu de collage de puce modifié pour réduire les contraintes mécaniques et mise en œuvre d'une inspection post-collage à 100 % à l'aide d'une inspection optique automatisée.

Résultat : Le taux de défaillance a été réduit de 92 %, ce qui porte le délai moyen entre les pannes à plus de 5 ans.

Normes pertinentes

Image C-SAM des fissures de la matrice

Analyse de la distribution des défaillances

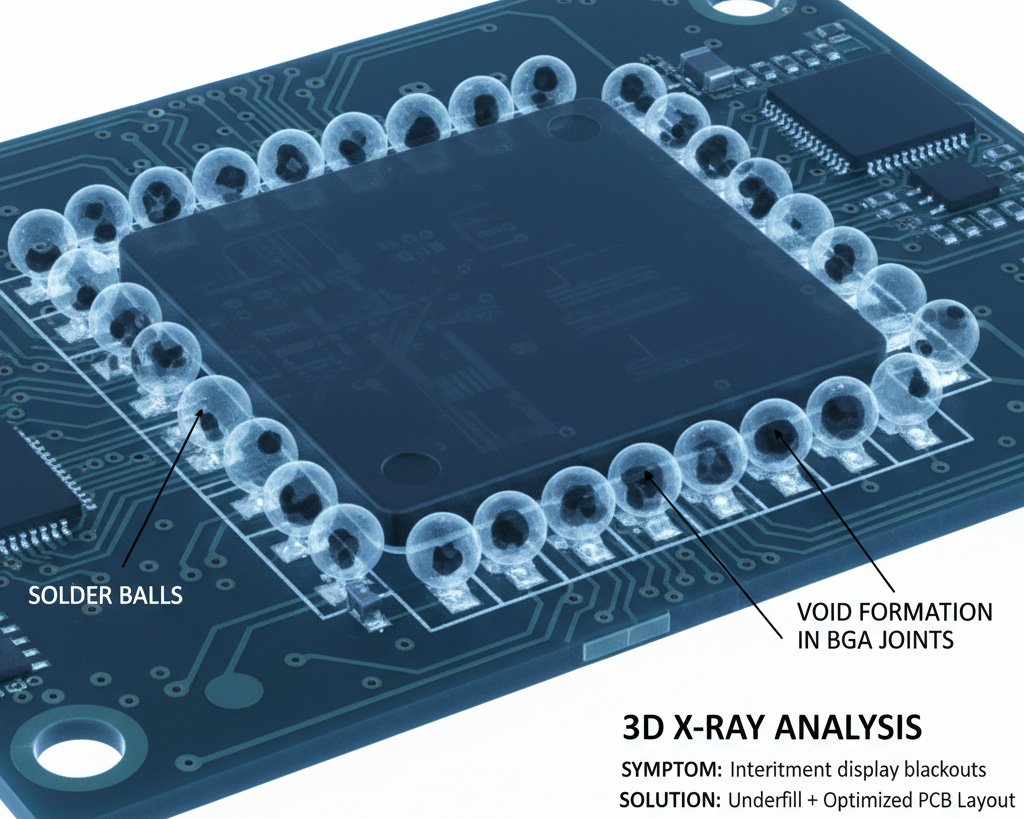

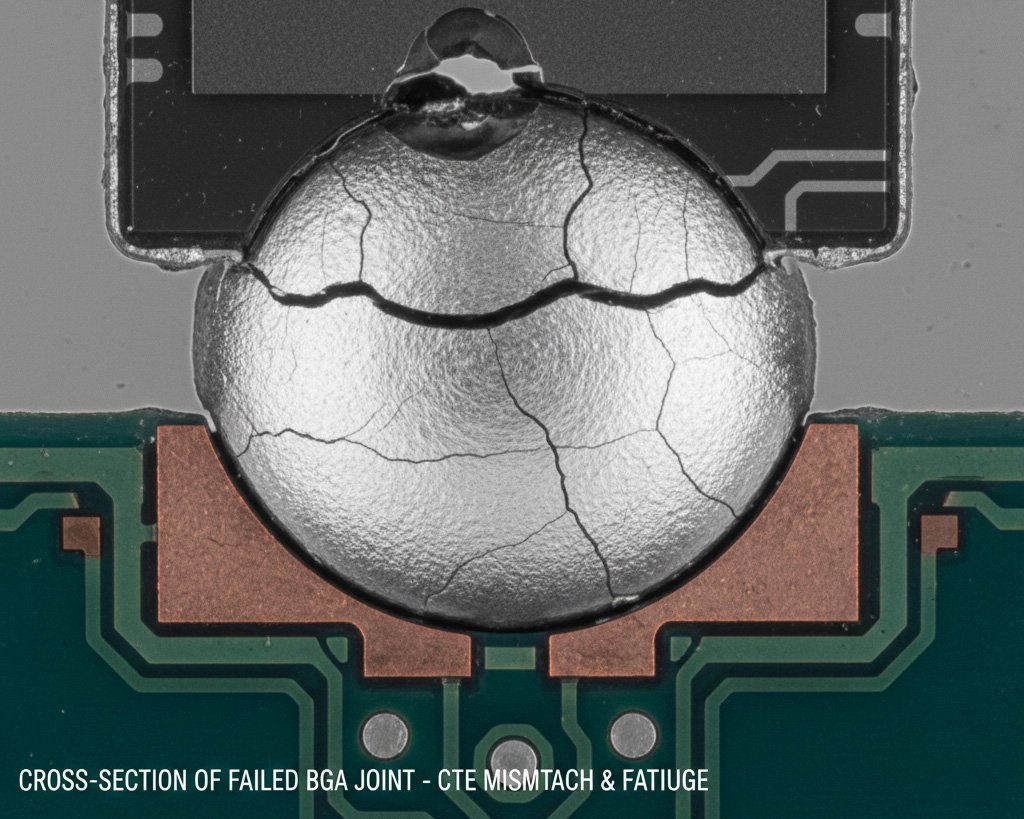

Défaillance BGA dans les smartphones

Symptôme

Des coupures d'écran intermittentes et un écran tactile non réactif apparaissent sur les smartphones haut de gamme après 6 à 8 mois d'utilisation.

Processus d'analyse

- Les cycles thermiques (de -40 °C à 85 °C) ont reproduit la défaillance en conditions de laboratoire.

- La microscopie acoustique à balayage (SAM) a révélé une fatigue des joints de soudure.

- L'analyse en coupe transversale a confirmé la différence de coefficient de dilatation thermique (CTE).

- L'analyse par rayons X 3D a quantifié la formation de vides dans 18 % des joints BGA.

Solution et résultat

Mise en œuvre d'un sous-remplissage avec une Tg (température de transition vitreuse) plus élevée et optimisation de la disposition du circuit imprimé pour réduire les gradients thermiques.

Résultat : Les retours sur le terrain ont diminué de 76 %, sans aucune défaillance signalée après 18 mois d'utilisation.

Normes pertinentes

Radiographie 3D des cavités BGA

Coupe transversale d'un joint défaillant

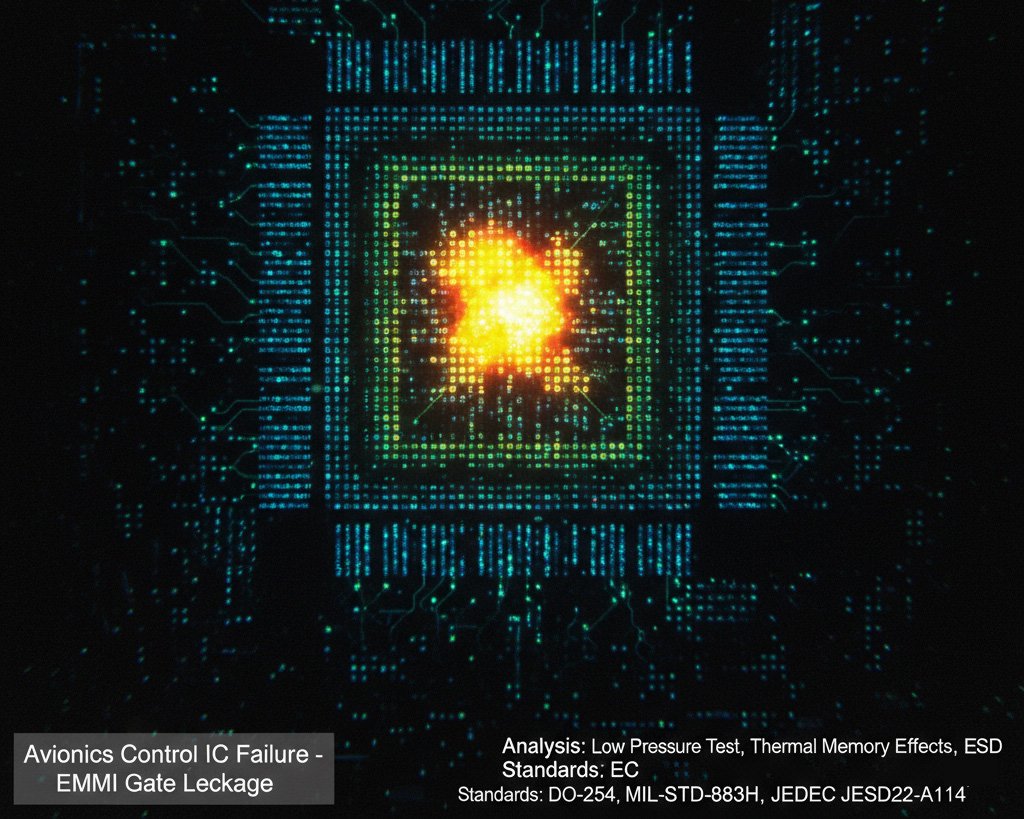

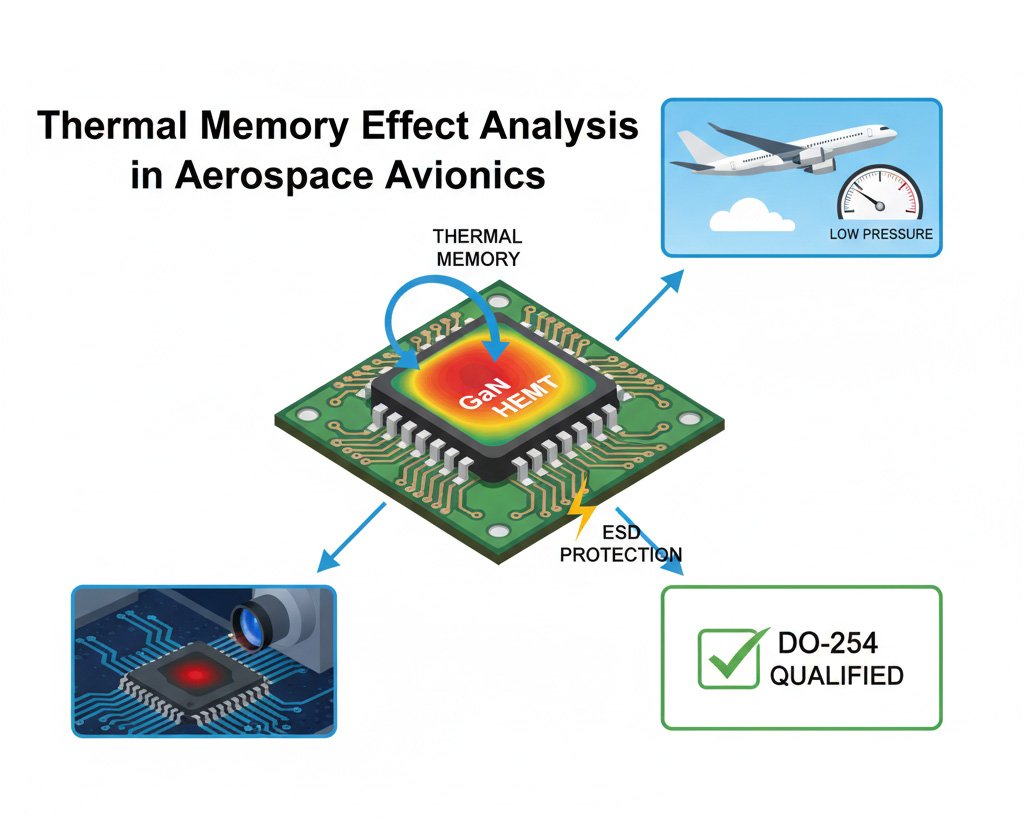

Défaillance du circuit intégré de commande avionique

Symptôme

Réinitialisations aléatoires des systèmes dans les modules de commande avioniques pendant les vols à haute altitude, sans schéma clair.

Processus d'analyse

- Les essais environnementaux ont reproduit la défaillance dans des conditions de basse pression (haute altitude).

- EMMI a détecté une fuite de courant intermittente dans le circuit intégré de gestion de l'alimentation.

- La modélisation IC-CAP a permis d'identifier des effets de mémoire thermique non modélisés dans les transistors HEMT GaN.

- Les tests ESD ont révélé une protection insuffisante dans les circuits d'entrée.

Solution et résultat

Modèle ASM-HEMT mis à jour pour inclure les effets de mémoire thermique et un circuit de protection ESD amélioré.

Résultat : Élimination complète des réinitialisations en vol, avec une qualification réussie selon les normes DO-254.

Normes pertinentes

Image EMMI de la fuite de grille

Analyse de l'effet de mémoire thermique

Outils et équipements

| Outil | Cas d'utilisation principal | Limite de résolution | Idéal pour | Limitation |

|---|---|---|---|---|

| EMMI | Localisation des points chauds (fuites, pannes) | ~1 μm | CMOS/FinFETs | Aucun signal pour les circuits ouverts |

| C-SAM | Détection de délamination/vide | 50 nm | Flip-chip, BGA | Nécessite un couplage liquide |

| Tomodensitométrie 3D par rayons X | Inspection des TSV/puces empilées | 100 nm | Circuits intégrés 3D | Coût élevé pour une haute résolution |

| Thermographie à verrouillage | Cartographie thermique inférieure au °C | 0,1°C | Circuits intégrés de puissance (IGBT) | Temps de numérisation lent |

| MEB/EDS | Caractérisation des matériaux, imagerie des défauts | 1-5 nm | Analyse physique au niveau de la puce | Nécessite un revêtement conducteur pour les isolateurs |

| FIB-SEM | Coupe transversale, édition de circuits | 5 nm | Circuits intégrés 3D, emballage avancé | Destructeur, chronophage |

Guide d'association outil-technique

L'utilisation des outils appropriés pour chaque scénario de défaillance spécifique garantit une analyse des causes profondes efficace et précise.

Analyse des dommages causés par les décharges électrostatiques

- Commencez par utiliser EMMI pour localiser les sites de fuite.

- Poursuivre avec une analyse FIB-SEM pour l'imagerie à l'échelle nanométrique des dommages.

- Utiliser la spectroscopie EDS pour vérifier la présence de contamination sur les sites de défaillance.

- Vérifier par des tests électriques (analyse de la courbe IV)

Fissures TSV des circuits intégrés 3D

- Utiliser la tomographie par rayons X 3D pour l'inspection non destructive

- Valider par coupe transversale FIB aux emplacements critiques

- Effectuer une imagerie MEB pour caractériser la morphologie des fissures

- Appliquer l'analyse par éléments finis pour déterminer les origines des contraintes.

Défaillances liées à la chaleur

- Commencez par la thermographie à verrouillage de phase pour la cartographie thermique

- Utilisez le C-SAM pour vérifier la présence de délamination due aux contraintes thermiques.

- Effectuer une coupe transversale pour examiner l'intégrité des joints de soudure

- Valider par des tests de cyclage thermique

Défaillances intermittentes

- Utiliser une chambre environnementale pour reproduire les conditions de défaillance.

- Appliquer OBIRCH pour l'analyse dynamique du chemin de courant

- Utiliser l'imagerie thermique lors des tests de résistance

- Vérifier par des tests de vibration si une contrainte mécanique est suspectée

Outils et technologies émergents

EMMI amélioré par l'IA

Des algorithmes d'apprentissage automatique qui distinguent automatiquement les schémas d'émission de photons normaux et anormaux, réduisant ainsi le temps d'analyse jusqu'à 70 %.

Marquage des points quantiques

Des marqueurs fluorescents à l'échelle nanométrique qui mettent en évidence les régions défectueuses des semi-conducteurs, permettant une détection plus précoce des sites de défaillance potentiels.

Plateformes d'analyse fonctionnelle prédictive

Des systèmes intégrés qui combinent données de fabrication, rapports de défaillance sur le terrain et intelligence artificielle pour prédire les mécanismes de défaillance potentiels avant qu'ils ne surviennent.

Normes et conformité

Normes JEDEC

JESD22-A121: Tests ESD

Définit les procédures de test de décharge électrostatique pour le modèle du corps humain (HBM), le modèle de machine (MM) et le modèle de dispositif chargé (CDM).

JESD47: Méthodes d’essai de contrainte pour les circuits intégrés

Norme complète couvrant divers tests de contrainte, notamment les cycles de température, la tension et la température, l'électromigration et la rupture diélectrique dépendante du temps.

JESD22-A104: Cycles de température

Norme spécifique pour les essais de cyclage thermique permettant d'évaluer la fiabilité des composants dans des conditions de contrainte thermique.

Normes spécifiques à l'industrie

AEC-Q100: Circuits intégrés automobiles

Spécifications de qualification pour les circuits intégrés utilisés dans les applications automobiles, avec des exigences de fiabilité rigoureuses.

DO-254 : Avionique aérospatiale

Recommandations pour l'assurance de la conception des matériels électroniques embarqués, y compris les circuits intégrés utilisés dans les systèmes critiques de vol.

Telcordia GR-468 : Télécommunications

Exigences relatives à l'assurance de la fiabilité des dispositifs semi-conducteurs utilisés dans les équipements de télécommunications.

Analyse des données de fiabilité

Une analyse efficace des défaillances nécessite une analyse statistique des données de fiabilité afin de comprendre les distributions des défaillances et de prédire la durée de vie du produit:

Distributions des défaillances

- Distribution log-normale: courante pour les défaillances des semi-conducteurs

- Distribution de Weibull: utile pour analyser les défaillances précoces, aléatoires et d’usure.

- Distribution exponentielle: appropriée pour les régions à taux de défaillance constant

Indicateurs clés

- MTBF (Temps moyen entre les pannes)

- Taux de défaillance (λ) - généralement exprimé en FIT (Défaillances dans le temps : 1 FIT = 1 défaillance pour 10^9 heures-appareil)

- Facteurs de conversion des essais de durée de vie accélérés (ALT)

Exemple d'analyse du taux de défaillance

Tendances futures en matière d'analyse des défaillances des circuits intégrés

Nœuds de processus avancés (2 nm/1 nm)

Les défis de l'analyse à l'échelle atomique, les effets quantiques devenant des facteurs importants dans les mécanismes de défaillance.

Principaux défis

- • Effets de tunnel quantique

- • Défauts d'alimentation côté arrière

- • Détection de la contamination au niveau atomique

Solutions émergentes

- • Microscope électronique à transmission cryogénique pour l'inspection à l'échelle atomique

- • AI-driven nanoprobing techniques

- • Tomographie par sonde atomique avancée

Circuits intégrés 3D et intégration hétérogène

Modes de défaillance complexes dans les architectures de puces empilées nécessitant de nouvelles techniques d'analyse non destructives.

Principaux défis

- • Fissuration des TSV (Through-Silicon Via)

- • Délamination du sous-remplissage dans les matrices empilées

- • Problèmes de gestion thermique

Solutions émergentes

- • Scanner 3D à rayons X de pointe avec une résolution plus élevée

- • Techniques d'imagerie multimodale

- • Conception pour la testabilité dans les circuits intégrés 3D

IA et apprentissage automatique

Détection et classification automatisées des défaillances pour gérer la complexité croissante des circuits intégrés.

Applications clés

- • Classification automatisée des défauts dans les images MEB

- • Analyse prédictive des défaillances à partir des données de fabrication

- • Détection d'anomalies dans les données de test des plaquettes

Avantages

- • Réduction de 50 à 70 % du temps d'analyse

- • Amélioration de la précision dans l'identification des causes profondes

- • Prédiction précoce des défaillances avant le déploiement sur le terrain