In den letzten Jahren hat die Redistribution Layer (RDL)-Technologie erheblich an Bedeutung gewonnen. Es handelt sich um eine revolutionäre Verpackungslösung, die die Art und Weise, wie wir ICs verpacken, grundlegend verändert hat.

In diesem Artikel werden wir uns mit der Definition von RDL, ihrer Funktion, ihren Vorteilen, ihrem Prozess, ihrer Anwendung und dem Vergleich mit anderen IC-Verpackungstechnologien befassen.

Was ist Redistribution Layer-Technologie?

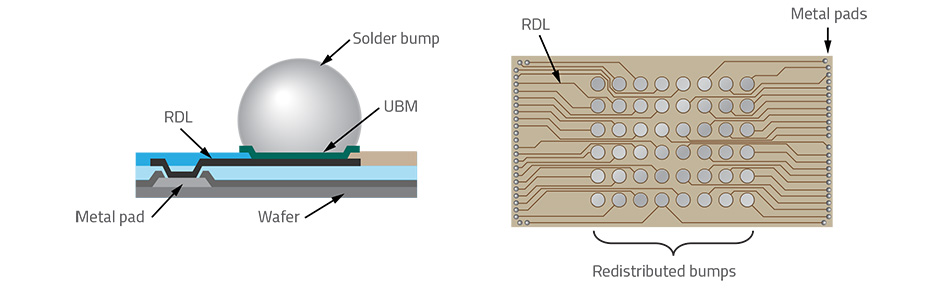

Die Redistribution Layer (RDL) ist eine Metallschicht, die auf einen integrierten Schaltkreis oder Mikrochip aufgebracht wird, um die elektrischen Verbindungen neu zu verteilen. Diese RDL-Technologie ist eine fortschrittliche Verpackungslösung für integrierte Schaltkreise (ICs), die die Integration mehrerer Chips in einem einzigen Gehäuse ermöglicht. Dabei wird eine strukturierte Metallschicht auf der dielektrischen Schicht aufgebracht, die die Ein-/Ausgänge (I/O) des ICs an einen neuen Ort umverteilt. Der neue Ort befindet sich in der Regel am Rand des Chips, wodurch der IC mit Hilfe der Standard-Oberflächenmontagetechnologie (SMT) mit der Leiterplatte (PCB) verbunden werden kann. Die RDL-Technologie ermöglicht es dem Konstrukteur, den Chip kompakt und effizient zu platzieren und so die Gesamtfläche des Geräts zu reduzieren.

Die RDL-Technologie ist für die Entwicklung moderner elektronischer Geräte, die immer kompakter und komplexer werden, von entscheidender Bedeutung. Sie ermöglicht kleinere, schnellere und effizientere Chips. Sie wird in der Regel bei der Verpackung von MEMS-Geräten, Sensoren, Leistungsbauelementen, Speichern, Mikroprozessoren und Grafikprozessoren eingesetzt.

Funktion der Umverteilungsschicht

Die Redistribution Layer (RDL) spielen eine entscheidende Rolle bei der Erweiterung und Verbindung der XY-Ebene im Chipdesign und in der Chipfertigung.

I/O-Verbindung neu verteilen

I/O-Pads (Input/Output) sind Chip-Pin-Verarbeitungsmodule, die in der Regel am Rand oder an der Peripherie des Chips angeordnet sind. Sie können das Signal der Chip-Pins verarbeiten und das Signal des Chips nach der Verarbeitung an den Pin ausgeben.

RDL kann die Umverteilung der I/O-Verbindungen vom Chip zum Gehäuse erleichtern. Das RDL verbindet die Bondpads auf dem Chip mit den Gehäuseanschlüssen oder -kugeln, was eine einfachere Montage und eine bessere Leistung des IC ermöglicht.

Dies ist natürlich für den Bonddrahtprozess praktisch, stellt jedoch für Flip-Chips eine gewisse Herausforderung dar. Daher wurde RDL zum Schlüssel für diesen Moment. Es lagert eine Metallschicht und eine entsprechende dielektrische Schicht auf der Oberfläche des Chips ab, bildet einen Metalldraht und gestaltet die IO-Ports zu einem neuen, geräumigeren Bereich um, wodurch ein Oberflächenarray-Layout entsteht.

Streckensignale und Stromversorgung

Darüber hinaus bietet RDL auch eine Möglichkeit, Signale und Strom innerhalb des ICs zu leiten. Der Einsatz von RDLs hat zunehmend an Bedeutung gewonnen, da ICs immer komplexer werden und mehr I/O-Verbindungen erfordern. Sie werden in einer Vielzahl von Anwendungen eingesetzt, beispielsweise in Mikroprozessoren, Speicherchips und Sensoren.

Vorteile der Umverteilungsschicht

Die RDL-Technologie bietet mehrere Vorteile für Entwickler, die leistungsstarke, kompakte und kostengünstige elektronische Geräte entwickeln möchten. Zu den Vorteilen der Verwendung der RDL-Technologie in IC-Gehäusen gehören:

Reduzierter Platzbedarf

Die RDL-Technologie ermöglicht die Integration mehrerer Chips in einem einzigen Gehäuse, wodurch die Gesamtgröße des Geräts reduziert wird. Dadurch können Entwickler kleinere und kompaktere elektronische Geräte entwerfen, was für Anwendungen wie Smartphones, Wearables und IoT-Geräte unerlässlich ist.

Verbesserte elektrische Leistung

Die RDL-Technologie ermöglicht es dem Entwickler, den Chip kompakt und effizient zu platzieren, wodurch die Länge der Verbindungen reduziert wird. Dies wiederum verringert die Signalverzögerung und verbessert die elektrische Leistung des Geräts. Die RDL-Technologie reduziert auch die parasitäre Kapazität und Induktivität, was die Signalintegrität des Geräts verbessert.

Reduzierte Kosten

Die RDL-Technologie macht Drahtbonding und Flip-Chip-Bonding überflüssig, beides kostspielige und zeitaufwendige Verfahren. Die RDL-Technologie reduziert außerdem die Anzahl der für das Gerät erforderlichen Komponenten, was die Kosten des Geräts weiter senkt. Die RDL-Technologie ist eine kostengünstige Lösung für die Herstellung von Hochleistungs-ICs, die einen kleinen Formfaktor erfordern.

Arten von Umverteilungsschicht-Technologie

Es gibt zwei Arten von Redistribution Layer (RDL)-Technologie: Fan-In und Fan-Out. Die Fan-In-RDL-Technologie wird für die Verpackung eines einzelnen Chips verwendet, während die Fan-Out-RDL-Technologie für die Verpackung mehrerer Chips eingesetzt wird.

Fan-in-RDL-Technologie

Die Fan-in-RDL-Technologie wird für die Verpackung eines einzelnen Chips verwendet. Die Fan-in-RDL-Technologie ist auch als Wafer-Level-Package (WLP) bekannt, bei dem es sich um einen Prozess handelt, bei dem ein Gehäuse direkt auf dem Wafer hergestellt wird. Die Fan-in-RDL-Technologie ist eine kostengünstige Lösung für die Herstellung kleiner und dünner Gehäuse.

Die Fan-in-RDL-Technologie eignet sich für Anwendungen wie Sensoren, MEMS-Bauteile, HF-Bauteile, Mikroprozessoren und Speicherbauteile.

Fan-Out-RDL-Technologie

Die Fan-Out-RDL-Technologie wird für die Verpackung mehrerer Chips verwendet. Die Fan-Out-RDL-Technologie ist auch als Wafer-Level-Fan-Out (WLFO) bekannt, ein Verfahren zur Herstellung einer Verpackung auf einem rekonstituierten Wafer. Die Fan-Out-RDL-Technologie ist eine kostengünstige Lösung für die Herstellung von Hochleistungspackagen mit kleinem Formfaktor.

Die Fan-Out-RDL-Technologie eignet sich für Anwendungen wie Grafikprozessoren, System-on-Chip (SoC), Speicherbausteine, Leistungsbauelemente und LED-Bauelemente.

Umverteilungsprozess

Die RDL-Technologie ist ein komplexer Prozess, der viele Schritte umfasst, darunter dielektrische Abscheidung, Metallabscheidung, Strukturierung und Ätzen. Nachfolgend finden Sie den Prozessablauf für Fan-in-RDL und Fan-out-RDL.

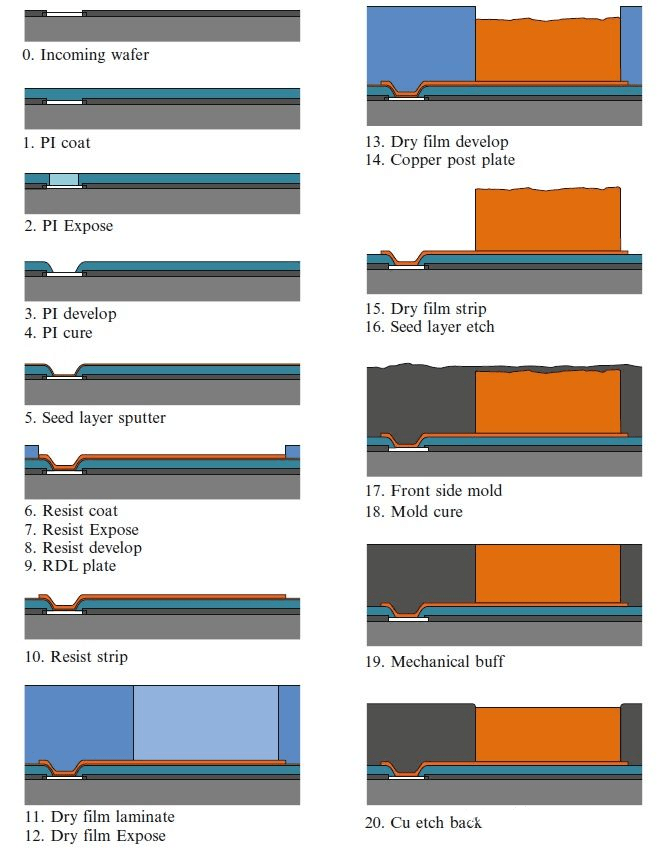

Fan-in-RDL-Prozess

Der Fan-in-RDL-Prozess wird bei der Herstellung fortschrittlicher Verpackungslösungen wie Wafer-Level Chip-Scale Packaging (WLCSP) und System-in-Package (SiP)-Designs eingesetzt. Er ermöglicht einen höheren Integrationsgrad, reduzierte Formfaktoren und eine verbesserte Leistung für Halbleiterbauelemente. Der Prozess umfasst mehrere Schritte, wie unten aufgeführt:

Der Prozess beginnt mit einem eingehenden Wafer, der dann in Schritt 1 mit PI (Photoresist Insulator) beschichtet wird. Darauf folgt die PI-Belichtung in Schritt 2, die PI-Entwicklung in Schritt 3 und die PI-Aushärtung in Schritt 4.

In Schritt 5 wird eine Grundschicht auf den Wafer gesputtert, der dann in Schritt 6 mit Resist beschichtet wird. Der Resist wird dann in Schritt 7 belichtet, in Schritt 8 entwickelt und in Schritt 9 wird das RDL plattiert.

Danach wird der Resist in Schritt 10 entfernt und in Schritt 11 eine Trockenfolie auf den Wafer laminiert. Die Trockenfolie wird dann in Schritt 12 belichtet und in Schritt 13 entwickelt. Als Nächstes werden in Schritt 14 Kupferpfosten auf den Wafer plattiert und in Schritt 15 die Trockenfolie entfernt.

In Schritt 16 wird die Keimschicht geätzt und in Schritt 17 wird eine Vorderseitenform erstellt. Die Form wird dann in Schritt 18 ausgehärtet und der Wafer wird in Schritt 19 mechanisch poliert. Schließlich wird in Schritt 20 das überschüssige Kupfer zurückgeätzt, wodurch der Fan-in-RDL-Prozessablauf abgeschlossen wird.

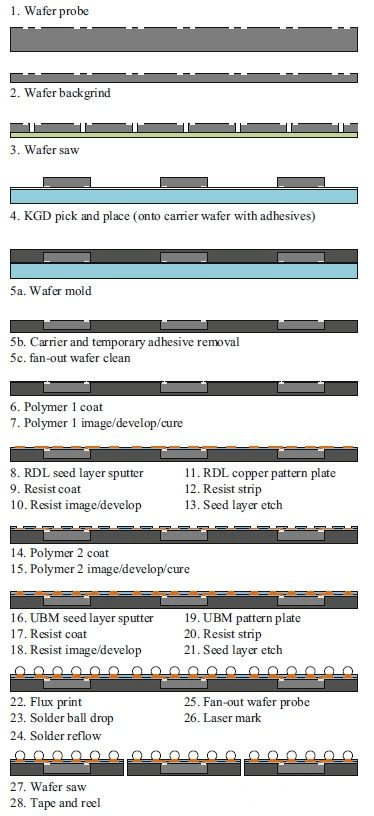

Fan-Out-RDL-Prozess

Ähnlich wie beim Fan-in-RDL-Verfahren ist auch das Fan-out-RDL-Verfahren eine Möglichkeit, kleinere, leistungsstärkere Chip-Gehäuse mit mehr Verbindungen herzustellen. Hier sind die Herstellungsschritte:

1. Wafer-Prüfung: Hierbei handelt es sich um die erste Prüfung des Wafers, um sicherzustellen, dass er die erforderlichen Spezifikationen erfüllt, bevor mit den nachfolgenden Verarbeitungsschritten fortgefahren wird.

2. Wafer-Rückseitenschliff: Die Rückseite des Wafers wird auf eine bestimmte Dicke geschliffen, um die Dicke des Gehäuses zu reduzieren.

3. Wafer-Säge: Der Wafer wird in einzelne Chips geschnitten.

4. KGD (Known Good Die) Pick and Place: Die guten Dies werden aufgenommen und mit Klebstoff auf einen Trägerwafer übertragen.

5a. Wafer-Form: Der Wafer mit den auf dem Trägerwafer befestigten Dies wird mit einem dielektrischen Material geformt, um eine Fan-Out-Struktur zu bilden.

5b. Entfernen des Trägers und des temporären Klebstoffs: Der Trägerwafer wird vom Fan-Out-Wafer entfernt, und auch der während des Prozesses verwendete temporäre Klebstoff wird entfernt.

5c. Reinigung des Fan-Out-Wafers: Der Fan-Out-Wafer wird gereinigt, um verbleibende Partikel oder Verunreinigungen zu entfernen.

6. Polymer 1-Beschichtung: Eine Polymerschicht wird auf die Oberfläche des Fan-Out-Wafers aufgetragen, um als dielektrische Schicht zu dienen.

7. Polymer 1 belichten/entwickeln/aushärten: Die Polymerschicht wird mittels Fotolithografie strukturiert, um die gewünschte Form und Größe der RDL-Struktur zu erzielen.

8. RDL-Keimschicht-Sputtern: Eine dünne Schicht aus Kupfer oder einem anderen leitfähigen Material wird mittels Sputtern auf die Polymerschicht aufgebracht.

9. Resistbeschichtung: Eine Schicht aus Resistmaterial wird auf die Seed-Schicht aufgetragen.

10. Resist-Bild/Entwicklung: Die Resistschicht wird mittels Fotolithografie strukturiert, um die gewünschte Form und Größe der RDL-Struktur zu erzielen.

11. RDL-Kupfermusterplatte: Kupfer wird mittels Galvanisierung auf die freiliegenden Bereiche der Grundierungsschicht aufgebracht, wodurch das gewünschte RDL-Muster entsteht.

12. Resist-Streifen: Das verbleibende Resistmaterial wird entfernt, sodass nur das Kupfer-RDL-Muster übrig bleibt.

13. Ätzen der Seed-Schicht: Der nicht benötigte Teil der Seed-Schicht wird durch Ätzen entfernt.

14. Polymer 2-Beschichtung: Eine weitere Polymerschicht wird auf die RDL-Struktur aufgebracht, um als dielektrische Schicht zu dienen.

15. Polymer 2 belichten/entwickeln/aushärten: Die Polymerschicht wird mittels Fotolithografie strukturiert, um die gewünschte Form und Größe der UBM-Struktur zu erzielen.

16. Sputtern der UBM-Seed-Schicht: Eine dünne Schicht aus Kupfer oder einem anderen leitfähigen Material wird mittels Sputtern auf die Polymerschicht aufgebracht.

17. Resistbeschichtung: Eine Schicht aus Resistmaterial wird auf die Keimschicht aufgetragen.

18. Resist-Bild/Entwicklung: Die Resistschicht wird mittels Fotolithografie strukturiert, um die gewünschte Form und Größe der UBM-Struktur zu erzielen.

19. UBM-Musterplatte: Auf die freiliegenden Bereiche der Grundierungsschicht wird mittels Galvanisierung Kupfer aufgebracht, wodurch das gewünschte UBM-Muster entsteht.

20. Resist-Streifen: Das verbleibende Resistmaterial wird entfernt, sodass nur das Kupfer-UBM-Muster übrig bleibt.

21. Ätzen der Keimschicht: Der nicht benötigte Teil der Keimschicht wird durch Ätzen entfernt.

22. Flussmittelaufdruck: Ein Flussmittel wird auf die UBM-Pads aufgetragen.

23. Aufbringen der Lötkugeln: Lötkugeln werden auf die UBM-Pads aufgebracht.

24. Reflow-Löten: Die Lötkugeln werden erhitzt, um sie zum Schmelzen zu bringen und Verbindungen zwischen den UBM-Pads und externen Anschlüssen oder Bumps herzustellen.

25. Fan-out-Wafer-Prüfung: Der verpackte IC wird getestet, um sicherzustellen, dass er die erforderlichen Spezifikationen erfüllt.

26. Lasermarkierung: Mit einem Laser wird eine eindeutige Kennung oder ein Barcode auf die Oberfläche des ICs geätzt.

27. Wafer-Säge: Der Fan-Out-Wafer wird in einzelne Gehäuse geschnitten.

28. Band und Rolle: Die einzelnen verpackten ICs werden zur einfachen Handhabung und zum Versand auf einer Rolle befestigt.

RDL auf fortschrittliche Verpackungen anwenden

Bei fortschrittlichen Verpackungen wie Fan-In-Wafer-Level-Package (FIWLP) und Fan-Out-Wafer-Level-Package (FOWLP) ist RDL die wichtigste Technologie. Der Aufstieg dieser Technologie hat es Verpackungsbetrieben ermöglicht, mit Wafer-Foundries im Bereich der Fan-Out-Verpackungstechnologie zu konkurrieren. Durch RDL kann IOPad zu verschiedenen Arten von Wafer-Level-Packages in FIWLP oder FOWLP verarbeitet werden. Bei FIWLP werden alle Bumps auf dem Chip gewachsen, und die Verbindung zwischen dem Chip und dem Pad hängt hauptsächlich von der Metallleitung des RDL ab. Nach der Verpackung hat der IC fast die gleiche Größe wie die Chipfläche. Bei FOWLP können Bumps außerhalb des Chips wachsen, und der IC ist nach der Verpackung größer als die Chipfläche (1,2-fach).

Insbesondere bei der fortschrittlichen 2,5D-Verpackung ist neben dem TSV auf dem Siliziumsubstrat auch RDL unverzichtbar. Am Beispiel von TSMCs InFO, einem Vertreter der fortschrittlichen 2,5D-Verpackung, verwendet InFO einen oder mehrere unbeschichtete Chips auf dem Träger, die dann in den rekonstituierten Wafer der Formmasse eingebettet werden. Anschließend werden RDL-Verbindungen und dielektrische Schichten auf dem Wafer hergestellt, was einem „Chip-First”-Prozessablauf entspricht. Single-Die-InFO bietet eine hohe Anzahl an Bumps, und die RDL-Leitungen erstrecken sich vom Chipbereich nach außen und bilden eine „Fan-Out”-Topologie.

Welche Umverteilungsschicht-Technologie sollte ich verwenden?

Wie bereits erwähnt, gibt es zwei RDL-Technologien: Fan-in-RDL und Fan-out-RDL. Wie wählt man also die richtige Technologie aus, um leistungsstarke, kompakte und kostengünstige elektronische Geräte zu entwickeln? Dies hängt von mehreren Faktoren ab, wie beispielsweise der Art der Anwendung, der Anzahl der Chips und den Leistungsanforderungen.

Anwendung

Die Fan-In-RDL-Technologie eignet sich für Anwendungen wie Sensoren, MEMS-Bauteile und HF-Bauteile. Die Fan-Out-RDL-Technologie eignet sich für Anwendungen wie Grafikprozessoren, System-on-Chip (SoC) und Speicherbauteile.

Anzahl der Matrizen

Die Fan-In-RDL-Technologie eignet sich für die Verpackung eines einzelnen Chips, während die Fan-Out-RDL-Technologie für die Verpackung mehrerer Chips geeignet ist.

Leistungsanforderungen

Die Fan-In-RDL-Technologie eignet sich für die Herstellung kleiner und dünner Gehäuse, während die Fan-Out-RDL-Technologie für die Herstellung von Hochleistungsgehäusen mit kleinem Formfaktor geeignet ist.

Vergleich von RDL mit anderen IC-Verpackungstechnologien

Aufgrund unterschiedlicher Verfahren stehen für integrierte Schaltkreise mehrere Verpackungstechnologien zur Verfügung. Weitere Informationen zu deren Unterschieden finden Sie in der folgenden Tabelle:

| IC Packaging | Description | Advantages | Disadvantages | Applications |

|---|---|---|---|---|

| Wire Bonding | Connecting the IC to the PCB using wires | Low cost, flexible, proven technology | Limited performance, not suitable for high-frequency and high-power applications | Consumer electronics, automotive, medical devices |

| Flip-Chip Bonding | Chips are bonded face-down to the substrate, Connecting the IC to the PCB using solder bumps | High performance, high-density, low inductance | Expensive, requires precise alignment and underfilling | High-speed data communication, high-power applications, microprocessors |

| Through-Silicon Via (TSV) | Creating vertical interconnects through the silicon substrate | Shorter interconnect lengths, higher performance, smaller form factor | Complex and expensive manufacturing process, thermal and mechanical stress issues | Memory devices, image sensors, 3D ICs |

| Chip-scale package (CSP) | Replacing the lead frame with a substrate | Small form factor, high density, low cost | Limited I/O, susceptibility to mechanical and thermal stress | Mobile devices, wearable technology |

| Integrated Fan-out (InFO) | Integrated package of multiple chips and the soldering point of the pin is outside of the chip | High density, small form factor, low power consumption | Complex manufacturing process, high cost | Mobile devices, IoT, wearable technology |

| High Bandwidth Memory (HBM) | 3D stacking technology | High bandwidth, low power consumption | Expensive, limited scalability | High-performance computing, graphics processing |

| Chip on Wafer on Substrate (CoWoS) | Integrate chip and silicon wafer (substrate) together | High bandwidth, low power consumption, heterogeneous integration | Complex manufacturing process, high cost | High-performance computing, graphics processing |

| Redistribution Layer (RDL) | Creating a patterned metal layer on top of the dielectric layer | High density, fine pitch, low profile | Limited power handling capability, susceptibility to mechanical and thermal stress | Mobile devices, consumer electronics |

| Bump Technology | Depositing small metal bumps on the chip | Low cost, simple manufacturing process, flexible design | Limited performance, not suitable for high-speed and high-power applications | Consumer electronics, automotive, medical devices |

Unternehmen, die Lösungen für Redistribution-Layer-Technologie anbieten

Es gibt mehrere Unternehmen, die Lösungen für die Redistribution Layer (RDL)-Technologie anbieten, darunter:

ASE-Gruppe

Die ASE Group ist ein globaler Anbieter von Halbleiterfertigungsdienstleistungen. Die ASE Group bietet eine breite Palette an RDL-Technologielösungen für verschiedene Anwendungen wie Speicher, Mikroprozessoren und Grafikprozessoren.

Amkor Technology

Amkor Technology ist ein globaler Anbieter von Halbleiterverpackungs- und Testdienstleistungen. Amkor Technology bietet eine breite Palette an RDL-Technologielösungen für verschiedene Anwendungen wie Sensoren, MEMS-Geräte und Leistungsgeräte.

Taiwan Semiconductor Manufacturing Company

TSMC ist ein weltweit tätiger Halbleiterhersteller, der eine breite Palette an RDL-Technologielösungen für verschiedene Anwendungen wie System-on-Chip (SoC), Speicherbausteine und Leistungsbauelemente anbietet.

Fazit

Die Redistribution Layer (RDL)-Technologie ist eine revolutionäre Verpackungslösung, die die Art und Weise, wie wir integrierte Schaltkreise (ICs) verpacken, verändert hat. Sie ermöglicht mehr Verbindungen auf einem einzigen Chip und reduziert so die Gesamtfläche des Geräts. Daher wird sie in verschiedenen Anwendungen wie Smartphones, Wearables und IoT-Geräten eingesetzt. Die Zukunft der RDL-Technologie in IC-Gehäusen ist vielversprechend, und es wird erwartet, dass sie in den kommenden Jahren einen erheblichen Einfluss auf die Elektronikindustrie haben wird.