Débogueurs matériels intégrés : outils et conseils

Déboguez les systèmes embarqués avec JTAG, SWD et des analyseurs logiques. Apprenez la configuration, le dépannage et la compatibilité avec STM32/Arduino. Guide indispensable pour les ingénieurs !

De schémas et de restauration de Gerber

MCU/CPLD code de la restauration de l'accès et de sauvegarde

1:1 exacte du matériel de réplication

BLE & Classique BT solutions sans fil

Précision PID & gestion thermique

Haute efficacité de moteur de contrôle

Industrielle RS485/RTU de la communication

Personnalisé STM32/ESP32 firmware & HW

L'optimisation de coûts et de rendement

Multi-couches à haute vitesse numérique, mise en page

Rapide tour d'échantillons à des fins de vérification

Clé en main PCBA & de l'approvisionnement en composants

L'expertise de la technologie de montage en Surface

Trouver les causes de la puce défauts

Au niveau du composant conseil d'administration de la restauration

Thermique et électrique des tests de stress

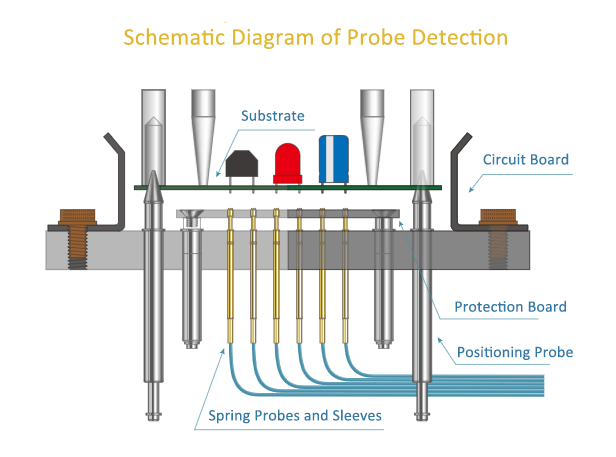

Découvrez le génie derrière la précision des microsondes

Calculer le PCB largeur de trace basé sur l'élévation de température, de courant et d'épaisseur de cuivre (IPC-2152).

La rétro-ingénierie des circuits intégrés est un processus sophistiqué d'analyse de la conception matérielle et de récupération des micrologiciels. Elle implique l'étude détaillée des circuits intégrés ou des microcontrôleurs afin de comprendre leur architecture, leur logique et les micrologiciels intégrés. Ce service professionnel est essentiel pour la maintenance des systèmes hérités, l'analyse matérielle et la recherche sur l'interopérabilité, car il permet aux ingénieurs de récupérer des données critiques à partir de composants anciens ou non pris en charge.

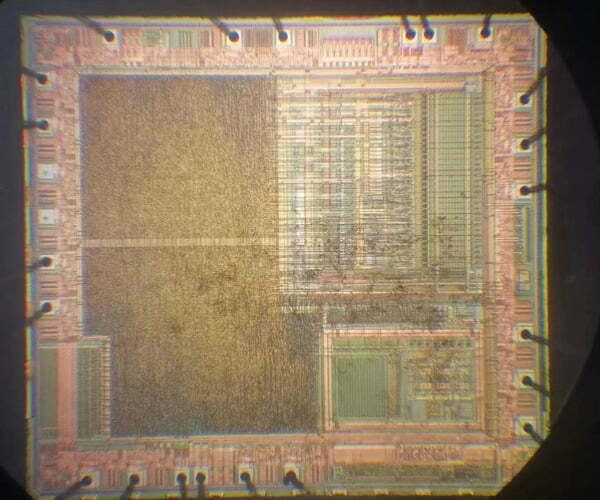

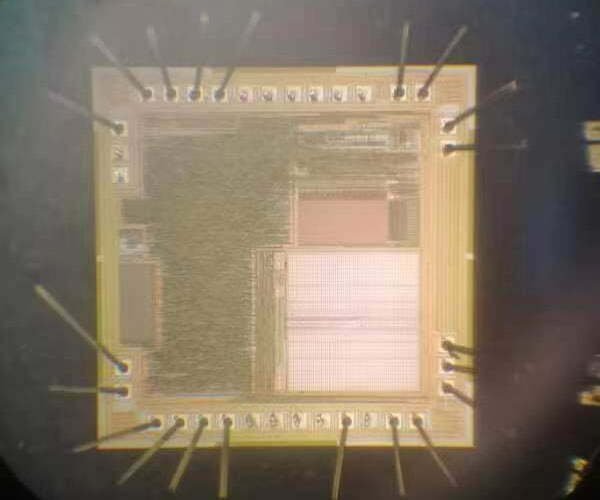

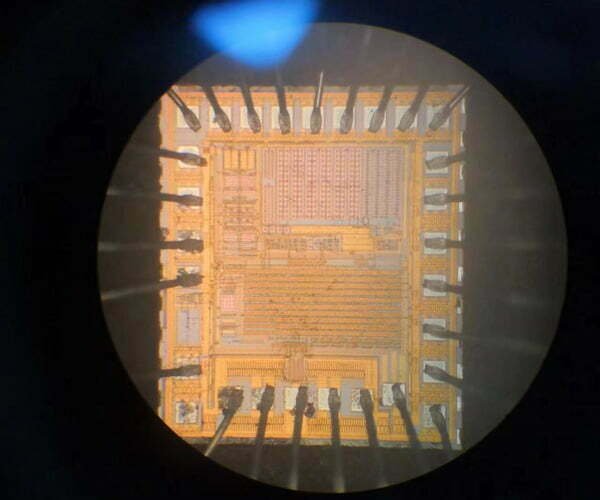

Délaminage des circuits par gravure chimique ou polissage mécanique.

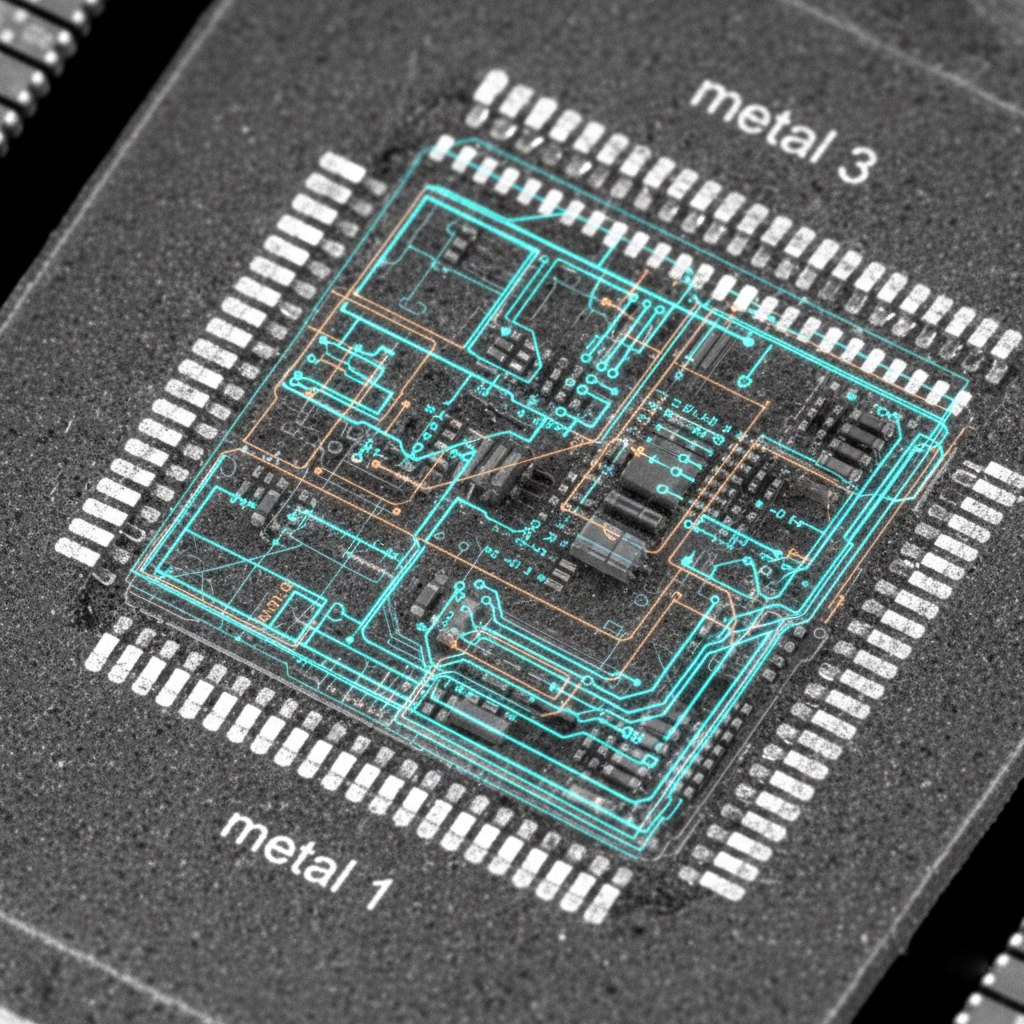

Utilisation d'images SEM haute résolution pour extraire la connectivité au niveau des transistors.

« Il ne s'agit pas seulement d'une duplication, mais d'un outil essentiel pour une compréhension approfondie des nœuds avancés et la protection des brevets. »

Avec plus de 15 ans d'expérience, nous avons réalisé plus de 1 000 projets d'analyse matérielle et de récupération de micrologiciels. Nos clients vont des start-ups innovantes aux entreprises mondiales dans des secteurs tels que l'automobile, l'aérospatiale, l'automatisation industrielle, les dispositifs médicaux et les télécommunications. Nous sommes le partenaire privilégié des entreprises qui ont besoin d'une connaissance approfondie du matériel et d'une assistance pour les systèmes hérités. Pour plus de modèles de circuits intégrés, veuillez nous contacter directement.

Nos méthodologies professionnelles pour l'analyse des puces et la récupération des données.

Nous utilisons une analyse avancée des protocoles pour identifier les séquences logiques au sein du micrologiciel. En analysant les délais d'exécution et les séquences d'effacement dans les architectures héritées telles que la série ATMEL AT89C, nous identifions les états dans lesquels la mémoire devient accessible. Notre équipe cartographie les structures du micrologiciel en détectant des modèles de données, tels que les séquences hexadécimales FFFF, garantissant ainsi une récupération ou une migration réussie vers des plateformes matérielles modernes.

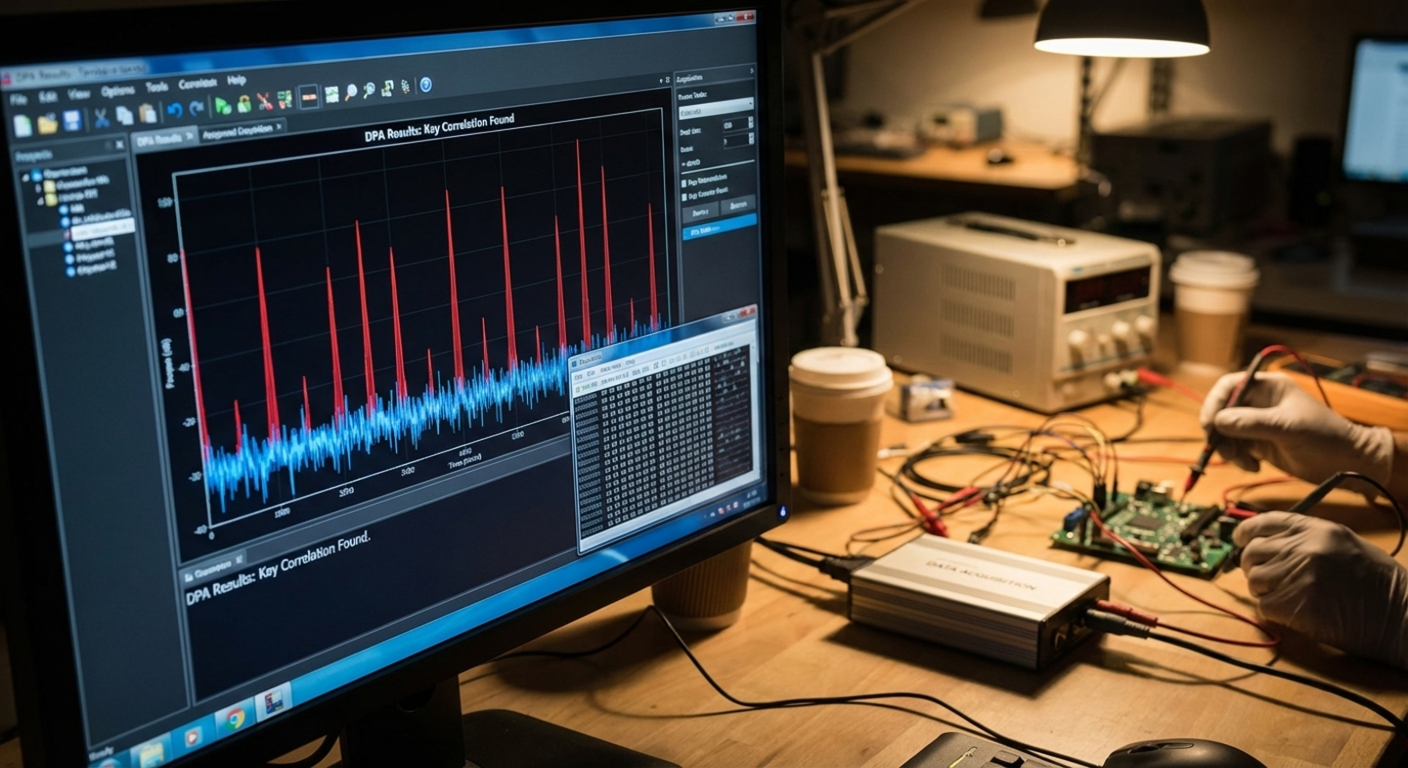

Cette technique non invasive surveille la consommation d'énergie et les émissions électromagnétiques pendant le fonctionnement de la puce. En appliquant des modèles statistiques avancés, nous pouvons déduire les états logiques et les modèles d'exécution sans intrusion physique. Cette méthodologie est essentielle pour comprendre le fonctionnement interne des appareils et les processus cryptographiques, car elle permet d'examiner en profondeur le comportement fonctionnel et le flux de données de la puce.

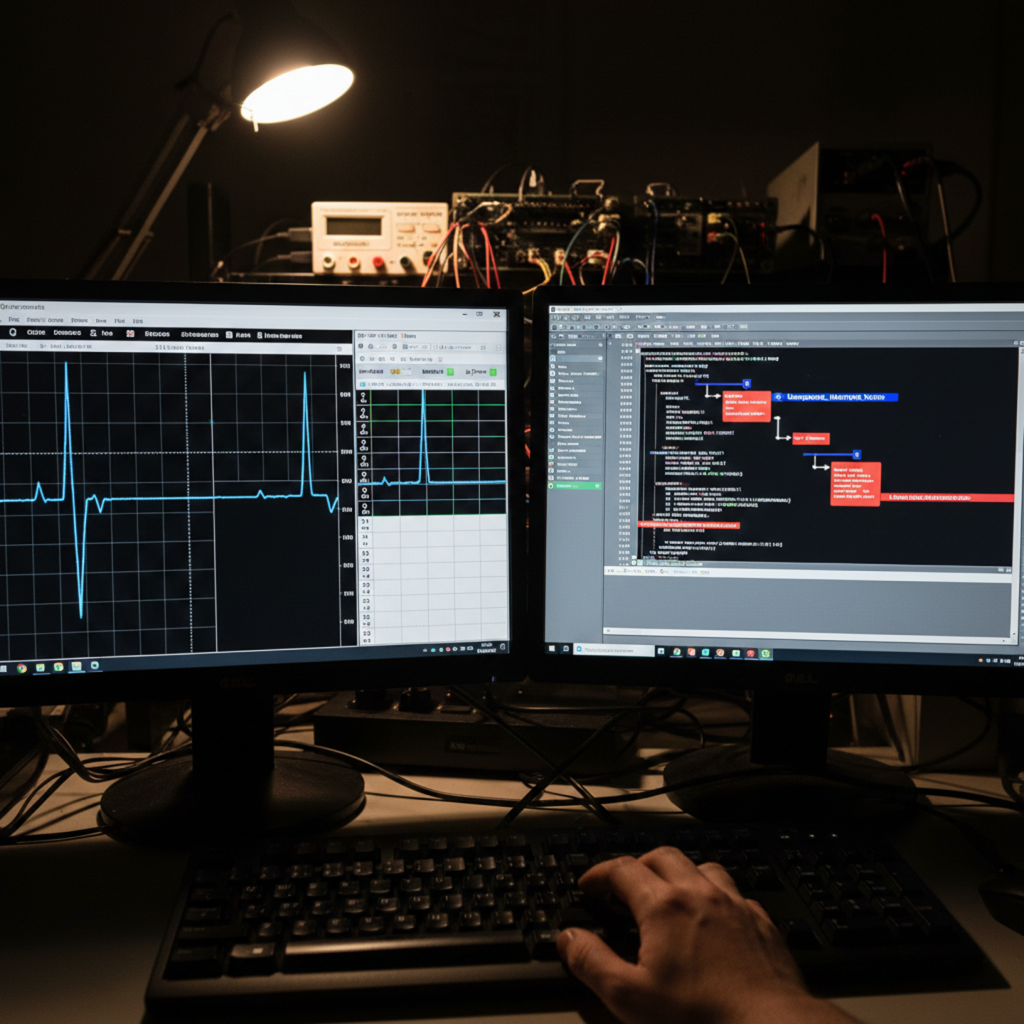

En appliquant des perturbations de tension contrôlées ou des transitoires d'horloge, nous analysons le comportement du processeur dans des conditions de fonctionnement anormales. Cette méthodologie de stress aide à identifier les vulnérabilités cachées de la conception et à améliorer la robustesse globale du système. Elle permet aux ingénieurs de repérer les points de défaillance critiques et de reconstruire la logique de flux de contrôle qui n'apparaît que lors de fluctuations environnementales spécifiques ou d'exceptions matérielles.

À l'aide de stations de test submicroniques de haute précision, nous extrayons les signaux directement à partir du câblage métallique interne du circuit intégré. Cette approche physique permet une vérification fonctionnelle en temps réel et une cartographie précise des chemins de données. En contournant les broches de sécurité externes et en nous connectant directement au bus interne, nous pouvons observer l'exécution des instructions et l'état des registres, qui sont autrement invisibles pour les outils de débogage externes.

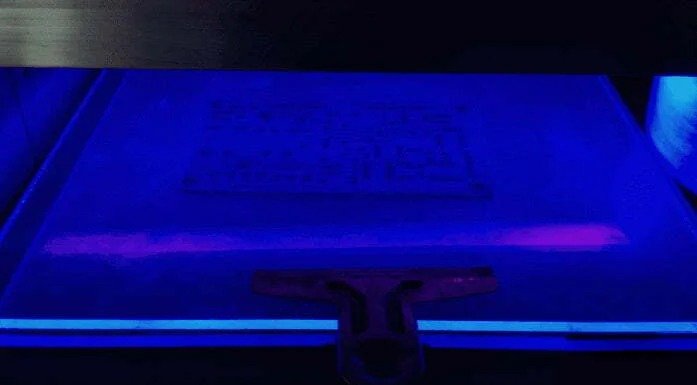

Des méthodes spécialisées d'irradiation UV sont utilisées pour analyser les structures de mémoire programmables une seule fois (OTP). Cette technique permet de récupérer des données pour la migration de systèmes hérités en manipulant les charges de la grille flottante. Il s'agit d'un service essentiel pour restaurer les micrologiciels à partir de puces industrielles discontinues dont le code d'origine a été perdu, offrant ainsi un moyen fiable de maintenir les infrastructures critiques et le matériel hérité.

Nous exploitons les caractéristiques de conception architecturale pour une récupération avancée des données. En identifiant des indicateurs matériels spécifiques ou des bascules logiques (FF) dans la structure de la mémoire, nous évaluons l'état de la puce pour une extraction précise du micrologiciel. Cette méthodologie est très efficace pour la série ATMEL 51 (AT89C51), où l'analyse au niveau des octets permet aux ingénieurs de restaurer l'accès au code critique perdu en raison de l'obsolescence du matériel.

La technologie FIB (Focused Ion Beam) est notre méthode privilégiée pour la restauration précise des circuits. Après décapsulation chimique, nous utilisons la microscopie électronique pour modifier les chemins logiques internes à l'échelle nanométrique. Cette technique est idéale pour les projets de la série TI MSP430 (MSP430F1101A, F149, F425) impliquant des fusibles de sécurité. En restaurant les états des circuits, nous permettons la récupération du micrologiciel à partir d'appareils protégés lorsque le code source d'origine n'est pas disponible.

Pour les puces CPLD et DSP hautement complexes, nous effectuons une analyse structurelle approfondie afin de contourner les portes logiques non fonctionnelles et de rétablir l'accès aux données du système central. Ce processus implique la reconstruction de listes de réseaux complexes et l'identification de chemins de signaux cachés dans la structure en silicium. Il est particulièrement efficace pour la série TMS320, permettant aux chercheurs de récupérer des algorithmes de traitement propriétaires à des fins de R&D.

Le décapsulage simple prend 1 à 3 jours. L'extraction complète de la liste d'interconnexions peut prendre de 2 à 12 semaines, selon la complexité de la puce et la taille des nœuds.

Les coûts varient considérablement. Une analyse structurelle de base peut coûter à partir de 5 000 dollars, tandis que l'extraction complète des circuits pour les nœuds avancés peut coûter entre 50 000 et plus de 200 000 dollars.

Oui, nous disposons de techniques spécialisées pour lire les mémoires non volatiles (Flash/EEPROM), mais leur efficacité dépend des fusibles de sécurité et du cryptage utilisés.

Déboguez les systèmes embarqués avec JTAG, SWD et des analyseurs logiques. Apprenez la configuration, le dépannage et la compatibilité avec STM32/Arduino. Guide indispensable pour les ingénieurs !

L'informatique optique se développe rapidement dans le domaine de l'IA et offre de larges perspectives d'application. Récemment, l'équipe de recherche sur les semi-conducteurs de l'Académie

Une puce à circuit intégré qui intègre une unité centrale de traitement (CPU), une mémoire vive (RAM), une mémoire morte (ROM), des ports d'entrée/sortie et