Das STM32F103C8T6-Core-Board basiert auf dem offiziellen ST STM32F103C8T6-Mikrocontroller-Chip. Dieses kompakte und vielseitige Board wurde sorgfältig entwickelt, um eine minimale Systemkonfiguration zu schaffen, wodurch es sich ideal für verschiedene Embedded-System-Projekte eignet. Es bietet eine Reihe wichtiger Komponenten, darunter Schaltungen für die Auswahl des BOOT-Modus, Entkopplung, Quarzoszillator, SWD-Download, Reset-Funktionalität, Stromanzeige und Peripherie-IO-Port-Schnittstellen. Dank ihres durchdachten Designs lässt sich die Platine leicht integrieren und für die Verwendung mit anderen Basisplatinen erweitern. Ihre Energieeffizienz und robusten Funktionen machen sie zu einem wertvollen Werkzeug für Entwickler, mit dem sie innovative Anwendungen auf der STM32F103C8T6-Plattform erstellen und testen können.

STM32F103C8T6 Projektbeschreibung

Dieses Projekt verwendet den offiziellen ST STM32F103C8T6-Chip und entwickelt eine minimale Systemplatine, die leicht erweitert und mit der Basisplatine verwendet werden kann.

- Zu den entworfenen Schaltungen gehören eine BOOT-Schaltung, eine Entkopplungsschaltung, eine Quarzoszillatorschaltung, eine SWD-Download-Schaltung, eine Reset-Schaltung, eine Betriebsanzeigeschaltung und eine periphere IO-Port-Schaltung.

- Die Platine wird über externe Anschlüsse an den +3V3-Pin und den GND-Pin mit Strom versorgt. Es wird empfohlen, die Platine im Bereich von 3,3 V bis 3,6 V zu betreiben, wobei eine Versorgungsspannung von 3,6 V nicht überschritten werden sollte.

- Eine +3V3-Stromanzeigeschaltung zeigt auf praktische Weise an, ob die Stromversorgung normal ist.

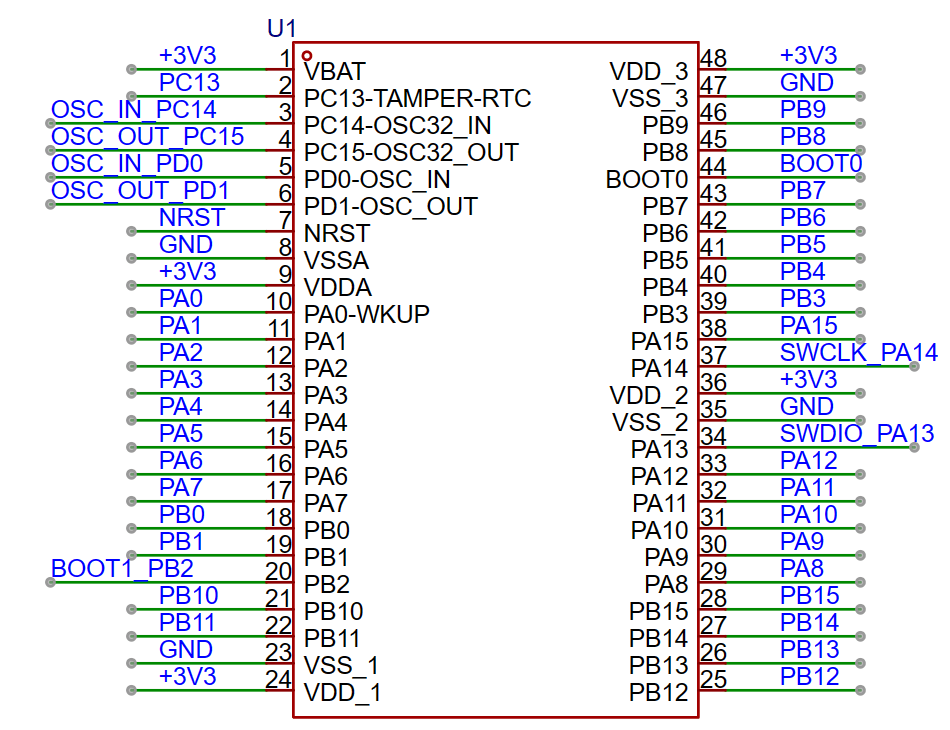

STM32F103C8T6 Pinbelegung

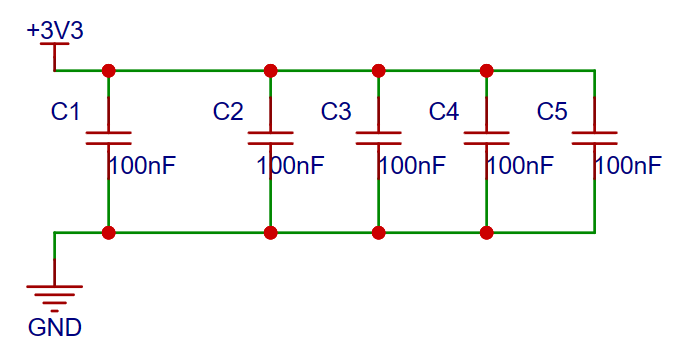

Entkopplungsschaltung

Schematische Darstellung

Durch Anbringen eines Kondensators mit 104 (0,1 μF) an den Stromversorgungsstiften wird das Rauschen der Stromversorgung wirksam unterdrückt, was als Entkopplung des Stromversorgungsrauschens bezeichnet wird.

Je näher die Punkte „Stromversorgung – Entkopplungskondensator – Masse“ beieinander liegen, desto besser ist der Entkopplungseffekt.

Bei Kondensatoren aus dem gleichen Material ändert sich der Entkopplungseffekt auch dann nicht wesentlich, wenn die Kapazität auf 1/10 sinkt. Bei der Hochfrequenzentkopplung zeigen Kondensatoren mit dem gleichen Gehäuse und Kapazitätswerten von 0,01 μF, 0,1 μF und 1 μF ähnliche Ergebnisse.

Oberflächenmontierte (SMD) Kondensatoren haben aufgrund der größeren äquivalenten Induktivität der Durchsteckkondensatoren, die den Entkopplungseffekt beeinflusst, einen besseren Entkopplungseffekt als Durchsteckkondensatoren mit derselben Kapazität.

Der Kondensator mit der geringsten Kapazität hat die höchste Resonanzfrequenz und den kleinsten Entkopplungsradius. Daher sollte er am nächsten zum Chip platziert werden.

Kondensatoren mit etwas größerer Kapazität können etwas weiter entfernt platziert werden, und die größte Kapazität sollte auf der äußersten Schicht platziert werden. Alle Kondensatoren zur Entkopplung dieses Chips sollten jedoch so nah wie möglich am Chip platziert werden.

Bei Hochgeschwindigkeits-Leiterplattenkonstruktionen ist es besser, Kondensatoren auf derselben Seite wie der Chip zu platzieren, um eine bessere Entkopplung zu erzielen. Bei MCU-Typ-Entkopplungskondensatoren gibt es keinen wesentlichen Unterschied zwischen der Platzierung auf der Vorder- oder Rückseite.

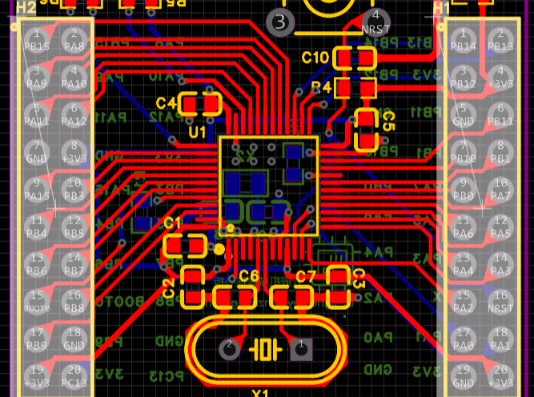

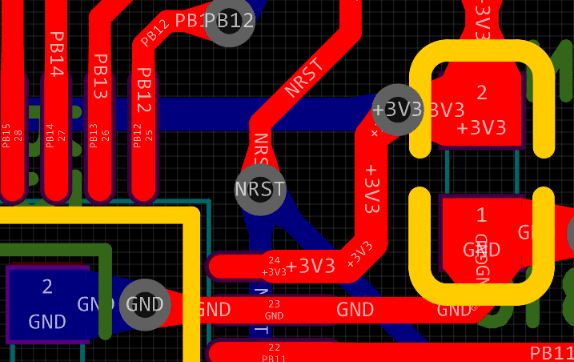

PCB-Design

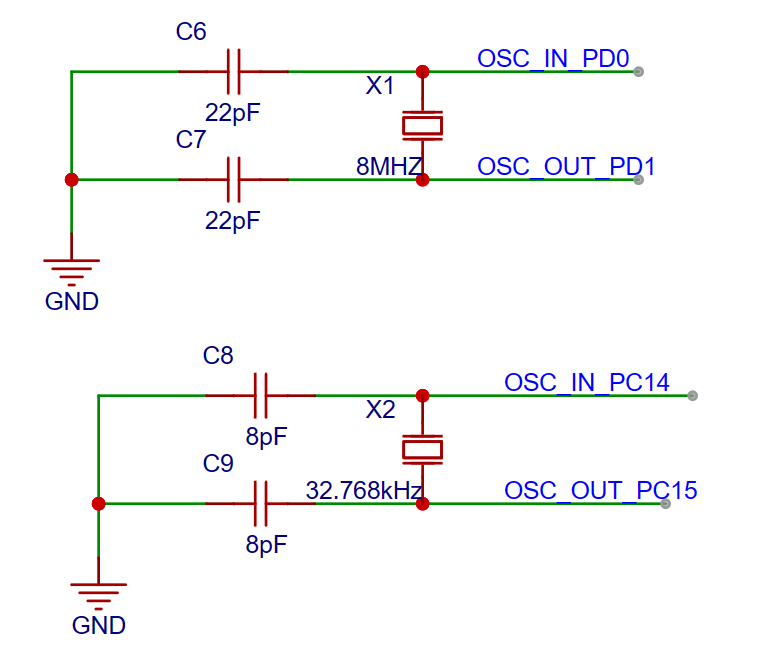

Quarzoszillatorschaltung

Schematische Darstellung

Der STM32 verfügt über drei interne Taktquellen, aber der Taktbaum des 32-Bit-Chips benötigt fünf Taktquellen. Daher muss die Leiterplatte externe Hochgeschwindigkeits- und Niedriggeschwindigkeitstakte aufnehmen können.

Der externe Hochgeschwindigkeits-Taktgeber kann ein Quarz-/Keramikresonator oder eine externe Taktquelle mit einem Frequenzbereich von 4 MHz bis 16 MHz sein. Eine gängige Wahl ist ein 8-MHz-Quarzoszillator für die Hauptsystemfrequenz.

Der externe Niedriggeschwindigkeits-Taktgeber ist ein Quarz mit einer Frequenz von 32,768 kHz, der zum Ansteuern der RTC-Uhr verwendet wird.

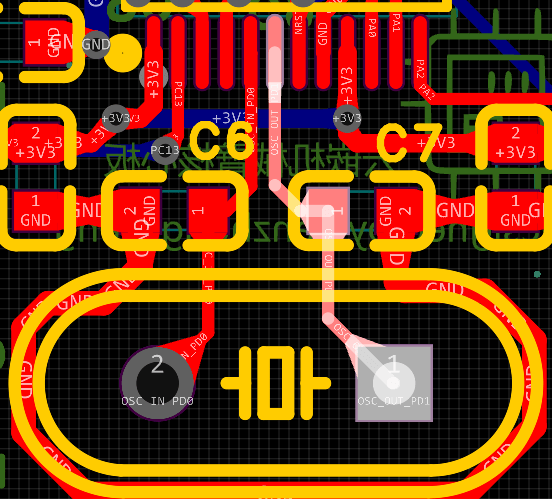

PCB-Design

Beachten Sie, dass der Bereich um den Quarzoszillator von GND-Leiterbahnen umgeben ist und es ratsam ist, auf diesen GND-Leiterbahnen Durchkontaktierungen anzubringen. Dies dient dazu, den Quarzoszillator zu isolieren. Vermeiden Sie außerdem Leiterbahnen auf der Ober- und Unterseite des Bereichs, in dem sich der Quarzoszillator befindet, da dies die Signalintegrität beeinträchtigen kann.

Darüber hinaus sollten die beiden Kondensatoren in der Nähe des Quarzoszillators symmetrisch angeordnet werden.

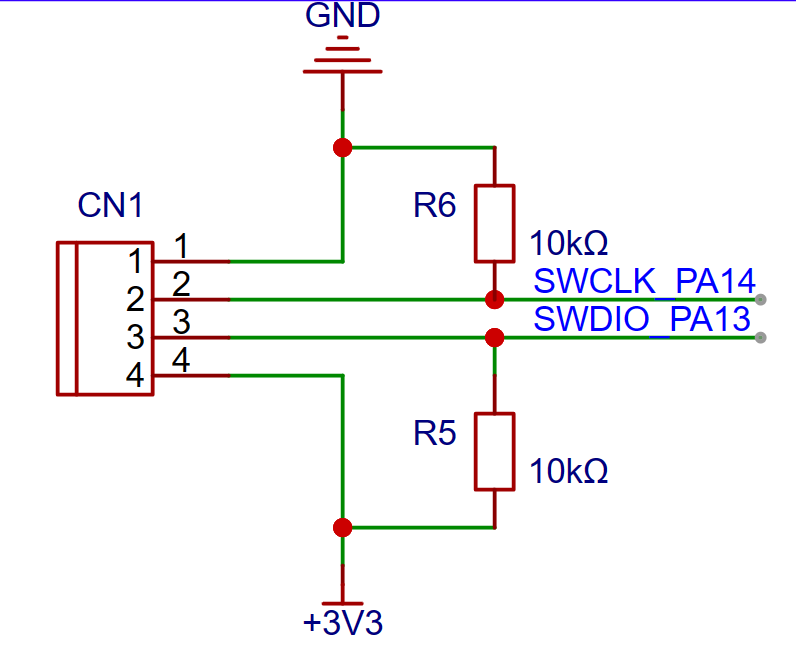

SWD-Download-Schaltung

Schematische Darstellung

Einführung in JTAG:

Wir verwenden üblicherweise den Jlink-Downloader, der jedoch den Nachteil hat, dass er die Jtag-20-PIN-Schnittstelle nutzt. Die übermäßige Anzahl an Pins kann zu Platzmangel auf kleinen Leiterplatten führen und die Komplexität der Verdrahtung erhöhen.

Die Verwendung der SWD-Schnittstelle zum Herunterladen und Debuggen erfordert nur 4 Pins: GND, RST, SWDIO, SWDCLK. Die Download-Geschwindigkeit kann bis zu 10 M/s erreichen, was klare Vorteile bietet.

SWD-Modus:

Der SWD-Modus ist in Hochgeschwindigkeitsszenarien zuverlässiger als JTAG. Bei großen Datenmengen kann der JTAG-Programm-Download häufiger fehlschlagen als bei SWD, das eine geringere Fehlerquote aufweist. Wenn Ihr Emulator den JTAG-Simulationsmodus unterstützt, können Sie in der Regel direkt den SWD-Modus verwenden, sofern dieser unterstützt wird.

PCB-Design

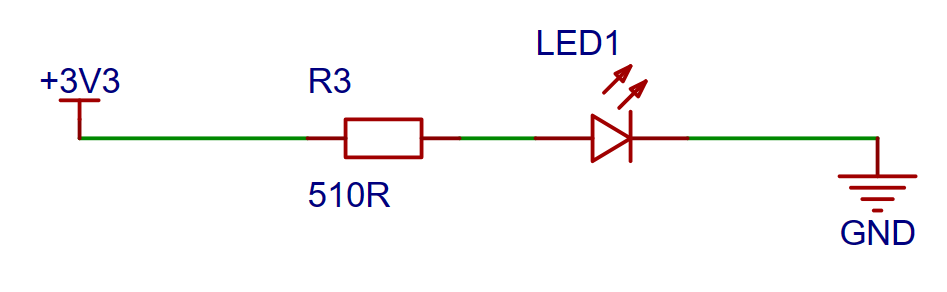

Leistungsanzeigeschaltung

Schematische Darstellung

Laut Datenblatt beträgt der maximale Vorwärtsspannungsabfall 2,4 V, wobei der typische Wert bei 2,1 V liegt. Wenn die LED also normal funktioniert, beträgt der maximale Spannungsabfall über der LED 2,4 V. In diesem Fall beträgt die Spannungsaufteilung über R3 0,9 V.

Normalerweise leuchten LEDs bei Strömen zwischen 3 mA und 10 mA. Der maximale Nennstrom beträgt 20 mA. Innerhalb des Nennstroms gilt: Je höher der durch die LED fließende Strom, desto heller leuchtet sie.

Hier wählen wir I = 10 mA, also R3 = U / I = 0,9 V / 10 mA = 90 Ω. Da 100-Ω-Widerstände in unseren Materialien häufiger vorkommen, können wir stattdessen einen 100-Ω-Widerstand verwenden.

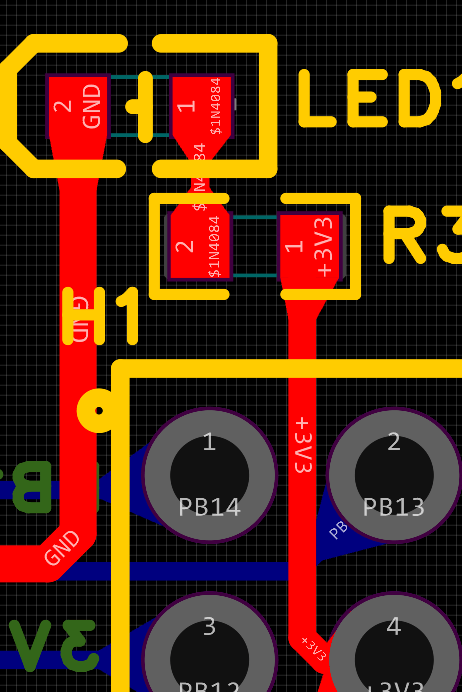

PCB-Design

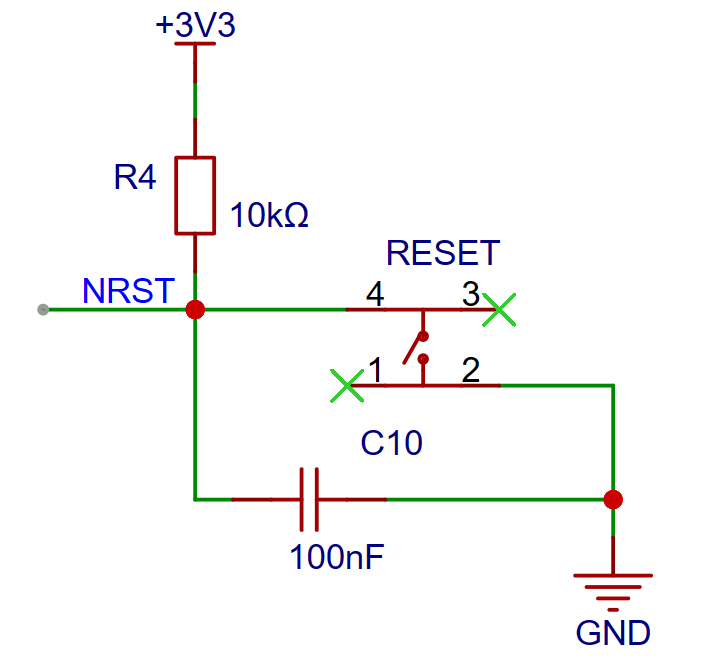

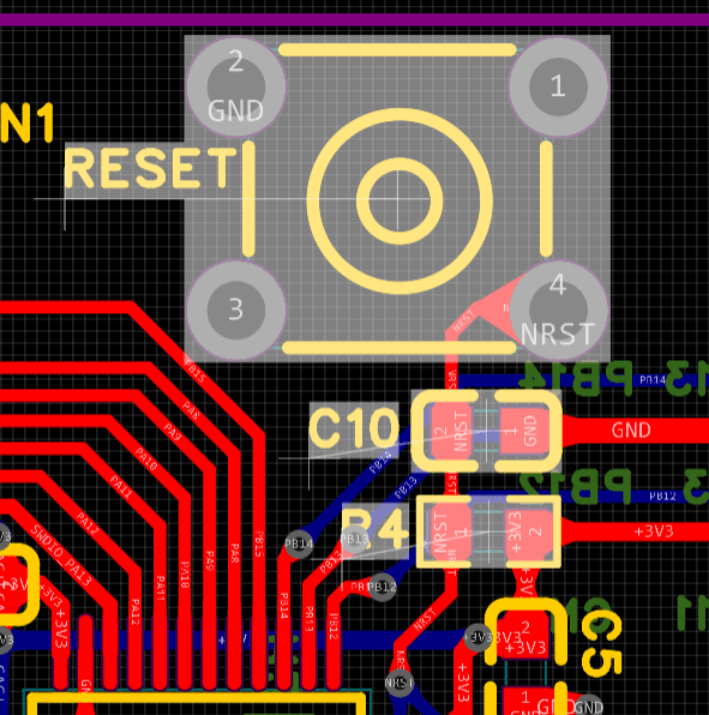

Rücksetzschaltung

Schematische Darstellung

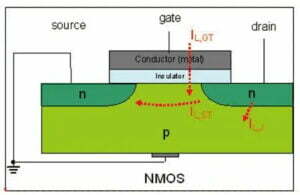

Wenn der NRST-Pin auf Low gezogen wird, wird ein Reset-Signal generiert, wodurch wir einen Reset-Vorgang an unserem Mikrocontroller durchführen können.

Im Schaltplan:

– Wenn der Mikrocontroller wieder eingeschaltet wird, lädt sich der Kondensator C14 auf und leitet Strom. Die RESET-Spannung ist niedrig, was zu einem System-Reset führt. Nach einer bestimmten Zeit, wenn der Kondensator C9 vollständig aufgeladen ist und sich trennt, wird die RESET-Spannung hoch und der Mikrocontroller bleibt stabil, ohne zurückgesetzt zu werden.

– Wenn die Taste gedrückt wird, bleibt sie für 20 bis 50 ms leitfähig und verbindet nRST mit Masse, was zu einer niedrigen Spannung und einem System-Reset führt.

PCB-Design

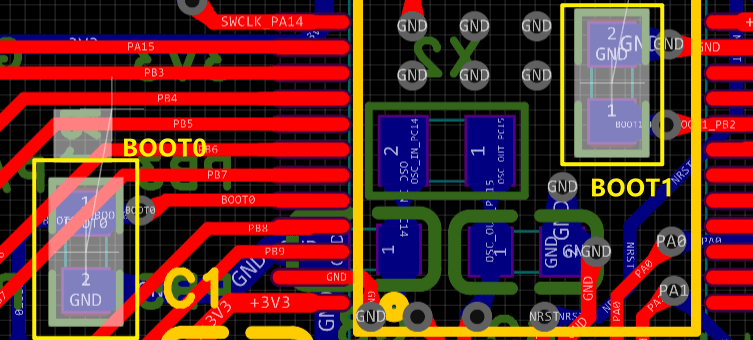

BOOT-Schaltungsdesign

Schematische Darstellung

BOOT0 und BOOT1 des STM32 steuern den Boot-Modus des Chips und unterstützen das Booten aus dem internen FLASH-Speicher, dem Systemspeicher und dem internen SRAM-Speicher. Im Einzelnen:

- Benutzer-Flash: Der integrierte Flash-Speicher des Chips.

- SRAM: Der integrierte RAM-Bereich des Chips.

- Systemspeicher: Ein bestimmter Bereich innerhalb des Chips, in den während der Herstellung ein Bootloader vorinstalliert wird. Dieser wird oft als ISP-Programm bezeichnet.

- ISP-Programme kommunizieren in der Regel über USART1.

Beim Debuggen und Herunterladen von Programmen mit JTAG oder SWD wird das Programm in der Regel in den Flash-Speicher heruntergeladen. In diesem Fall können Sie die Pins BOOT0 und BOOT1 auf Low setzen.

Ein 10K-Widerstand wird verwendet, da BOOT0 und BOOT1 ohne externe Geräte in einem hochohmigen Zustand sind. Die 10K-Pull-up- und Pull-down-Widerstände dienen als gute Strombegrenzer und schützen außerdem den internen IC-Chip.

PCB-Design

Hier platzieren wir die Pull-Down-Widerstände für BOOT0 und BOOT1 auf der Rückseite der Leiterplatte, um eine Beeinträchtigung unserer Leiterbahnen zu vermeiden.

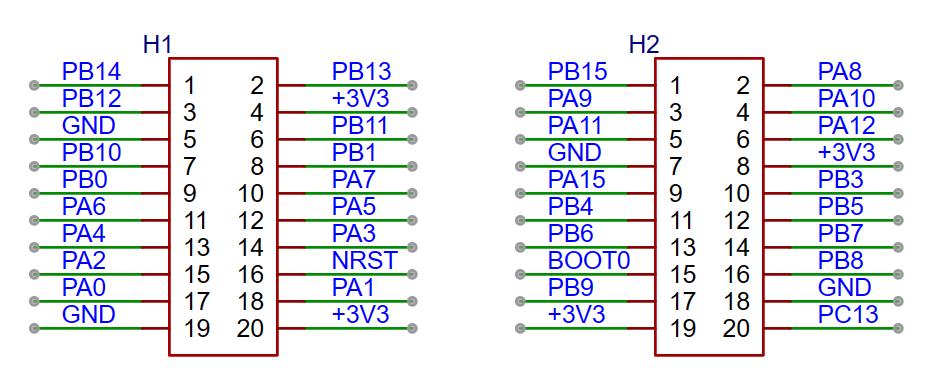

Peripherie-E/A-Port-Schaltung

Schematische Darstellung

Nicht verwendete Pins werden in der Regel über Stiftleisten herausgeführt. Es wird empfohlen, zweireihige Stiftleisten zu verwenden, um die Stabilität zu erhöhen und das Verbiegen beim Einstecken oder Herausziehen zu minimieren. Einreihige Stiftleisten sollten vermieden werden.

Darüber hinaus ist es ratsam, BOOT0 herauszuführen. Dies erleichtert später die Konstruktion einer Ein-Knopf-ISP-Download-Schaltung, die das Herunterladen von Programmen mit einem einzigen USB-Kabel ermöglicht.

Schließlich wird empfohlen, mindestens zwei Sätze von +3V3- und GND-Pins herauszuführen, damit jede Seite der Stiftleiste über eine Stromversorgung verfügt, was die Verdrahtung der Leiterplatte erleichtert.

PCB-Design