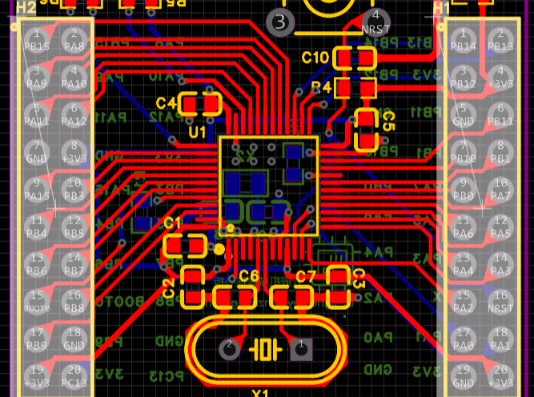

La carte mère STM32F103C8T6 est basée sur la puce officielle du microcontrôleur ST STM32F103C8T6. Cette carte compacte et polyvalente a été méticuleusement conçue pour créer une configuration système minimale, ce qui en fait un choix idéal pour divers projets de systèmes embarqués. Elle offre une gamme de composants essentiels, notamment des circuits pour la sélection du mode BOOT, le découplage, l'oscillateur à quartz, le téléchargement SWD, la fonctionnalité de réinitialisation, l'indication d'alimentation et l'interfaçage des ports d'E/S périphériques. Grâce à sa conception soigneusement pensée, la carte peut être facilement intégrée et étendue pour être utilisée avec d'autres cartes mères. Son efficacité énergétique et ses fonctionnalités robustes en font un outil précieux pour les développeurs, leur permettant de créer et d'expérimenter des applications innovantes sur la plateforme STM32F103C8T6.

Description du projet STM32F103C8T6

Ce projet utilise la puce officielle ST STM32F103C8T6 et conçoit une carte système minimale, qui peut être facilement étendue et utilisée avec la carte mère.

- Les circuits conçus comprennent un circuit BOOT, un circuit de découplage, un circuit oscillateur à quartz, un circuit de téléchargement SWD, un circuit de réinitialisation, un circuit indicateur d'alimentation et un circuit de port E/S périphérique.

- La carte est alimentée par des connexions externes à la broche +3V3 et à la broche GND. Il est recommandé d'alimenter la carte dans une plage comprise entre 3,3 V et 3,6 V, et il est préférable de ne pas dépasser une alimentation de 3,6 V.

- Un circuit indicateur d'alimentation +3V3 est conçu pour indiquer de manière pratique si l'alimentation électrique est normale.

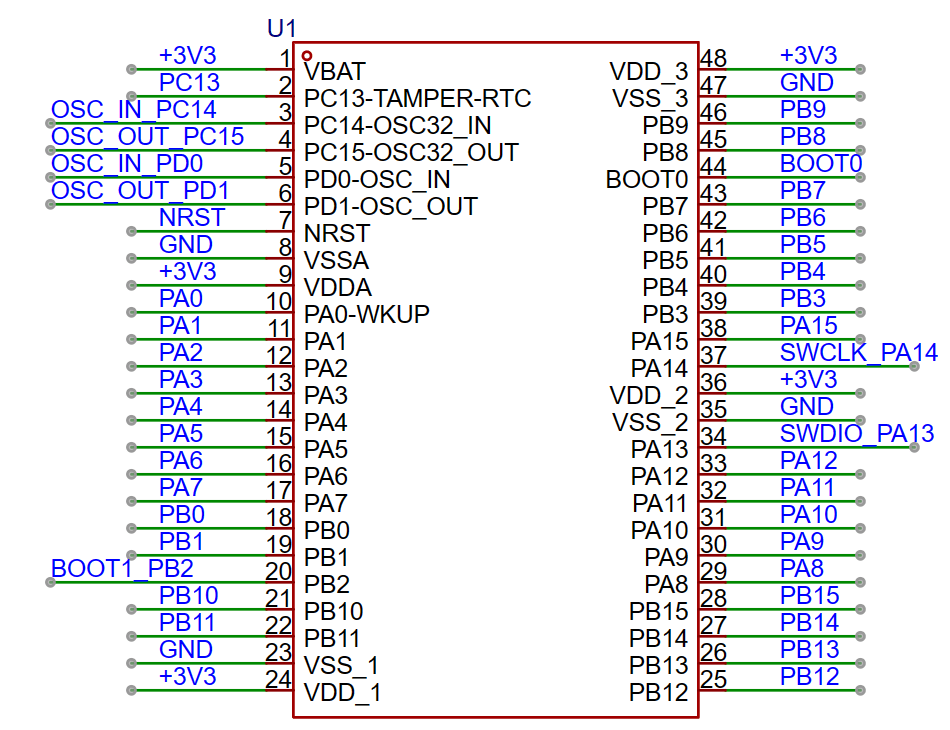

Brochage du STM32F103C8T6

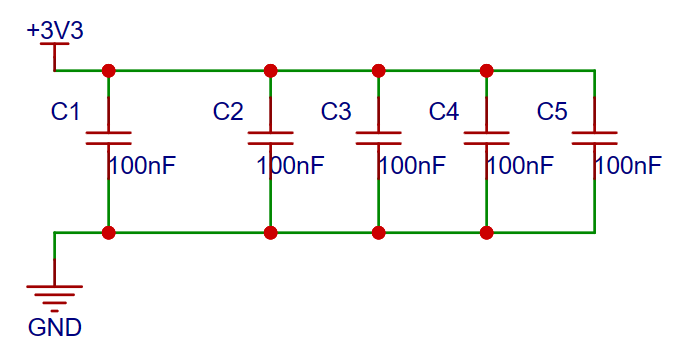

Circuit de découplage

Schéma schématique

Le placement d'un condensateur 104 (0,1 μF) sur les broches d'alimentation permet de supprimer efficacement le bruit sur l'alimentation électrique, ce qui est connu sous le nom de découplage du bruit de l'alimentation électrique.

Plus les points « Alimentation – Condensateur de découplage – Masse » sont proches, meilleur est l'effet de découplage.

Pour les condensateurs de même matériau, même si la capacité diminue à 1/10, l'effet de découplage ne change pas de manière significative. Pour le découplage haute fréquence, les condensateurs de même boîtier, avec des valeurs de capacité de 0,01 μF, 0,1 μF et 1 μF, donnent des résultats similaires.

Les condensateurs à montage en surface (SMD) ont de meilleurs effets de découplage que les condensateurs à trous traversants de même capacité en raison de l'inductance équivalente plus importante des condensateurs à trous traversants, qui affecte l'effet de découplage.

Le condensateur ayant la plus petite capacité a la fréquence de résonance la plus élevée et le rayon de découplage le plus petit. Il doit donc être placé le plus près possible de la puce.

Les condensateurs avec une capacité légèrement supérieure peuvent être placés un peu plus loin, et ceux avec la plus grande capacité doivent être placés sur la couche la plus externe. Cependant, tous les condensateurs destinés au découplage de cette puce doivent être placés aussi près que possible de celle-ci.

Pour les conceptions de circuits imprimés à haute vitesse, il est préférable de placer les condensateurs du même côté que la puce pour un meilleur découplage. Pour les condensateurs de découplage de type MCU, il n'y a pas de différence significative entre les placer à l'avant ou à l'arrière.

Conception de circuits imprimés

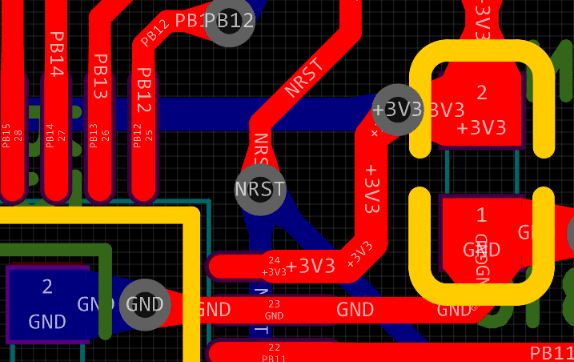

Circuit oscillateur à quartz

Schéma schématique

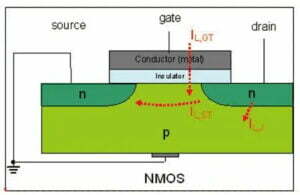

Le STM32 dispose de trois sources d'horloge internes, mais l'arborescence d'horloge de la puce 32 bits nécessite cinq sources d'horloge. Par conséquent, le circuit imprimé doit pouvoir accueillir des horloges externes à haute et basse vitesse.

L'horloge externe haute vitesse peut être un résonateur à quartz/céramique ou une source d'horloge externe, avec une plage de fréquence de 4 MHz à 16 MHz. Un choix courant est un oscillateur à quartz de 8 MHz pour la fréquence principale du système.

L'horloge externe basse vitesse est un cristal de quartz avec une fréquence de 32,768 kHz, utilisé pour piloter l'horloge RTC.

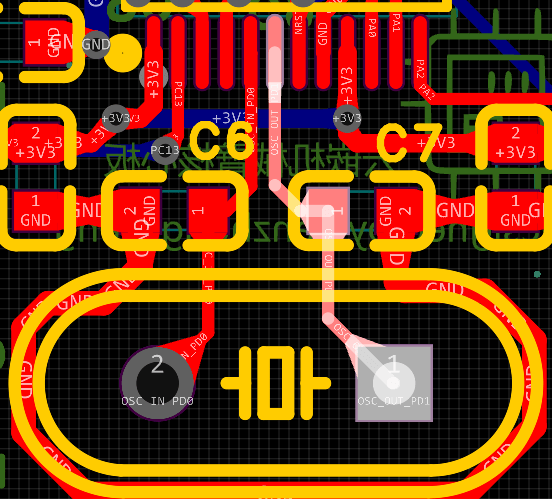

Conception de circuits imprimés

Notez que la zone autour de l'oscillateur à quartz est entourée de traces GND, et il est conseillé d'ajouter des vias sur ces traces GND. Cela permet d'isoler l'oscillateur à quartz. Évitez également de faire passer des traces sur les couches supérieure et inférieure de la zone où se trouve l'oscillateur à quartz, car cela peut nuire à l'intégrité du signal.

De plus, les deux condensateurs situés près de l'oscillateur à quartz doivent être placés symétriquement.

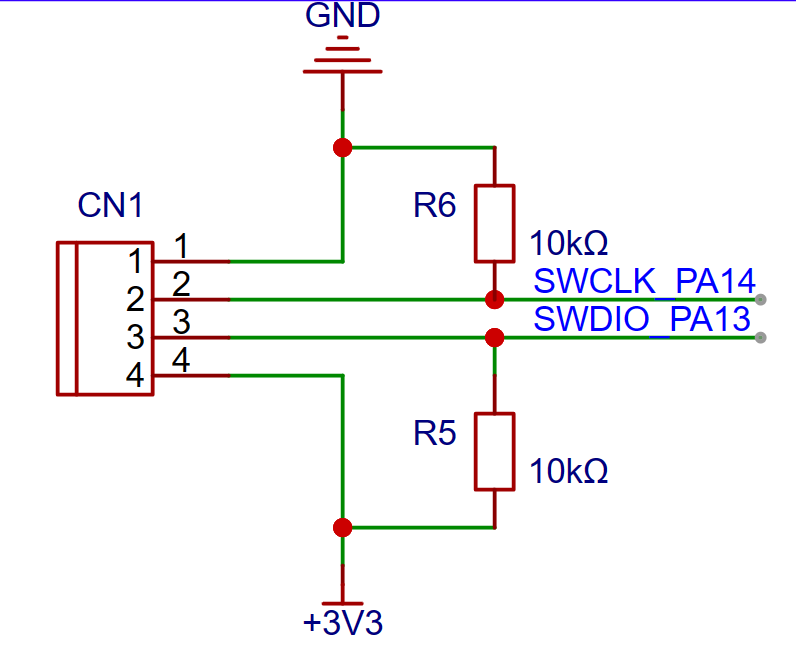

Circuit de téléchargement SWD

Schéma schématique

Introduction au JTAG :

Nous utilisons couramment le téléchargeur Jlink, qui présente l'inconvénient d'utiliser l'interface Jtag 20 broches. Le nombre excessif de broches peut entraîner un encombrement sur les petites cartes PCB et augmenter la complexité du câblage.

L'utilisation de l'interface SWD pour le téléchargement et le débogage ne nécessite que 4 broches : GND, RST, SWDIO, SWDCLK. La vitesse de téléchargement peut atteindre 10 M/s, ce qui offre des avantages évidents.

Mode SWD :

Le mode SWD est plus fiable que le JTAG dans les scénarios à haute vitesse. Dans les situations où les quantités de données sont importantes, le téléchargement de programmes JTAG peut échouer plus fréquemment que le SWD, qui présente un taux d'échec plus faible. En général, si votre émulateur prend en charge le mode de simulation JTAG, vous pouvez utiliser directement le mode SWD, à condition qu'il le prenne en charge.

Conception de circuits imprimés

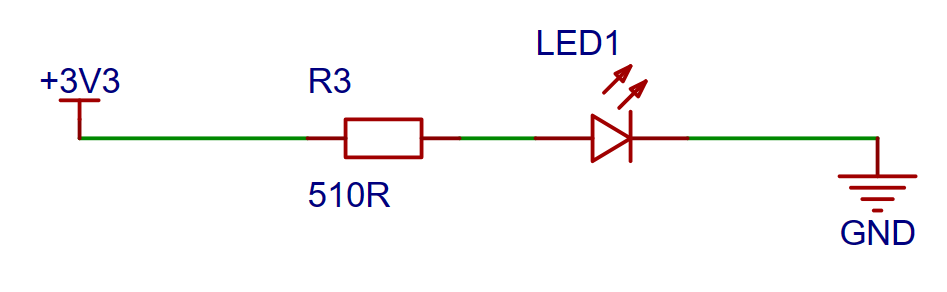

Circuit indicateur d'alimentation

Schéma schématique

Selon la fiche technique, la chute de tension directe maximale est de 2,4 V, avec une valeur typique de 2,1 V. Ainsi, lorsque la LED fonctionne normalement, la chute de tension maximale à travers la LED est de 2,4 V. Dans ce cas, la division de tension à travers R3 est de 0,9 V.

En général, les LED s'allument normalement à des courants compris entre 3 mA et 10 mA. Le courant nominal maximal est de 20 mA. Dans les limites du courant nominal, plus le courant traversant la LED est élevé, plus celle-ci brille.

Ici, nous choisissons I = 10 mA, donc R3 = U / I = 0,9 V / 10 mA = 90 Ω. Comme les résistances de 100 Ω sont plus courantes dans nos matériaux, nous pouvons utiliser une résistance de 100 Ω à la place.

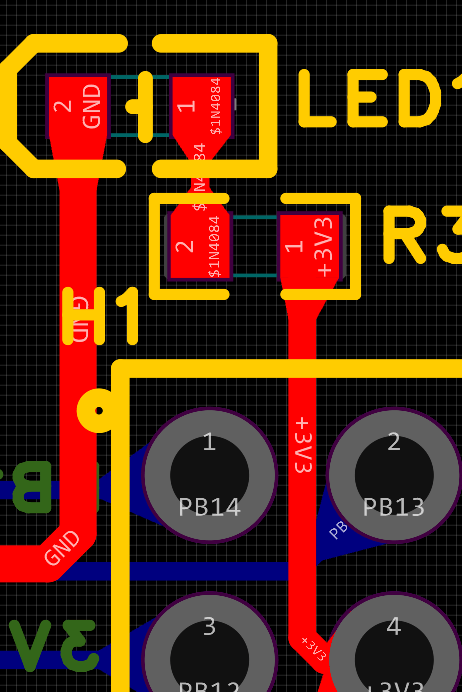

Conception de circuits imprimés

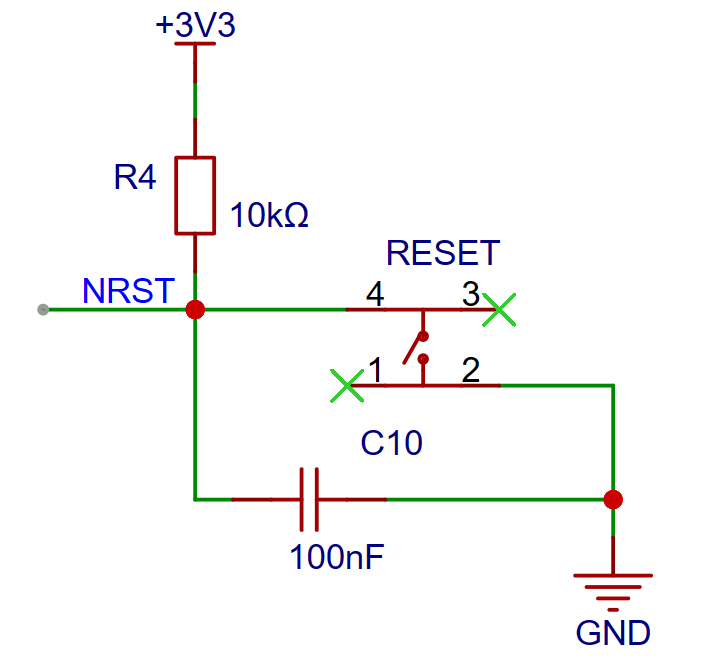

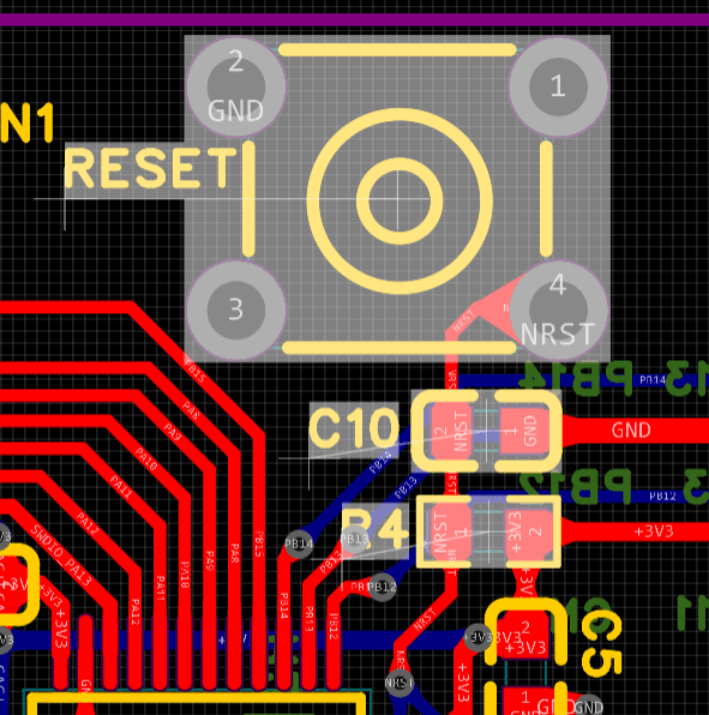

Conception du circuit de réinitialisation

Schéma schématique

Lorsque la broche NRST est mise à l'état bas, un signal de réinitialisation est généré, ce qui nous permet d'effectuer une opération de réinitialisation sur notre microcontrôleur.

Dans le schéma du circuit :

– Lorsque le microcontrôleur est remis sous tension, le condensateur C14 se charge et conduit. La tension RESET est basse, ce qui provoque une réinitialisation du système. Après un certain temps, lorsque le condensateur C9 a fini de se charger et se déconnecte, la tension RESET devient élevée et le microcontrôleur reste stable sans se réinitialiser.

– Lorsque le bouton est enfoncé, il reste conducteur pendant 20 à 50 ms, connectant nRST à la masse, ce qui entraîne une tension basse et une réinitialisation du système.

Conception de circuits imprimés

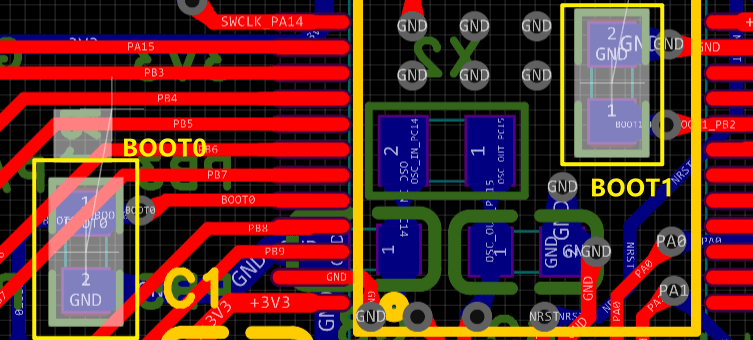

Conception du circuit BOOT

Schéma schématique

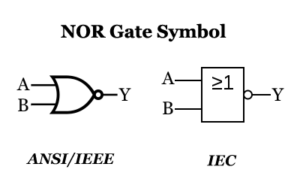

BOOT0 et BOOT1 du STM32 contrôlent le mode de démarrage de la puce, prenant en charge le démarrage FLASH interne, le démarrage de la mémoire système et le démarrage SRAM interne. Plus précisément :

- Flash utilisateur : Flash intégré à la puce.

- SRAM : zone RAM intégrée à la puce.

- Mémoire système : zone spécifique de la puce dans laquelle un chargeur d'amorçage est préchargé lors de la fabrication. On parle souvent de programme ISP.

- Les programmes ISP communiquent généralement via USART1.

Lors du débogage et du téléchargement de programmes à l'aide de JTAG ou SWD, le programme est généralement téléchargé dans la mémoire Flash. Dans ce cas, vous pouvez régler les broches BOOT0 et BOOT1 sur faible.

Une résistance de 10K est utilisée car BOOT0 et BOOT1 sont dans un état de haute impédance sans dispositifs externes. Les résistances pull-up et pull-down de 10K servent de bons limiteurs de courant et protègent également la puce IC interne.

Conception de circuits imprimés

Ici, nous plaçons les résistances de rappel vers le bas pour BOOT0 et BOOT1 à l'arrière du circuit imprimé afin d'éviter toute interférence avec nos traces.

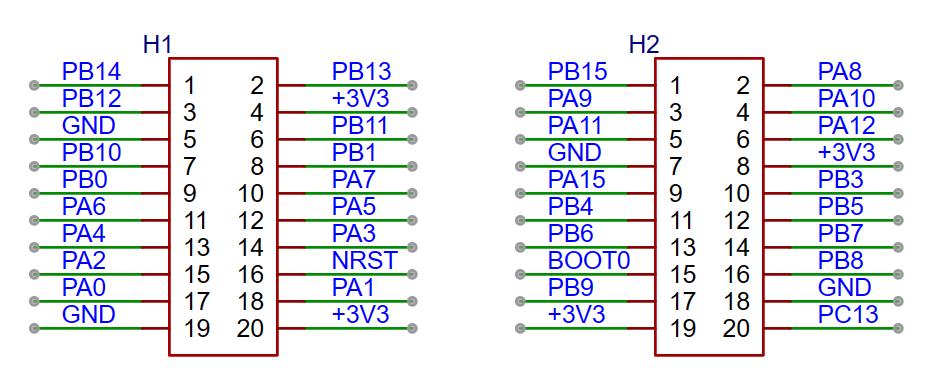

Circuit de port d'E/S périphérique

Schéma schématique

Les broches inutilisées sont généralement reliées à l'aide de connecteurs à broches. Il est recommandé d'utiliser des connecteurs à broches à double rangée pour améliorer la stabilité et minimiser la flexion lors de l'insertion ou du retrait, en évitant les connecteurs à broches à simple rangée.

De plus, il est conseillé de sortir BOOT0. Cela facilite la conception ultérieure d'un circuit de téléchargement ISP à un seul bouton, permettant le téléchargement de programmes à l'aide d'un seul câble USB.

Enfin, il est recommandé de sortir au moins deux jeux de broches +3V3 et GND, afin que chaque côté du connecteur à broches dispose d'une alimentation électrique, ce qui facilite le câblage du circuit imprimé.

Conception de circuits imprimés