SWD et JTAG sont des interfaces de débogage populaires pour les microcontrôleurs basés sur Cortex-M. Mais ces deux interfaces sont différentes tant au niveau de leur structure que de leurs applications. Dans cet article, nous présenterons leurs broches, leur principe de fonctionnement, leurs avantages et leurs inconvénients.

Interface SWD

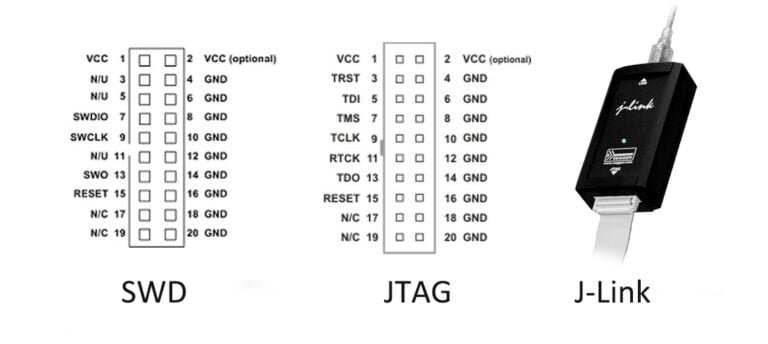

SWD, Serial Wire Debug, est un protocole conçu par ARM pour la programmation et le débogage de ses microcontrôleurs. Il est basé sur l'architecture de débogage ARM CoreSight et permet la lecture et l'écriture des registres de puces via des paquets de données. SWD est un protocole à deux fils permettant d'accéder aux interfaces de débogage ARM. Il fait partie de la spécification ARM Debug Interface Architecture et sert d'alternative au JTAG. Dans les cas où la disposition des circuits imprimés est limitée et où les ressources en broches sont restreintes, le SWD est un bon choix. De nombreux débogueurs sur le marché prennent en charge les interfaces de débogage SWD, tels que ST-Link, J-Link, e-Link, GD-Link et autres.

Épingles SWD

SWDIO : Serial Wire Data Input Output, broche d'entrée et de

sortie de données série SWCLK : Serial Wire Clock, broche d'horloge de ligne série

Pour SWDIO, il s'agit d'une broche de données bidirectionnelle (entrée et sortie), et la ligne doit être tirée vers le haut sur le circuit imprimé (ARM recommande 100 K).

Comment fonctionne SWD ?

Les périphériques externes, tels que les sondes de débogage, se connectent à SWDIO/SWCLK pour accéder directement au port de débogage série (SW-DP). Le SW-DP peut accéder à un ou plusieurs ports d'accès (AP) et, via ces derniers, aux autres registres du système. L'AHB-AP est un AP important pour les processeurs Cortex M-series, car il sert de maître sur le bus AHB interne. En d'autres termes, l'AHB-AP peut accéder à la carte mémoire du cœur interne. Étant donné que la mémoire flash interne, la SRAM, les composants de débogage et les périphériques sont tous mappés en mémoire, l'AHB-AP peut contrôler l'ensemble du dispositif, y compris sa programmation. L'ensemble du processus de fonctionnement SWD est hiérarchique, avec des signaux d'horloge entrant par la broche SWCLK et des signaux de données entrant/sortant par la broche SWDIO. Au départ, le débogueur fonctionne sur le SW-DP pour déterminer les paramètres des registres AP, ce qui permet de manipuler la carte mémoire Cortex.

Avantages du SWD

- Réduction du nombre de signaux

- Fiabilité à grande vitesse

- Probabilité réduite de défaillances

- Compatibilité avec les simulations JTAG

- Nécessite moins de broches pour fonctionner

Interface JTAG

Le JTAG (Joint Test Action Group) était à l'origine utilisé pour tester des puces. Ce groupe a lancé des discussions à la fin des années 1980 et a officiellement publié des documents interprétant les normes IEEE en 1990. (IEEE signifie Institute of Electrical and Electronics Engineers, une organisation internationale chargée de publier des normes telles que WiFi et Bluetooth.) Le protocole qu'ils ont proposé a été documenté dans la norme IEEE 1149.1 en 1990. Ce document a depuis fait l'objet de révisions et d'améliorations, la dernière norme en date au moment de la rédaction du présent document étant la norme IEEE 1149.7.

Broches JTAG

- TDI : Test Data In, une broche d'entrée série.

- TDO : sortie de données de test, une broche de sortie série.

- TCK : horloge de test, une broche d'horloge.

- TMS : Test Mode Select, une broche de sélection de mode (signal de commande).

- TRST : Test Reset, une broche de réinitialisation.

Comment fonctionne JTAG ?

Le principe du JTAG consiste à définir un port d'accès de test (TAP) au sein du dispositif. Cela permet de tester les nœuds internes à l'aide d'outils de test JTAG spécialisés. Le test JTAG permet de connecter plusieurs dispositifs en série via une interface JTAG, formant ainsi une chaîne JTAG pour le test individuel des dispositifs. De nos jours, les interfaces JTAG sont également couramment utilisées pour les opérations de programmation dans le système (ISP), telles que la programmation des dispositifs FLASH. En termes de structure matérielle, l'interface JTAG se compose de deux parties : le port JTAG et le contrôleur. Les dispositifs compatibles avec l'interface JTAG peuvent être des microprocesseurs (MPU), des microcontrôleurs (MCU), des PLD, des CPLD, des FPGA, des DSP, des ASIC ou d'autres puces conformes aux spécifications IEEE 1149.1. La norme IEEE 1149.1 impose la présence d'un registre à décalage appelé unité de balayage des limites (BSU) pour chaque broche d'une puce de circuit intégré numérique. Il relie le circuit JTAG au circuit logique central tout en isolant ce dernier des broches de la puce. L'ensemble des unités de balayage des limites de la puce constitue le registre de balayage des limites (BSR). Le circuit du registre de balayage des limites n'est actif que pendant les tests JTAG et n'affecte pas le fonctionnement de la puce en mode normal.

Le protocole JTAG contrôle la transition de la machine à états TAP via le signal TMS. Après la mise sous tension du système, le contrôleur TAP entre d'abord dans l'état Test-Logic Reset, puis passe séquentiellement par les états Run-Test/Idle, Select-DR-Scan, Select-IR-Scan, Capture-IR, Shift-IR, Exit1-IR et Update-IR avant de revenir à Run-Test/Idle. Au cours de ce processus, les transitions d'état sont pilotées par le signal TCK (front montant), les signaux TMS étant utilisés pour sélectionner l'état TAP. Dans l'état Capture-IR, une séquence logique spécifique est chargée dans le registre d'instructions ; dans l'état Shift-IR, une instruction spécifique peut être décalée dans le registre d'instructions ; et dans l'état Update-IR, l'instruction qui vient d'être entrée dans le registre d'instructions est utilisée pour mettre à jour le registre d'instructions. Enfin, le système revient à l'état Run-Test/Idle, où l'instruction prend effet, achevant ainsi l'accès à l'instruction et aux registres. Après être revenu à l'état Run-Test/Idle, en fonction du contenu du registre d'instructions, le registre de données requis est sélectionné et le travail sur les registres de données commence.

Avantages du JTAG

- Le JTAG ne se limite pas aux puces ARM ; il est pris en charge dans des puces autres que celles d'ARM, telles que la célèbre MSP430.

- Le JTAG offre un large éventail d'applications pour la programmation, le débogage et les tests de production.

- JTAG est un groupe indépendant qui évolue avec le développement du protocole.

Conclusion

JTAG et SWD sont deux interfaces importantes pour le débogage des systèmes embarqués, chacune ayant ses propres avantages et inconvénients. Le choix de l'interface dépend des exigences du projet, de la prise en charge matérielle et des besoins en termes de performances. Pour les systèmes complexes, JTAG peut être nécessaire pour obtenir plus de contrôle et de fonctionnalités, tandis que SWD peut être mieux adapté aux systèmes aux ressources limitées. La prise en compte de l'ensemble de ces facteurs peut vous aider à prendre des décisions éclairées pour un développement et un débogage plus efficaces des systèmes embarqués.