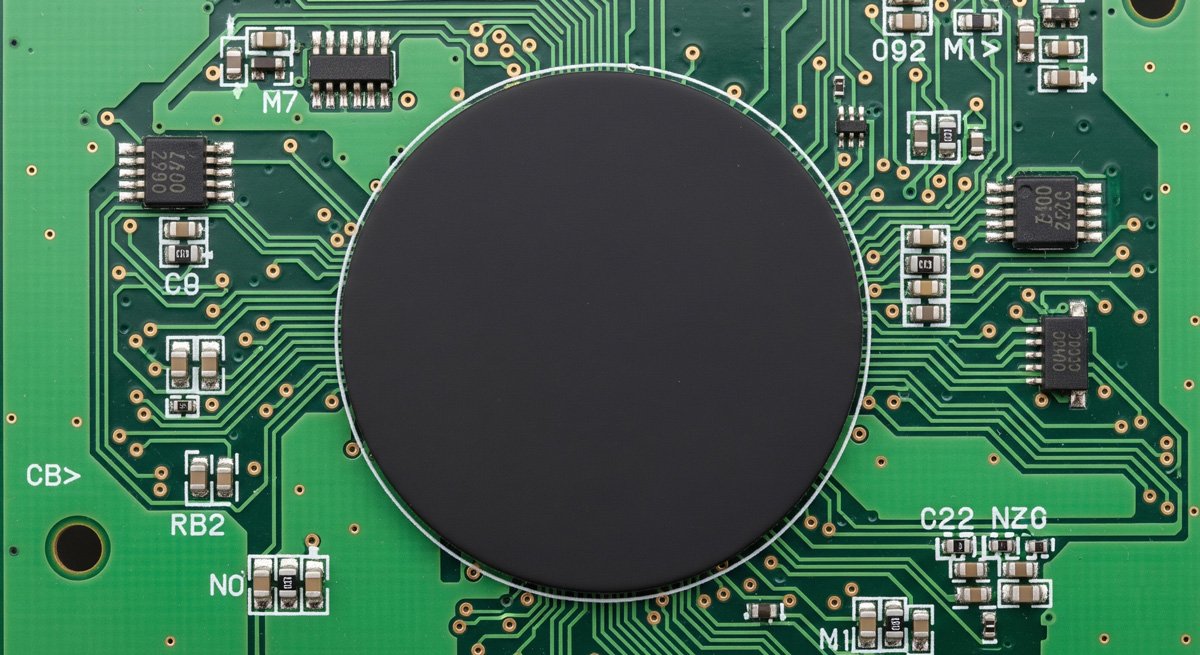

À l'ère des serveurs IA, des smartphones 5G et des véhicules autonomes, les performances d'une puce dépendent entièrement de la qualité du « système nerveux » qui la soutient : le substrat du circuit intégré. Alors que la densité des circuits atteint ses limites physiques, le choix du procédé de fabrication détermine l'intégrité du signal et la fiabilité du produit final.

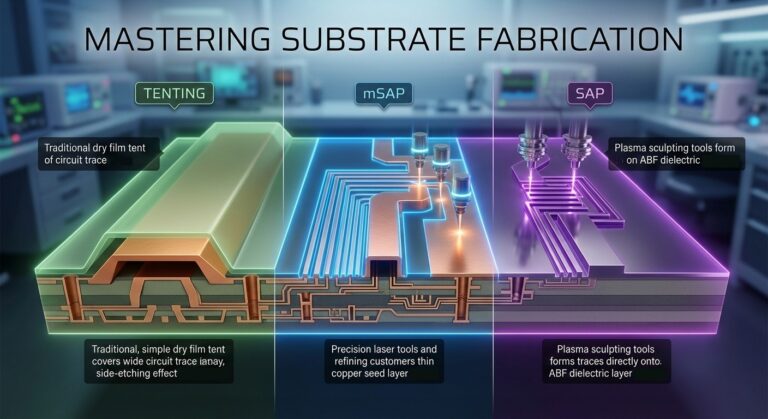

Aujourd'hui, trois « outils de sculpture » principaux dominent le secteur : le Tenting (soustractif), le mSAP (procédé semi-additif modifié) et le SAP (procédé semi-additif). Ce guide détaille leurs mécanismes techniques, leurs avantages et leurs inconvénients, ainsi que leur place dans l'écosystème électronique moderne.

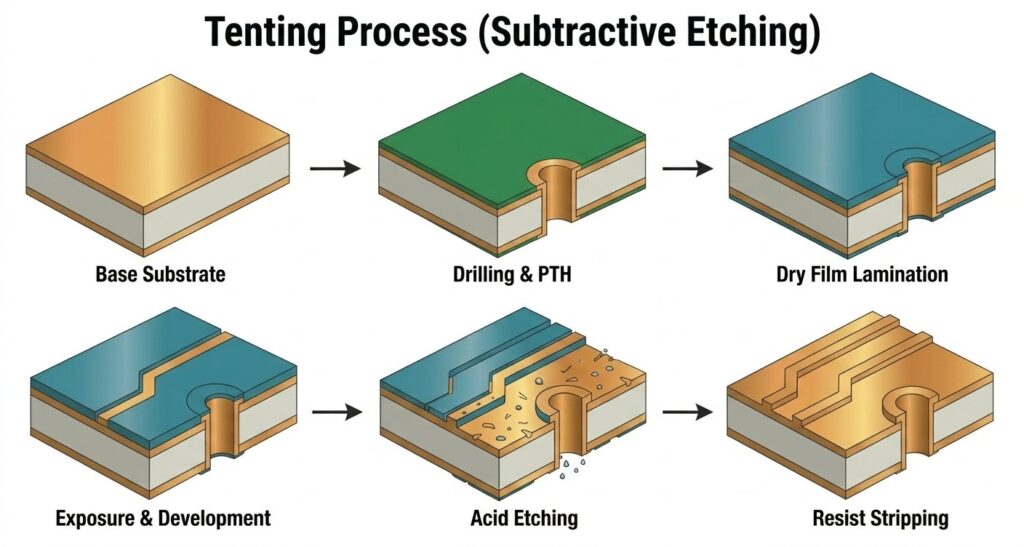

1. Procédé de tentage (méthode soustractive)

Le procédé de « tenting » est la technologie de formation de circuits la plus traditionnelle et la plus répandue dans l'industrie des circuits imprimés et des substrats à faible densité. Son principe fondamental repose sur le principe « recouvrir puis retirer », un peu comme lorsqu'on sculpte un sceau dans un bloc de pierre.

Fonctionnement : on commence avec un stratifié revêtu de cuivre (CCL) comportant une feuille de cuivre épaisse (généralement > 12 µm). Un film sec (photorésist) recouvre les zones du circuit prévues, telle une « tente » au-dessus des trous (d'où le nom). Le cuivre non protégé est ensuite éliminé par gravure chimique.

Le problème (gravure latérale) : comme la gravure enlève le cuivre simultanément à la verticale et à l'horizontale, elle crée une section transversale « trapézoïdale ». Cette « gravure latérale » limite la précision de la largeur de ligne et de l'espacement (L/S) à environ 30 µm/30 µm.

Idéal pour : l'électronique grand public standard, les circuits imprimés automobiles et les substrats BGA à câblage filaire (WB BGA) traditionnels.

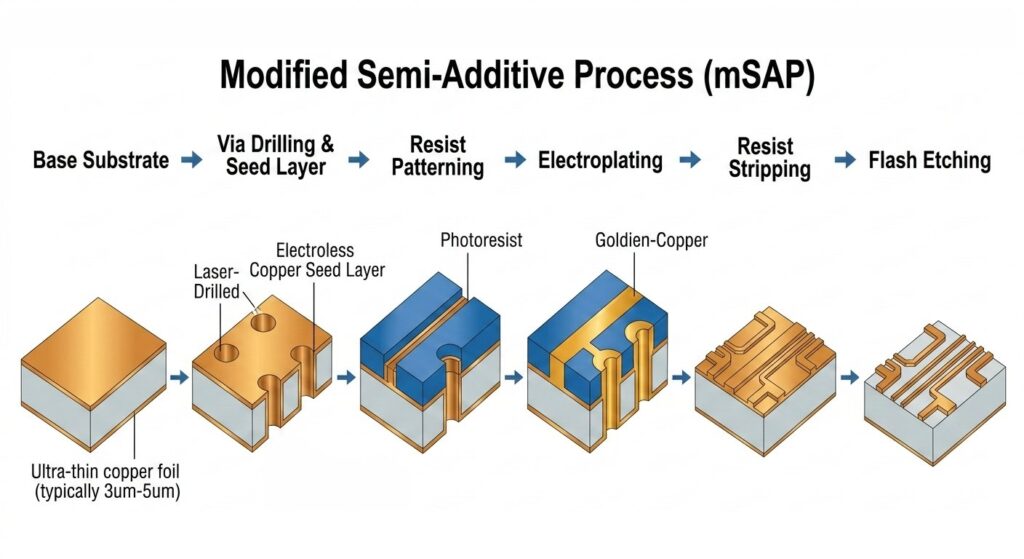

2. mSAP (procédé semi-additif modifié)

À mesure que le nombre de broches augmentait et que les signaux s'accéléraient, le mSAP s'est imposé comme le pont entre les circuits imprimés traditionnels et les substrats de circuits intégrés haut de gamme. Il constitue aujourd'hui le choix privilégié pour les substrats FCBGA utilisés dans les puces réseau et les processeurs haut de gamme des smartphones.

Fonctionnement : au lieu d'utiliser du cuivre épais, le mSAP part d'une base de cuivre ultra-fine (généralement de 3 à 5 µm) ou d'une « couche d'amorçage » déposée chimiquement. Les circuits sont « ajoutés » par galvanoplastie sélective jusqu'à l'épaisseur souhaitée.

L'avantage : après le placage, une « gravure flash » rapide élimine la couche de base ultra-fine. La base étant très fine, le temps de gravure est minime, ce qui permet d'obtenir des parois de circuit rectangulaires presque verticales avec des capacités $L/S$ pouvant descendre jusqu'à $10\mu m/10\mu m$.

Idéal pour : les processeurs d'application (AP) pour smartphones haut de gamme (série A d'Apple, Snapdragon), les boîtiers à l'échelle de la puce (FCCSP) et les circuits imprimés de type substrat (SLP).

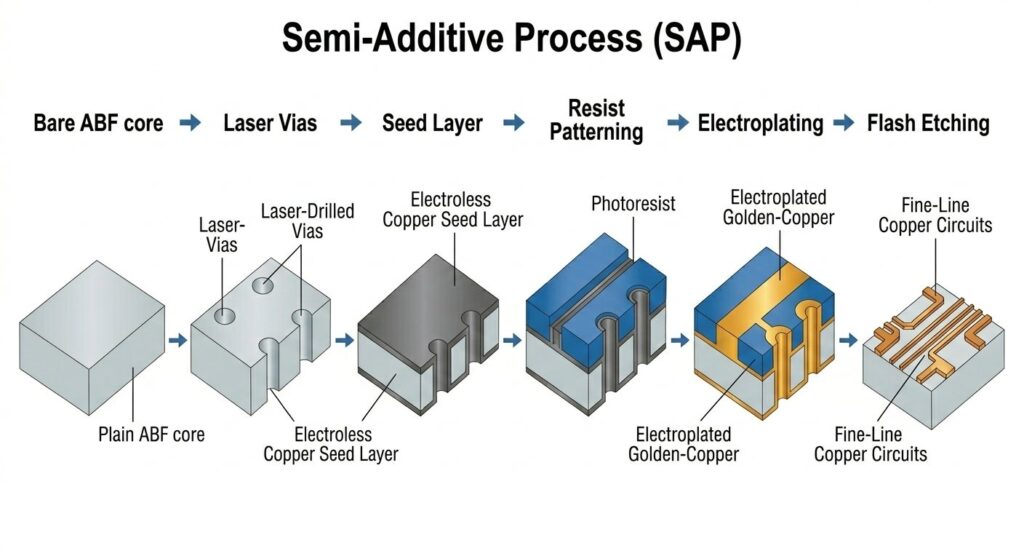

3. SAP (procédé semi-additif)

La technologie SAP représente le summum de la précision en matière de circuits imprimés ; elle est souvent qualifiée de version « purifiée » du mSAP. Elle abandonne totalement la feuille de cuivre au profit d’une « addition pure ».

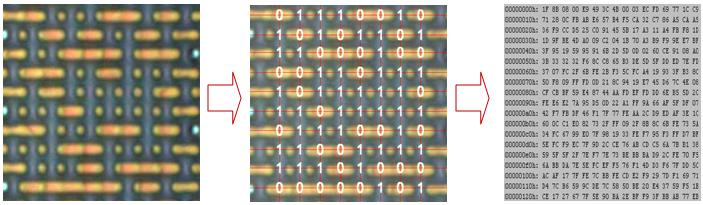

Fonctionnement : il utilise un matériau diélectrique sans cuivre, notamment l'ABF (Ajinomoto Build-up Film). Une « couche d'amorçage » microscopique ($< 1\mu m$) est déposée chimiquement sur la surface lisse, suivie d'un placage sélectif pour construire les circuits.

L'avantage : la couche d'amorçage étant quasi inexistante, la gravure n'a aucun impact sur la morphologie du circuit. Cela permet une précision extrême ($L/S < 10\mu m$) et un contrôle supérieur de l'impédance pour les signaux à haute vitesse.

Idéal pour : le calcul haute performance (HPC), les accélérateurs d'IA (Nvidia H100) et les conditionnements avancés tels que CoWoS et HBM.

4. Tableau comparatif : Tenting, mSAP et SAP

| Feature | Tenting | mSAP | SAP |

|---|---|---|---|

| Core Principle | Subtractive: Etch away thick copper foil | Additive: Plate over ultra-thin copper base | Pure Additive: Seed layer on copper-free dielectric |

| Line Precision (L/S) | > 30μm | 10μm - 30μm | < 10μm |

| Cross-section Shape | Trapezoidal (Side-etching) | Near-Rectangular | Perfectly Rectangular |

| Base Material | Standard CCL | Ultra-thin copper foil | ABF (Ajinomoto Build-up Film) |

| Primary Application | Consumer PCBs / Motherboards | Smartphone AP / High-end HDI | AI Accelerators / CPU / GPU Substrates |

| Cost & Maturity | Low Cost / Highly Mature | Medium-High / Mainstream High-end | Very High / Cutting-edge |

Perspectives d'avenir : l'avenir de la fabrication

Le secteur s'oriente vers une approche « hybride » visant à trouver un équilibre entre coût et performances, en utilisant la technique du « tenting » pour les couches centrales et les procédés mSAP/SAP pour les couches externes à haute densité. Alors que la demande en IA repousse les limites de la loi de Moore, les technologies émergentes telles que les substrats en verre et les puces intégrées continueront d'évoluer parallèlement à ces trois procédés fondamentaux.

Comprendre les nuances de ces méthodes de fabrication est la première étape pour maîtriser le paysage complexe de l'encapsulation moderne des puces et de la sécurité matérielle.