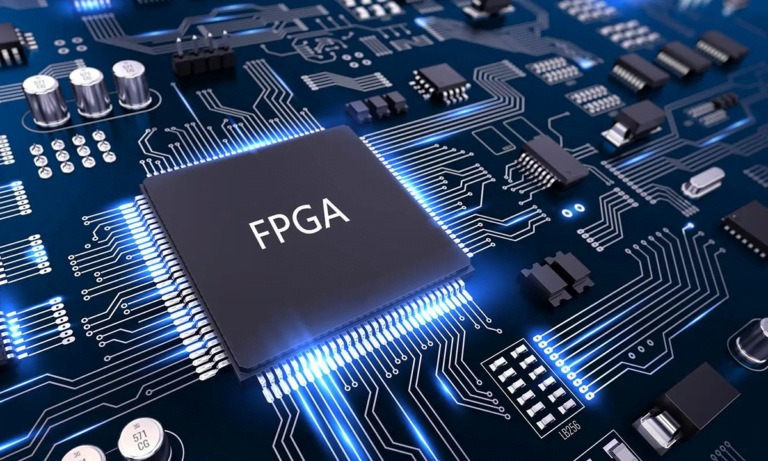

FPGA, abréviation de Field Programmable Gate Array (matrice prédiffusée programmable), est une architecture matérielle reconfigurable. En d'autres termes, il s'agit d'une puce qui peut être programmée pour modifier sa structure interne. Les FPGA sont utilisés depuis de nombreuses années comme substituts à faible volume des puces spécifiques à une application (ASIC).

Structure de base d'un FPGA

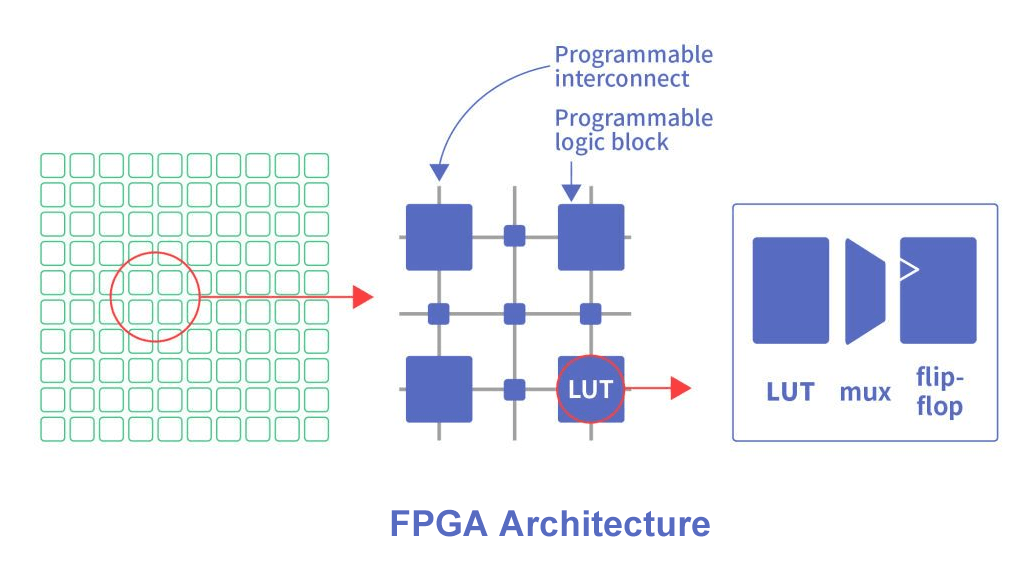

L'architecture FPGA comprend principalement quatre parties : un bloc logique configurable (CLB), un bloc d'entrée et de sortie (IOB), un câblage interne (interconnexion) et d'autres unités intégrées. La structure interne du dispositif FPGA est illustrée ci-dessous.

Bloc logique configurable (CLB)

Le CLB est l'unité logique de base du FPGA. Le nombre et les caractéristiques réels varient d'un dispositif à l'autre, mais chaque CLB contient une matrice de commutation configurable à 4 ou 6 entrées, plusieurs circuits de sélection (multiplexeurs, etc.) et des bascules.

Bloc d'entrée et de sortie (IOB)

Les FPGA peuvent prendre en charge de nombreuses normes d'E/S, ce qui en fait un pont d'interface idéal pour la conception de systèmes. Les E/S dans le FPGA sont regroupées par banque, et chaque banque peut prendre en charge indépendamment différentes normes d'E/S. À l'heure actuelle, le FPGA le plus avancé fournit plus de dix banques d'E/S, ce qui permet une prise en charge flexible des E/S.

Câblage interne (interconnexion)

Les CLB fournissent les performances logiques, tandis que le routage d'interconnexion flexible est chargé de transmettre les signaux entre les CLB et les E/S. Il existe plusieurs types de routage, allant des interconnexions CLB dédiées (ressources à câbles courts) aux câbles horizontaux et verticaux à grande vitesse (ressources à câbles longs) au sein du dispositif, en passant par le routage global à faible décalage pour les horloges et autres signaux globaux (ressources de routage globales dédiées).

Unités intégrées

Les unités centrales intégrées comprennent la mémoire vive (RAM), le processeur de signal numérique (DSP), le module de gestion d'horloge numérique (DCM) et d'autres unités centrales d'interface spécifiques, etc.

Caractéristiques du FPGA

- L'utilisation d'un FPGA pour concevoir un circuit ASIC permet un cycle court, un coût faible, un risque réduit et une qualité stable.

- Le FPGA adopte la technologie CHMOS haute vitesse à faible consommation d'énergie ;

- Architecture FPGA, unité logique flexible, haute intégration, large gamme d'applications ;

- Le FPGA est compatible avec les avantages du PLD et du réseau de portes générales, et peut réaliser des circuits à grande échelle ;

- La reprogrammation sur site est possible et les coûts de maintenance ultérieurs sont faibles ;

- Le FPGA est un calcul parallèle qui peut répondre simultanément à des exigences multifonctionnelles.

Comment fonctionne un FPGA ?

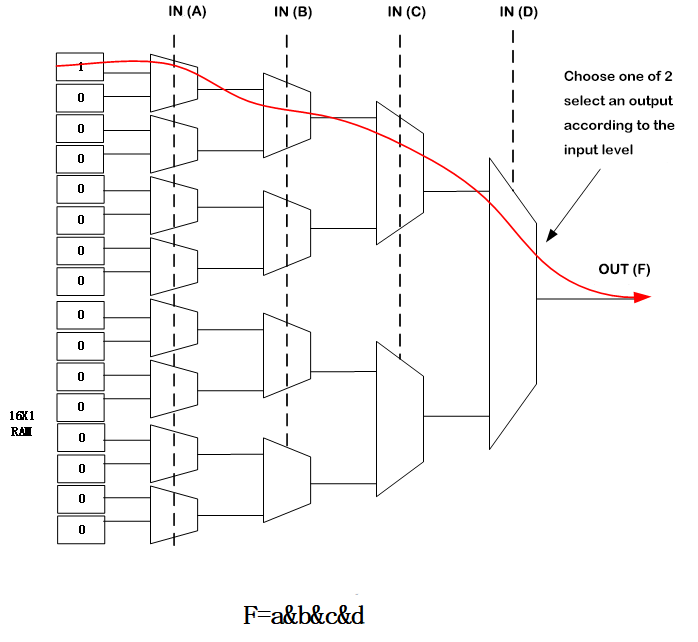

Le FPGA implémente des fonctions logiques en chargeant des données de programmation dans des unités de stockage statique internes. La valeur stockée dans l'unité de stockage détermine la fonction logique de l'unité logique et le mode de connexion entre chaque module d'unité logique ou entre le module et l'E/S, et détermine finalement la fonction réalisée par le FPGA. Le FPGA utilise une petite table de consultation pour mettre en œuvre la logique combinatoire. Chaque table de consultation est connectée à l'entrée d'une bascule D, et la bascule D est utilisée pour piloter d'autres circuits logiques ou E/S, formant ainsi une fonction logique combinée et réalisant le module de base de la fonction logique séquentielle. Ces modules sont connectés entre eux ou au module E/S par des fils métalliques.

Voici un exemple simple pour expliquer le principe du FPGA :

Comme le montre la figure ci-dessus, nous configurons la RAM 16 bits comme 0000000000000001, et ce circuit est équivalent à F=A&B&C&D ;

Uniquement lorsque A=B=C=D=1, F=1, sinon F=0 ;

« 0000000000000001 » Cette chaîne de chiffres correspond à la programmation FPGA.

Bloc logique du FPGA

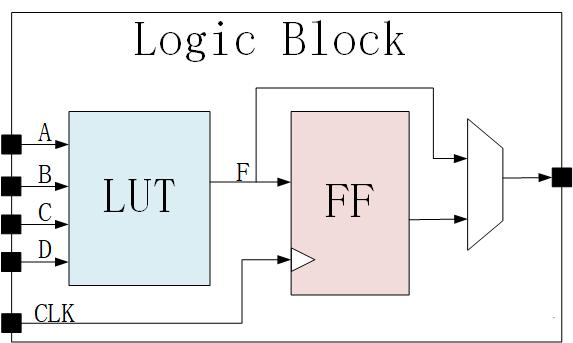

Il existe un terme spécifique en FPGA, appelé LUT, table de correspondance (table de consultation).

La LUT constitue l'unité la plus élémentaire de tout FPGA.

La LUT ne peut implémenter que la logique combinatoire numérique, c'est pourquoi un registre bascule (ff) est ajouté pour réaliser le verrouillage des données.

Comme le montre la figure ci-dessous : Les LUT + registres forment la structure de base des FPGA modernes.

Processus de développement FPGA

Le processus de développement FPGA consiste à utiliser des logiciels de développement EDA et des outils de programmation pour développer des puces FPGA. Le processus de développement FPGA est généralement illustré dans la figure ci-dessous. Il comprend les étapes principales suivantes : définition des fonctions/sélection des dispositifs, saisie de la conception, simulation des fonctions, synthèse logique, disposition et routage, implémentation, programmation et débogage.

Définition de la fonction/sélection du dispositif :

Avant le lancement du projet de conception FPGA, il est nécessaire de définir les fonctions du système et la répartition des modules. De plus, en fonction des exigences de la tâche, telles que la fonction et la complexité du système, la vitesse de travail et les ressources, les coûts et les connexions du dispositif lui-même peuvent être répartis. Il convient de trouver un compromis entre différents aspects, tels que les performances, et de sélectionner le schéma de conception et le type de dispositif appropriés.

Contribution à la conception :

La conception désigne l'utilisation d'un langage de description du matériel pour exprimer le système ou le circuit conçu sous forme de code. Le langage de description du matériel le plus couramment utilisé est Verilog HDL.

Simulation fonctionnelle :

La simulation fonctionnelle consiste à vérifier la fonction logique du circuit conçu par l'utilisateur avant la synthèse logique. Avant la simulation, il est nécessaire de construire une plateforme de test et de préparer des stimuli de test. Les résultats de la simulation génèrent des fichiers de rapport et des formes d'onde de signal de sortie, à partir desquels les changements des signaux de chaque nœud peuvent être observés. Si des erreurs sont détectées, revenez à la conception pour réviser la conception logique. Les outils de simulation courants comprennent ModelSim de Model Tech, VCS de Sysnopsys et d'autres logiciels.

Synthèse logique :

La synthèse consiste à transformer la description du niveau d'abstraction supérieur en description du niveau inférieur. L'optimisation synthétique optimise les connexions logiques générées en fonction des objectifs et des exigences, et rend la conception hiérarchique plane pour que le logiciel de routage et de disposition FPGA puisse la mettre en œuvre. En ce qui concerne le niveau actuel, l'optimisation complète consiste à compiler les données de conception en une liste de connexions logiquement reliées, composée d'unités logiques de base telles que des portes ET, des portes OU, des portes NON, des mémoires RAM et des bascules, plutôt que de véritables circuits au niveau des portes.

Mise en page et réalisation :

La disposition et le routage peuvent être compris comme l'utilisation d'outils d'implémentation pour mapper la logique aux ressources de la structure du dispositif cible, déterminer la disposition optimale de la logique, sélectionner les canaux de câblage reliés par la logique et les fonctions d'entrée et de sortie, et générer les fichiers correspondants (tels que les fichiers de configuration et les rapports associés) ; l'implémentation consiste à configurer la liste d'interconnexions logique générée par la synthèse sur une puce FPGA spécifique. Étant donné que seul le fabricant de la puce FPGA connaît parfaitement la structure de la puce, la disposition et le routage doivent choisir les outils fournis par le développeur de la puce.

Débogage de programmation :

La dernière étape de la conception consiste à programmer et à déboguer. La programmation de la puce consiste à générer des fichiers de données (fichiers bitstream, Bitstream Generaon) et à charger les données de programmation dans la puce FPGA ; après cela, le test de la carte peut être effectué. Enfin, téléchargez le fichier FPGA (tel que le fichier .bit) de l'ordinateur vers la puce FPGA sur la carte.

FPGA vs CPU et GPU

Les processeurs centraux (CPU) et les processeurs graphiques (GPU) suivent tous deux l'architecture von Neumann avec décodage des instructions et mémoire partagée. En revanche, les FPGA ont une architecture intrinsèquement différente qui ne repose pas sur des instructions et ne nécessite pas de mémoire partagée. Le tableau ci-dessous montre leurs différences :

| Feature | FPGA | CPU | GPU |

|---|---|---|---|

| Architecture | Reconfigurable logic | Von Neumann | Von Neumann |

| Instruction | No instructions | Instructions | Instructions |

| Shared Memory | No shared memory | Arbitration and shared memory | Arbitration and shared memory |

| Parallel Processing | Pipeline and data parallelism | Data parallelism | Data parallelism |

| Flexibility | Reprogrammable | Fixed functionality | Fixed functionality |

| Computational Power | Suitable for complex tasks | General-purpose computing | Parallel computing and vector processing |

| Latency | Low latency | Medium latency | Relatively high latency |

| Power Consumption | High power consumption | Medium power consumption | High power consumption |

| Application Areas | Electronics, communication, embedded systems | General-purpose computing | Graphics processing, scientific computing |

Compétences requises pour les ingénieurs FPGA

- Langage Verilog et son rapport avec les circuits matériels

- Outils de développement (maîtrise de Synplify, vivodo, ISE, Modelsim)

- Connaissance du processus de conception FPGA (simulation, synthèse, disposition et routage, analyse de synchronisation)

- Maîtrise de l'estimation des ressources (en particulier l'estimation des ressources slice, lut, ram et autres)

- Maîtrise des concepts de base (tels que le temps de configuration, le temps de maintien, le calcul du débit, le calcul du temps de retard, le risque concurrentiel, les méthodes d'élimination des parasites, etc.

- Circuits numériques (circuits combinatoires, bascules, en particulier les bascules D qui constituent un diviseur de fréquence, circuits séquentiels, et peuvent être décrits en langage Verilog)

Fabricants de FPGA

- Xilinx : la plateforme de développement est ISE, l'inventeur du FPGA ;

- Altera : la plateforme de développement est Quartus II, l'inventeur des dispositifs logiques programmables ;

- Actel : la plateforme de développement est Libero ;

- Lattice : la plateforme de développement est ISPLEVER ;

- Atmel