FPGA, kurz für Field Programmable Gate Array, ist eine rekonfigurierbare Hardware-Architektur. Mit anderen Worten handelt es sich um einen Chip, der so programmiert werden kann, dass er seine interne Struktur verändert. FPGAs werden seit vielen Jahren als Ersatz für anwendungsspezifische Chips (ASICs) in geringen Stückzahlen eingesetzt.

Grundlegende Struktur eines FPGA

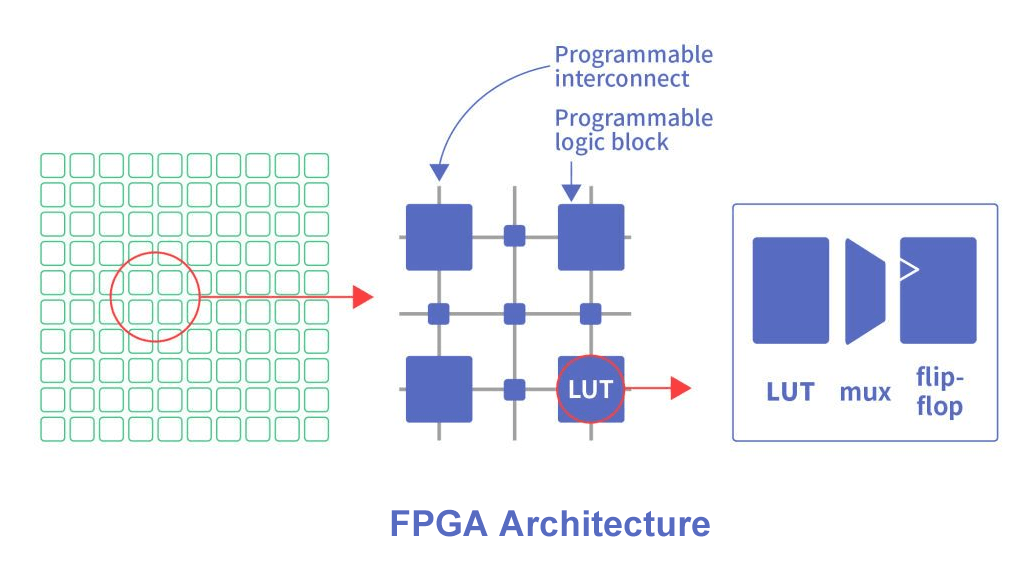

Die FPGA-Architektur umfasst im Wesentlichen vier Teile: konfigurierbare Logikblöcke (CLB), Ein- und Ausgangsblöcke (IOB), interne Verdrahtung (Interconnect) und andere eingebettete Einheiten. Die interne Struktur des FPGA-Bausteins ist unten dargestellt.

Konfigurierbarer Logikblock (CLB)

CLB ist die grundlegende Logikeinheit eines FPGA. Die tatsächliche Anzahl und die Eigenschaften variieren von Gerät zu Gerät, aber jedes CLB enthält eine konfigurierbare Schaltmatrix mit 4 oder 6 Eingängen, mehrere Auswahlschaltungen (Multiplexer usw.) und Flipflops.

Eingabe- und Ausgabeblock (IOB)

FPGAs unterstützen viele I/O-Standards und sind daher eine ideale Schnittstellenbrücke für Systemdesigns. Die I/Os im FPGA sind nach Bänken gruppiert, wobei jede Bank unabhängig voneinander verschiedene I/O-Standards unterstützen kann. Derzeit bieten die fortschrittlichsten FPGAs mehr als zehn I/O-Bänke, die eine flexible I/O-Unterstützung ermöglichen.

Interne Verkabelung (Verbindung)

Die CLBs sorgen für die logische Leistung, und das flexible Interconnect-Routing ist für die Weiterleitung der Signale zwischen den CLBs und den I/Os zuständig. Es gibt verschiedene Arten von Routing, von dedizierten CLB-Interconnects (kurze Drahtressourcen) über horizontale und vertikale Hochgeschwindigkeits-Langdrahtverbindungen (Langdrahtressourcen) innerhalb des Bausteins bis hin zu globalem Low-Skew-Routing für Takte und andere globale Signale (globale dedizierte Routing-Ressourcen).

Eingebettete Einheiten

Zu den eingebetteten Hardcore-Einheiten gehören RAM, DSP, DCM (Digital Clock Management Module) und andere spezifische Schnittstellen-Hardcores usw.

FPGA-Funktionen

- Durch die Verwendung von FPGA zum Entwerfen von ASIC-Schaltungen ist der Zyklus kurz, die Kosten sind gering, das Risiko ist gering und die Qualität ist stabil.

- FPGA nutzt die schnelle CHMOS-Technologie mit geringem Stromverbrauch.

- FPGA-Architektur, flexible Logikeinheit, hohe Integration, breites Anwendungsspektrum.

- FPGA vereint die Vorteile von PLD und allgemeinen Gate-Arrays und ermöglicht die Realisierung groß angelegter Schaltungen.

- Eine Neuprogrammierung vor Ort ist möglich, und die späteren Wartungskosten sind gering.

- FPGA ist ein paralleles Rechensystem, das gleichzeitig multifunktionale Anforderungen erfüllen kann.

Wie funktioniert FPGA?

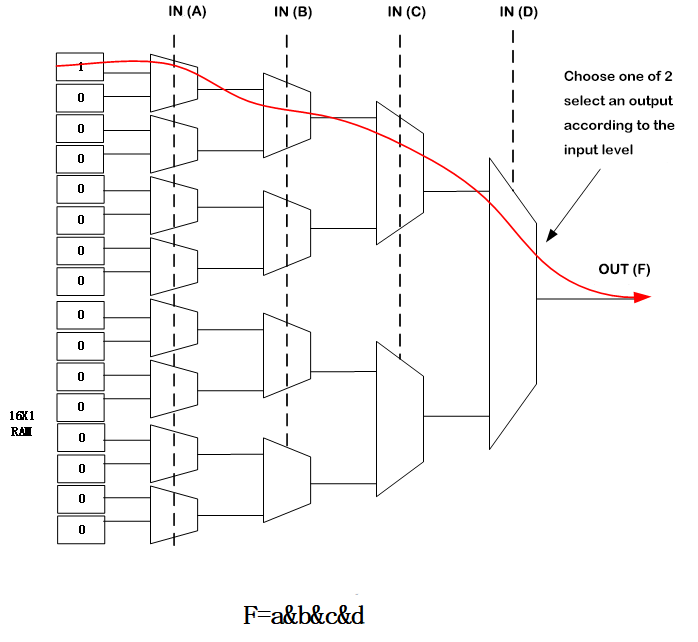

FPGA implementiert Logikfunktionen, indem es Programmierdaten in interne statische Speichereinheiten lädt. Der in der Speichereinheit gespeicherte Wert bestimmt die Logikfunktion der Logikeinheit und den Verbindungsmodus zwischen den einzelnen Logikeinheitsmodulen oder zwischen dem Modul und der E/A und bestimmt schließlich die realisierte FPGA-Funktion. FPGA verwendet eine kleine Nachschlagetabelle, um kombinatorische Logik zu implementieren. Jede Nachschlagetabelle ist mit dem Eingang eines D-Flipflops verbunden, und das D-Flipflop wird verwendet, um andere Logikschaltungen oder E/A anzusteuern, wodurch eine kombinierte Logikfunktion gebildet und die grundlegende Logikeinheit des sequentiellen Logikmoduls realisiert wird. Diese Module sind durch Metalldrähte miteinander oder mit dem E/A-Modul verbunden.

Hier ist ein einfaches Beispiel, um das Prinzip des FPGA zu erklären:

Wie in der obigen Abbildung gezeigt, konfigurieren wir 16bitRAM als 0000000000000001, und diese Schaltung entspricht F=A&B&C&D;

Nur wenn A=B=C=D=1, ist F=1, andernfalls ist F=0.

„0000000000000001“ Diese Zahlenfolge ist eine FPGA-Programmierung.

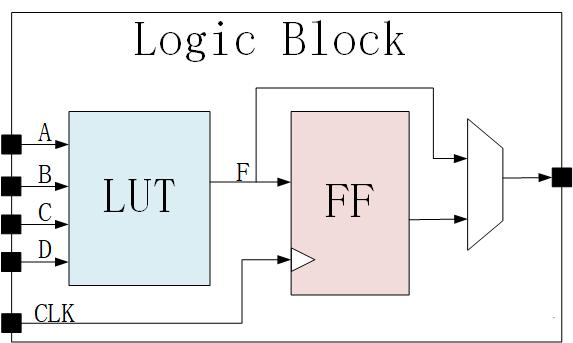

Logikblock des FPGA

In FPGA gibt es einen Fachbegriff namens LUT, Lookup Table (Nachschlagetabelle).

Die LUT bildet die grundlegendste Einheit eines jeden FPGA.

Die LUT kann nur digitale kombinatorische Logik implementieren, daher wird ein Register-Flipflop (ff) hinzugefügt, um das Speichern von Daten zu realisieren.

Wie in der folgenden Abbildung dargestellt: LUT+Register bilden die Grundstruktur moderner FPGAs.

FPGA-Entwicklungsprozess

Der FPGA-Entwicklungsprozess ist der Prozess der Verwendung von EDA-Entwicklungssoftware und Programmierwerkzeugen zur Entwicklung von FPGA-Chips. Der Entwicklungsprozess von FPGA ist im Allgemeinen in der folgenden Abbildung dargestellt und umfasst wichtige Schritte wie Funktionsdefinition/Geräteauswahl, Designeingabe, Funktionssimulation, Logiksynthese, Layout und Routing sowie Implementierung, Programmierung und Debugging.

Funktionsdefinition/Geräteauswahl:

Bevor das FPGA-Designprojekt beginnt, müssen die Systemfunktionen definiert und die Module aufgeteilt werden. Darüber hinaus können je nach Aufgabenanforderungen, wie z. B. der Funktion und Komplexität des Systems, der Arbeitsgeschwindigkeit und den Ressourcen, Kosten und Verbindungen des Geräts selbst, Kompromisse zwischen verschiedenen Aspekten wie der Leistung eingegangen und das geeignete Designschema und der geeignete Gerätetyp ausgewählt werden.

Design-Input:

Design-Input bezieht sich auf die Verwendung einer Hardwarebeschreibungssprache, um das entworfene System oder die Schaltung in Code auszudrücken. Die am häufigsten verwendete Hardwarebeschreibungssprache ist Verilog HDL.

Funktionssimulation:

Funktionssimulation bezieht sich auf die Überprüfung der Logikfunktion der vom Benutzer entworfenen Schaltung vor der Logiksynthese. Vor der Simulation muss eine Testplattform aufgebaut und Teststimuli vorbereitet werden. Die Simulationsergebnisse generieren Berichtsdateien und geben Signalwellenformen aus, anhand derer die Veränderungen der Signale jedes Knotens beobachtet werden können. Wenn Fehler gefunden werden, kehren Sie zum Entwurf zurück, um das Logikdesign zu überarbeiten. Zu den gängigen Simulationswerkzeugen gehören ModelSim von Model Tech, VCS von Sysnopsys und andere Software.

Logische Synthese:

Die sogenannte Synthese besteht darin, die Beschreibung der höheren Abstraktionsebene in die Beschreibung der niedrigeren Ebene umzuwandeln. Die synthetische Optimierung optimiert die generierten logischen Verbindungen entsprechend den Zielen und Anforderungen und macht das hierarchische Design planar, damit es von der FPGA-Layout- und Routing-Software implementiert werden kann. Was die aktuelle Ebene betrifft, bezieht sich die umfassende Optimierung auf die Kompilierung der Designeingaben zu einer logisch verbundenen Netzliste, die aus grundlegenden Logikeinheiten wie UND-Gattern, ODER-Gattern, NICHT-Gattern, RAMs und Flipflops besteht, anstatt aus realen Schaltungen auf Gate-Ebene.

Layout und Umsetzung:

Layout und Routing können als die Verwendung von Implementierungswerkzeugen verstanden werden, um die Logik auf die Ressourcen der Zielgerätestruktur abzubilden, das optimale Layout der Logik zu bestimmen, die durch Logik und Ein- und Ausgangsfunktionen verbundenen Verdrahtungskanäle auszuwählen und entsprechende Dateien (wie Konfigurationsdateien und zugehörige Berichte) zu generieren. Die Implementierung besteht darin, die durch die Synthese erzeugte Logik-Netzliste für einen bestimmten FPGA-Chip zu konfigurieren. Da nur der FPGA-Chip-Hersteller die Chipstruktur am besten kennt, müssen für Layout und Routing die vom Chip-Entwickler bereitgestellten Werkzeuge verwendet werden.

Programmierung Debugging:

Der letzte Schritt im Design ist die Programmierung und Fehlerbehebung. Die Chip-Programmierung bezieht sich auf die Erstellung von Datendateien (Bitstromdateien, Bitstream Generaon) und das Laden der Programmierdaten in den FPGA-Chip; danach kann der Board-Test durchgeführt werden. Laden Sie schließlich die FPGA-Datei (z. B. .bit-Datei) vom Computer auf den FPGA-Chip auf der Platine herunter.

FPGA vs. CPU und GPU

Sowohl CPUs als auch GPUs folgen der von Neumann-Architektur mit Befehlsdecodierung und gemeinsamem Speicher. Im Gegensatz dazu haben FPGAs eine grundlegend andere Architektur, die nicht auf Befehlen basiert und keinen gemeinsamen Speicher benötigt. Die folgende Tabelle zeigt ihre Unterschiede:

| Feature | FPGA | CPU | GPU |

|---|---|---|---|

| Architecture | Reconfigurable logic | Von Neumann | Von Neumann |

| Instruction | No instructions | Instructions | Instructions |

| Shared Memory | No shared memory | Arbitration and shared memory | Arbitration and shared memory |

| Parallel Processing | Pipeline and data parallelism | Data parallelism | Data parallelism |

| Flexibility | Reprogrammable | Fixed functionality | Fixed functionality |

| Computational Power | Suitable for complex tasks | General-purpose computing | Parallel computing and vector processing |

| Latency | Low latency | Medium latency | Relatively high latency |

| Power Consumption | High power consumption | Medium power consumption | High power consumption |

| Application Areas | Electronics, communication, embedded systems | General-purpose computing | Graphics processing, scientific computing |

Erforderliche Fähigkeiten für FPGA-Ingenieure

- Die Sprache Verilog und ihre Beziehung zu Hardwareschaltungen

- Entwicklungswerkzeuge (beherrscht Synplify, Vivodo, ISE, Modelsim)

- Vertraut mit dem FPGA-Entwurfsprozess (Simulation, Synthese, Layout und Routing, Timing-Analyse)

- Kenntnisse in der Ressourcenschätzung (insbesondere der Schätzung von Slice, LUT, RAM und anderen Ressourcen)

- Kenntnisse grundlegender Konzepte (z. B. Setup-Zeit, Hold-Zeit, Flussberechnung, Verzögerungszeitberechnung, Wettbewerbsrisiko, Methoden zur Beseitigung von Störungen usw.)

- Digitale Schaltungen (Kombinationsschaltungen, Flipflops, insbesondere D-Flipflops, die einen Frequenzteiler bilden, sequentielle Schaltungen, die in der Sprache Verilog beschrieben werden können)

FPGA-Hersteller

- Xilinx: Die Entwicklungsplattform ist ISE, der Erfinder von FPGA.

- Altera: Die Entwicklungsplattform ist Quartus II, der Erfinder programmierbarer Logikbausteine.

- Actel: Die Entwicklungsplattform ist Libero.

- Lattice: Die Entwicklungsplattform ist ISPLEVER.

- Atmel