Im Zeitalter von KI-Servern, 5G-Smartphones und autonomen Fahrzeugen hängt die Leistungsfähigkeit eines Chips entscheidend von seinem „Nervensystem“ ab – dem IC-Substrat. Da die Schaltungsdichte an ihre physikalischen Grenzen stößt, bestimmt die Wahl des Fertigungsprozesses die Signalintegrität und Zuverlässigkeit des Endprodukts.

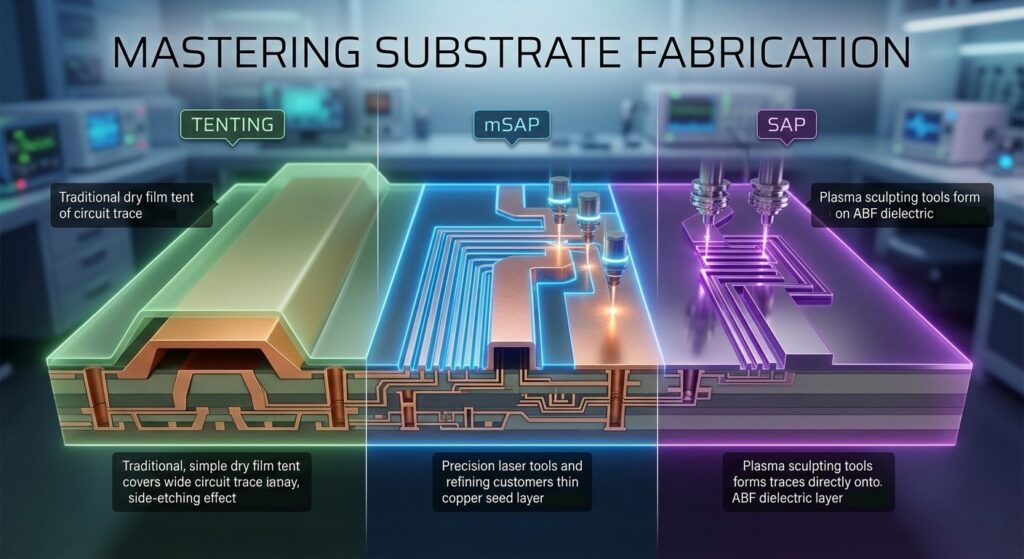

Heute dominieren drei primäre „Formungswerkzeuge“ die Branche: Tenting (subtraktiv), mSAP (modifizierter semi-additiver Prozess) und SAP (semi-additiver Prozess). Dieser Leitfaden erläutert ihre technischen Mechanismen, Vor- und Nachteile sowie ihre Rolle im modernen Elektronik-Ökosystem.

1. Tenting-Verfahren (subtraktive Methode)

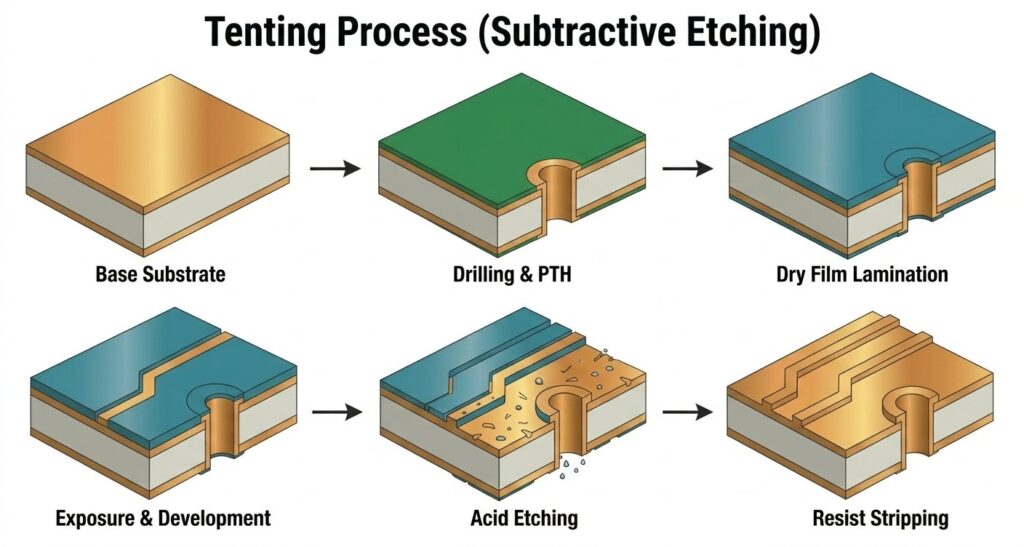

Das Tenting-Verfahren ist die traditionellste und am weitesten verbreitete Technologie zur Leiterbahnbildung in der Leiterplatten- und Substratindustrie mit geringer Dichte. Sein Grundprinzip lautet „abdecken und entfernen“ – ähnlich wie beim Schnitzen eines Siegels aus einem Steinblock.

So funktioniert es: Ausgangspunkt ist ein kupferkaschiertes Laminat (CCL) mit einer dicken Kupferfolie (in der Regel > 12 µm). Ein Trockenfilm (Fotolack) bedeckt die vorgesehenen Leiterbahnbereiche wie ein „Zelt“ über den Löchern (daher der Name). Das ungeschützte Kupfer wird dann chemisch weggeätzt.

Das Problem (Seitenätzung): Da beim Ätzen Kupfer gleichzeitig vertikal und horizontal entfernt wird, entsteht ein „trapezförmiger“ Querschnitt. Diese „Seitenätzung“ begrenzt die Präzision der Leiterbahnbreite und des Abstands ($L/S$) auf etwa $30\mu m/30\mu m$.

Am besten geeignet für: Standard-Unterhaltungselektronik, Leiterplatten für die Automobilindustrie und traditionelle Wire-Bond-BGA-Substrate (WB-BGA).

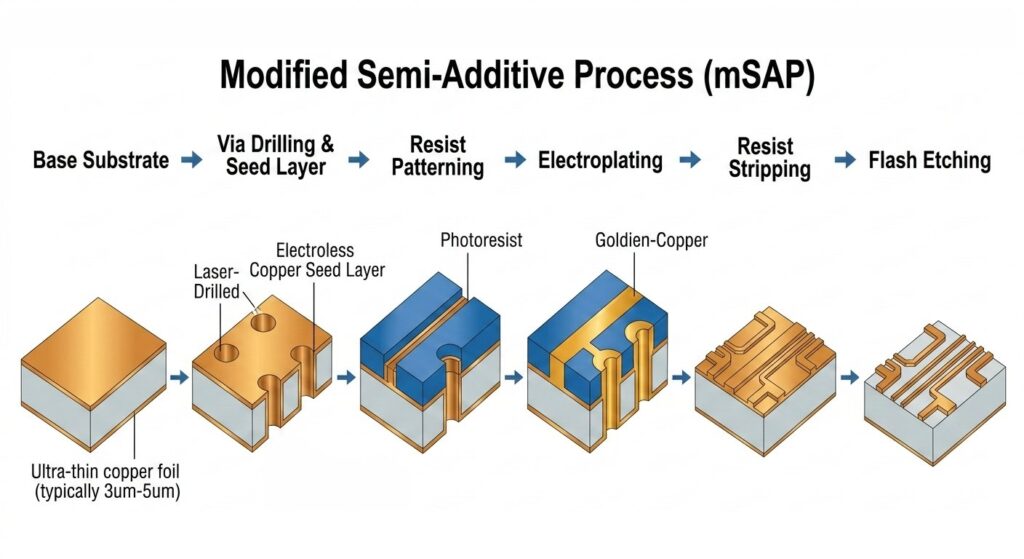

2. mSAP (modifiziertes semi-additives Verfahren)

Mit der steigenden Pin-Anzahl und der zunehmenden Signalgeschwindigkeit entwickelte sich mSAP zur Brücke zwischen herkömmlichen Leiterplatten und High-End-IC-Substraten. Derzeit ist es die gängigste Wahl für FCBGA-Substrate, die in Netzwerkchips und Premium-Smartphone-Prozessoren zum Einsatz kommen.

So funktioniert es: Anstelle von dickem Kupfer beginnt mSAP mit einer ultradünnen Kupferbasis (in der Regel 3–5 µm) oder einer chemisch abgeschiedenen „Keimschicht“. Die Schaltkreise werden durch selektives Galvanisieren auf die gewünschte Dicke „aufgebracht“.

Der Vorteil: Nach dem Plattieren entfernt ein schnelles „Flash-Ätzen“ die ultradünne Basisschicht. Da die Basis so dünn ist, ist die Ätzzeit minimal, was zu nahezu senkrechten, rechteckigen Schaltungswänden mit $L/S$-Werten von bis zu $10\mu m/10\mu m$führt.

Am besten geeignet für: High-End-Smartphone-APs (Apple A-Serie, Snapdragon), Chip-Scale-Packaging (FCCSP) und substratähnliche Leiterplatten (SLP).

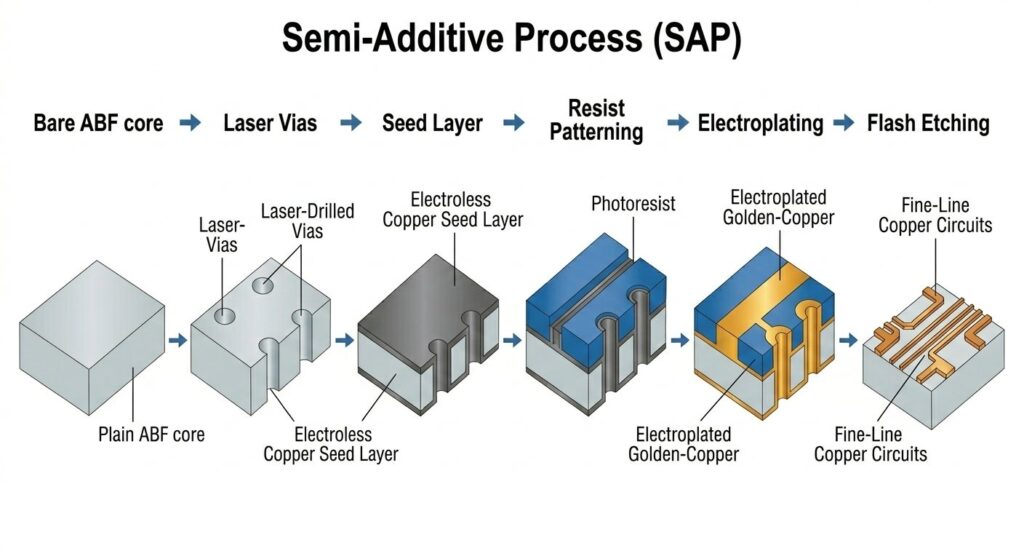

3. SAP (semi-additives Verfahren)

SAP stellt den Gipfel der Schaltungspräzision dar und wird oft als „verfeinerte“ Version von mSAP bezeichnet. Dabei wird vollständig auf Kupferfolie verzichtet und stattdessen auf „reine Addition“ gesetzt.

So funktioniert es: Es wird ein kupferfreies dielektrisches Material verwendet, insbesondere ABF (Ajinomoto Build-up Film). Eine mikroskopisch kleine „Keimschicht“ ($< 1\mu m$) wird chemisch auf die glatte Oberfläche aufgebracht, gefolgt von selektivem Plattieren, um die Schaltkreise aufzubauen.

Der Vorteil: Da die Keimschicht praktisch nicht vorhanden ist, hat das Ätzen keinerlei Einfluss auf die Schaltungsmorphologie. Dies ermöglicht extreme Präzision ($L/S < 10\mu m$) und eine hervorragende Impedanzkontrolle für Hochgeschwindigkeitssignale.

Am besten geeignet für: Hochleistungsrechner (HPC), KI-Beschleuniger (Nvidia H100) und fortschrittliche Verpackungstechnologien wie CoWoS und HBM.

4. Vergleichstabelle: Tenting vs. mSAP vs. SAP

| Feature | Tenting | mSAP | SAP |

|---|---|---|---|

| Core Principle | Subtractive: Etch away thick copper foil | Additive: Plate over ultra-thin copper base | Pure Additive: Seed layer on copper-free dielectric |

| Line Precision (L/S) | > 30μm | 10μm - 30μm | < 10μm |

| Cross-section Shape | Trapezoidal (Side-etching) | Near-Rectangular | Perfectly Rectangular |

| Base Material | Standard CCL | Ultra-thin copper foil | ABF (Ajinomoto Build-up Film) |

| Primary Application | Consumer PCBs / Motherboards | Smartphone AP / High-end HDI | AI Accelerators / CPU / GPU Substrates |

| Cost & Maturity | Low Cost / Highly Mature | Medium-High / Mainstream High-end | Very High / Cutting-edge |

Ausblick: Die Zukunft der Fertigung

Die Branche tendiert zu einem „hybriden“ Ansatz, um Kosten und Leistung in Einklang zu bringen – dabei wird „Tenting“ für die Kernschichten und mSAP/SAP für die hochdichten Außenschichten eingesetzt. Da die Nachfrage nach KI die Grenzen des Moore’schen Gesetzes immer weiter verschiebt, werden sich neue Technologien wie Glassubstrate und eingebettete Chips parallel zu diesen drei grundlegenden Verfahren weiterentwickeln.

Das Verständnis der Feinheiten dieser Fertigungsmethoden ist der erste Schritt zur Beherrschung der komplexen Landschaft moderner Chip-Verpackung und Hardware-Sicherheit.