O que é Dual Inline Package?

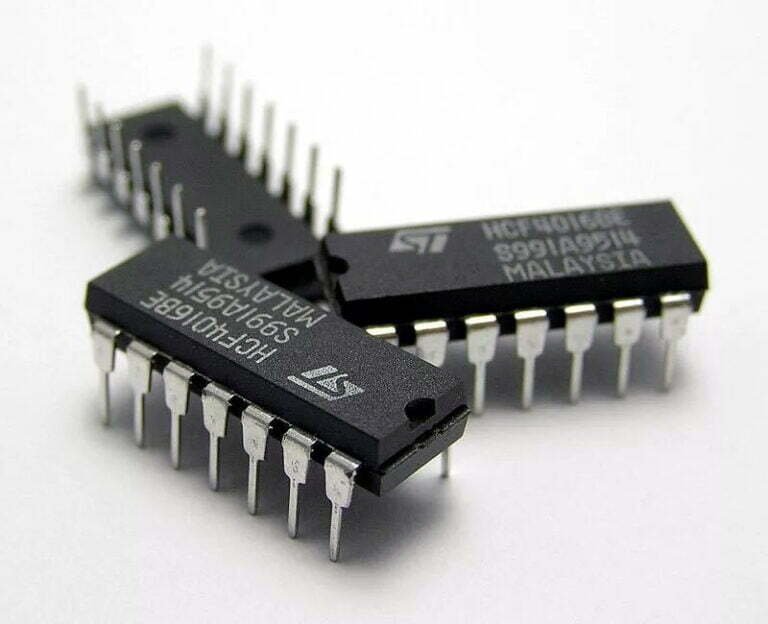

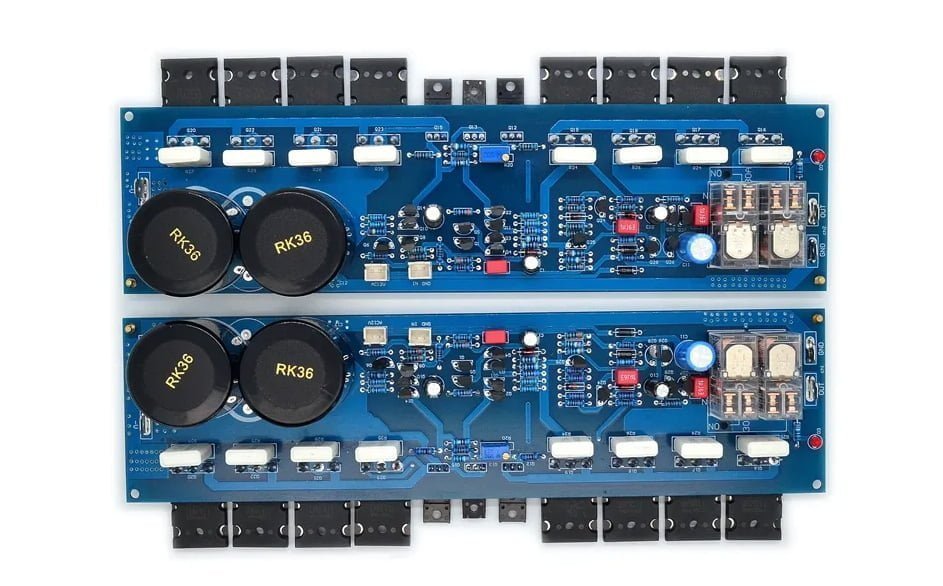

DIP, ou pacote dual inline, é um tipo de embalagem de circuito integrado (IC) que apresenta duas fileiras paralelas de pinos metálicos, chamados pinos dual inline, em ambos os lados de um circuito retangular. Os pacotes DIP podem ser soldados em uma placa de circuito impresso ou inseridos em um soquete DIP. Os chips DIP têm duas fileiras de pinos e requerem inserção em um soquete DIP em um portador de chip ou podem ser soldados diretamente em uma placa de circuito impresso. Os pacotes DIP têm sido amplamente utilizados para ICs, interruptores DIP, LEDs, displays de sete segmentos, displays de gráfico de barras e relés.

Tipos de pacotes dual inline

- DIP cerâmico (CDIP): melhor desempenho elétrico e maior resistência ao calor, umidade e choques.

- DIP plástico (PDIP): consiste em duas fileiras paralelas de pinos, fornece isolamento e proteção para os ICs.

- DIP plástico retrátil (SPDIP): apresenta um pequeno espaçamento entre os pinos de 0,07 pol. (1,778 mm).

- DIP fino (SDIP): vem com uma largura de 7,62 mm e uma distância central entre os pinos de 2,54 mm.

História do Pacote DIP

Invenção do DIP

O primeiro componente DIP foi inventado por Bryant Buck Rogers, da Fairchild Semiconductor, em 1964. Ele tinha 14 pinos e era bastante semelhante às embalagens DIP atuais. A forma retangular dos componentes DIP aumentou a densidade dos componentes nas placas de circuito em comparação com os componentes redondos anteriores. Os componentes DIP também eram adequados para equipamentos de montagem automatizados, com dezenas a centenas de ICs em uma placa de circuito soldada por máquinas de solda por onda e testada por equipamentos de teste automatizados, exigindo apenas uma pequena quantidade de trabalho manual. O tamanho dos componentes DIP é, na verdade, muito maior do que os circuitos integrados dentro deles.

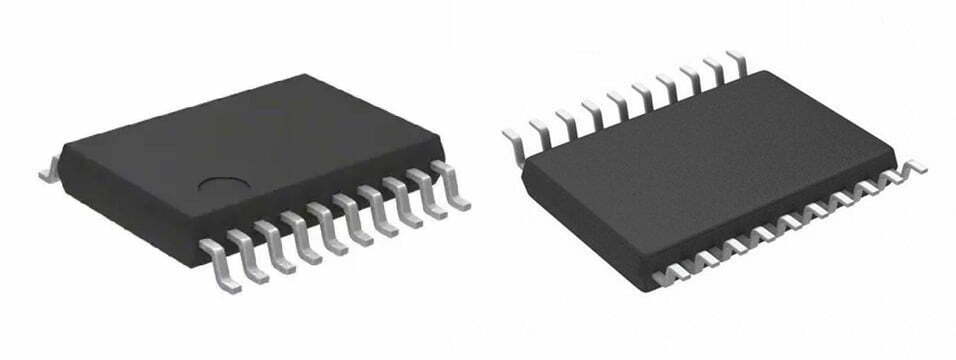

De DIP para SMT

A embalagem DIP era a principal tendência da indústria microeletrônica nas décadas de 1970 e 1980. Seu uso diminuiu gradualmente no início do século XXI e foi substituído pela tecnologia de montagem em superfície (SMT), como PLCC e SOIC. As características dos componentes SMT são adequadas para a produção em massa, mas menos convenientes para a produção de protótipos de circuitos. Como alguns novos componentes oferecem apenas produtos de embalagem SMT, muitas empresas produzem adaptadores que convertem componentes SMD em embalagens DIP, permitindo que os ICs SMT sejam colocados no adaptador e conectados a placas de ensaio ou outros componentes de inserção direta em uma placa de protótipo de circuito (como uma placa perfurada), assim como os componentes DIP.

O declínio dos componentes DIP

Para componentes programáveis, como EPROM ou GAL, os componentes embalados em DIP ainda são populares por um tempo, pois são convenientes para gravar dados por meio de equipamentos externos de gravação (os componentes embalados em DIP podem ser inseridos diretamente no soquete DIP correspondente do equipamento de gravação). No entanto, com a popularidade da tecnologia de programação em linha (ISP), os benefícios da fácil programação dos componentes embalados em DIP não são mais importantes. Na década de 1990, componentes com mais de 20 pinos ainda podem ter produtos embalados em DIP. No século XXI, muitos novos componentes programáveis são embalados em SMT, e os produtos em embalagem DIP não estão mais disponíveis.

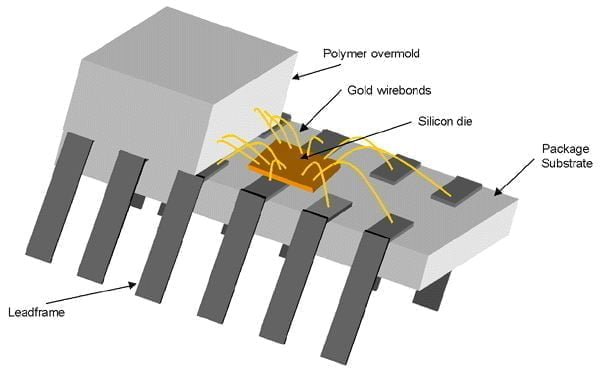

Estrutura DIP

O pacote DIP consiste em uma estrutura de chumbo, um substrato de pacote, um chip de silício, fios de ouro e um revestimento de polímero.

O leadframe é uma estrutura metálica fina que sustenta o chip de silício e fornece conexões elétricas com o mundo exterior. O substrato da embalagem é uma peça fina de material isolante que sustenta e conecta eletricamente o leadframe e o chip de silício.

O chip de silício é o coração do pacote DIP, contendo os circuitos eletrônicos que executam a função desejada. Os fios de ouro conectam o chip de silício ao leadframe, permitindo que os sinais elétricos fluam entre o chip de silício e o mundo exterior.

O sobremoldado de polímero é um revestimento protetor que cobre o leadframe, o substrato da embalagem, o chip de silício e as ligações de fio de ouro. Ele fornece proteção mecânica, impede a entrada de umidade e melhora a confiabilidade geral da embalagem DIP.

Prós e contras do pacote Dual Inline

Pros

- Simples e de baixo custo.

- Fácil de fabricar e montar para produção em massa.

- Compatível com técnicas de montagem através de orifícios.

- Boa dissipação de calor.

- Fácil de substituir sem danificar os componentes circundantes.

Contras

- Os DIPs ocupam mais espaço na placa de circuito em comparação com outros tipos de embalagem, como SMT.

- Eles não são adequados para aplicações de alta densidade, pois o espaçamento entre os pinos é limitado.

- Os DIPs não são tão resistentes quanto outros tipos de embalagem e podem ser danificados por tensão mecânica, como dobras ou torções.

- Eles também podem ser afetados por flutuações de temperatura, o que pode causar a expansão ou contração dos pinos e, potencialmente, levar à falha da junta de solda.

Pinos do DIP

Os componentes DIP (dual in-line package) têm dimensões padrão que cumprem as normas JEDEC. A distância entre dois pinos (pitch) é de 0,1 polegadas (2,54 mm). O espaçamento entre linhas, que se refere à distância entre duas linhas de pinos, depende do número de pinos no pacote. Os espaçamentos entre linhas mais comuns são 0,3 polegadas (7,62 mm) ou 0,6 polegadas (15,24 mm). Outros espaçamentos menos comuns são 0,4 polegadas (10,16 mm) ou 0,9 polegadas (22,86 mm). Existem também alguns pacotes com um passo de 0,07 polegadas (1,778 mm) e espaçamentos entre linhas de 0,3 polegadas, 0,6 polegadas ou 0,75 polegadas.

Os pacotes DIP usados na antiga União Soviética e na Europa Oriental são semelhantes aos padrões JEDEC, mas o passo é de 2,5 milímetros, baseado no sistema métrico, em vez de 0,1 polegadas (2,54 mm) usado no sistema imperial.

O número de pinos em um pacote DIP é sempre par. Se o espaçamento entre linhas for de 0,3 polegadas, o número mais comum de pinos é de 8 a 24, e às vezes há pacotes com 4 ou 28 pinos. Se o espaçamento entre as fileiras for de 0,6 polegadas, os números mais comuns de pinos são 24, 28, 32 ou 40, e também existem pacotes com 36, 48 ou 52 pinos. O número máximo de pinos para pacotes DIP comumente usados é 64, como no caso das CPUs Motorola 68000 e Zilog Z180.

Quando o entalhe de identificação de um componente está voltado para cima, o pino superior esquerdo é o pino 1 e os outros pinos são numerados no sentido anti-horário. Às vezes, o pino 1 também é marcado com um ponto. Por exemplo, em um IC DIP14, quando o entalhe de identificação está voltado para cima, os pinos do lado esquerdo são numerados de 1 a 7 de cima para baixo, e os pinos do lado direito são numerados de 8 a 14 de baixo para cima.

Características elétricas dos componentes DIP

Os componentes DIP (dual in-line package) têm características elétricas específicas que determinam seu desempenho e confiabilidade. A seguir estão algumas das especificações elétricas mais importantes para componentes DIP:

- Vida útil elétrica: Cada interruptor é testado para 2000 ciclos a 24 VCC e 25 mA.

- Corrente nominal para comutação pouco frequente: 100 mA, tensão suportada de 50 VCC.

- Corrente nominal para comutação frequente: 25 mA, tensão suportada de 24 VCC.

- Resistência de contato: (a) valor inicial máximo de 50 mΩ; (b) valor máximo após teste de 100 mΩ.

- Resistência de isolamento: Mínimo de 100 mΩ a 500 VCC.

- Tensão suportável: 500 VCA/1 minuto.

- Capacitância entre eletrodos: máximo de 5 pF.

- Circuito: Estão disponíveis configurações unipolar, simples (SPST) ou bipolar, dupla (DPDT).

Essas características elétricas são cruciais para garantir o desempenho ideal e a confiabilidade dos componentes DIP. Os fabricantes devem aderir aos padrões JEDEC para garantir que seus componentes atendam às especificações exigidas. Ao projetar circuitos que usam componentes DIP, é importante considerar essas características elétricas para garantir que o circuito funcione de maneira adequada e segura.

DIP vs SOIC

DIP (pacote dual in-line) e SOIC (circuito integrado de contorno pequeno) são dois tipos de embalagem comumente usados para circuitos integrados (ICs). Ambos os tipos têm suas vantagens e desvantagens, e a escolha entre eles depende dos requisitos específicos da aplicação. A tabela a seguir resume as principais diferenças entre DIP e SOIC.

| Feature | DIP | SOIC |

|---|---|---|

| Pin Count | Up to 64 pins | Up to 48 pins |

| Pitch | 0.1 inches (2.54 mm) | 0.5 mm to 1.27 mm |

| Size | Larger than SOIC | Smaller than DIP |

| Through-Hole Mounting | Yes | No |

| Surface Mounting | No | Yes |

| Lead Count | Even | Even or Odd |

| Lead Position | Inline | Gull-wing and J-lead |

| Electrical Performance | Good | Better than DIP |

| Cost | Lower than SOIC | Higher than DIP |

Os pacotes DIP têm sido amplamente utilizados há muitos anos, mas seu tamanho e montagem através de orifícios os tornam menos adequados para aplicações modernas de tecnologia de montagem em superfície (SMT). Os pacotes SOIC, por outro lado, são menores, mais leves e mais adequados para montagem SMT. A posição dos terminais dos pacotes SOIC também permite um melhor desempenho elétrico, pois os terminais têm caminhos mais curtos até o IC.

Em termos de custo, os pacotes DIP são geralmente mais baratos do que os pacotes SOIC. No entanto, a diferença de custo pode ser compensada pelas vantagens dos pacotes SOIC em termos de desempenho, tamanho e facilidade de montagem.

Em resumo, os pacotes DIP são adequados para aplicações que requerem menor número de pinos e montagem através de orifícios, enquanto os pacotes SOIC são mais adequados para aplicações que requerem maior número de pinos, tamanho menor e tecnologia de montagem em superfície.