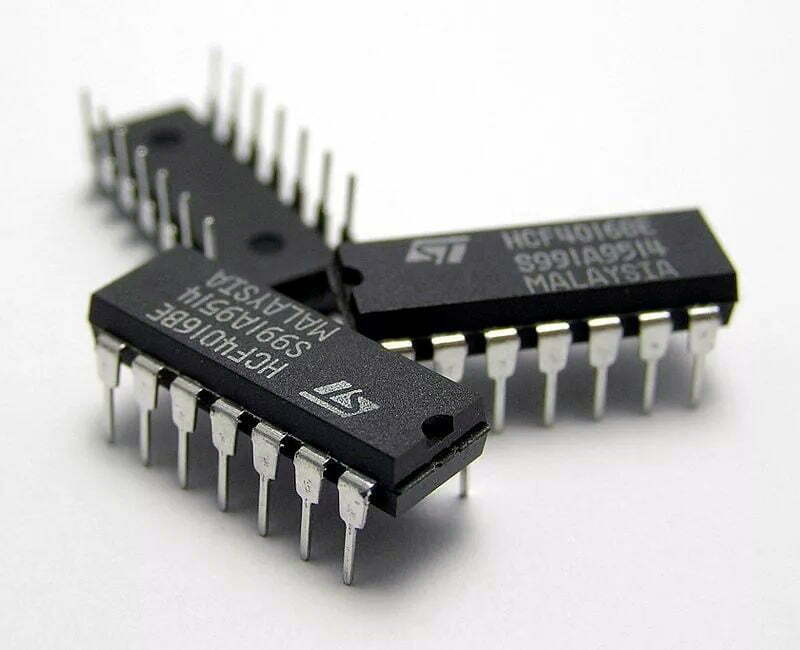

¿Qué es un paquete dual en línea?

DIP, o paquete dual en línea, es un tipo de encapsulado de circuito integrado (IC) que cuenta con dos filas paralelas de pines metálicos, llamados pines duales en línea, a cada lado de un circuito de forma rectangular. Los paquetes DIP se pueden soldar a una placa de circuito impreso o insertarse en un zócalo DIP. Los chips DIP tienen dos filas de pines y requieren su inserción en un zócalo DIP en un portachips o se pueden soldar directamente a una placa de circuito impreso. Los encapsulados DIP se han utilizado ampliamente para circuitos integrados, interruptores DIP, LED, pantallas de siete segmentos, pantallas de gráficos de barras y relés.

Tipos de paquetes duales en línea

- DIP cerámico (CDIP): mejor rendimiento eléctrico y mayor resistencia al calor, la humedad y los golpes.

- DIP de plástico (PDIP): consta de dos filas paralelas de pines, proporciona aislamiento y protección para los circuitos integrados.

- DIP de plástico retráctil (SPDIP): se caracteriza por un pequeño paso de pines de 0,07 pulgadas (1,778 mm).

- DIP delgado (SDIP): tiene una anchura de 7,62 mm y una distancia entre pines de 2,54 mm.

Historia del paquete DIP

Invención del DIP

El primer componente DIP fue inventado por Bryant Buck Rogers, de Fairchild Semiconductor, en 1964. Tenía 14 pines y era muy similar al encapsulado DIP actual. La forma rectangular de los componentes DIP aumentó la densidad de los componentes en las placas de circuitos en comparación con los componentes redondos anteriores. Los componentes DIP también eran adecuados para equipos de montaje automatizados, con docenas o cientos de circuitos integrados en una placa de circuitos soldados por máquinas de soldadura por ola y probados por equipos de prueba automatizados, lo que requería solo una pequeña cantidad de trabajo manual. El tamaño de los componentes DIP es en realidad mucho mayor que los circuitos integrados que contienen.

De DIP a SMT

El encapsulado DIP fue la corriente dominante en la industria microelectrónica en las décadas de 1970 y 1980. Su uso disminuyó gradualmente a principios del siglo XXI y fue sustituido por el encapsulado de tecnología de montaje superficial (SMT), como PLCC y SOIC. Las características de los componentes SMT son adecuadas para la producción en masa, pero menos convenientes para la producción de prototipos de circuitos. Dado que algunos componentes nuevos solo ofrecen productos de encapsulado SMT, muchas empresas fabrican adaptadores que convierten los componentes SMD en encapsulados DIP, lo que permite colocar los circuitos integrados SMT en el adaptador y conectarlos a placas de pruebas u otros componentes de inserción directa en una placa prototipo de circuito (como una placa perforada), al igual que los componentes DIP.

El declive de los componentes DIP

En el caso de los componentes programables, como EPROM o GAL, los componentes con encapsulado DIP siguen siendo populares durante un tiempo, ya que resultan cómodos para grabar datos mediante equipos de grabación externos (los componentes con encapsulado DIP se pueden insertar directamente en el zócalo DIP correspondiente del equipo de grabación). Sin embargo, con la popularidad de la tecnología de programación en línea (ISP), las ventajas de la fácil programación de los componentes con encapsulado DIP ya no son tan importantes. En la década de 1990, los componentes con más de 20 pines aún podían tener productos encapsulados en DIP. En el siglo XXI, muchos componentes programables nuevos se encapsulan en SMT, y los productos en encapsulado DIP ya no están disponibles.

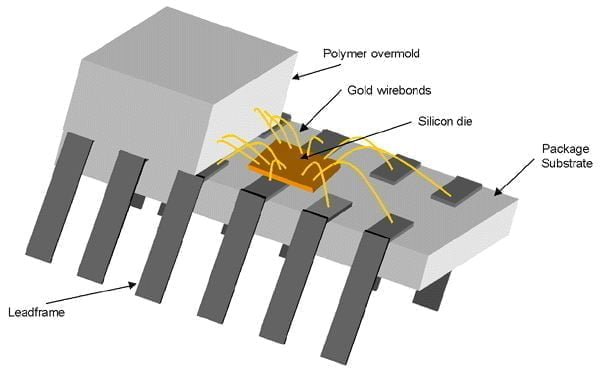

Estructura DIP

El paquete DIP consta de un marco de plomo, un sustrato de paquete, un chip de silicio, conexiones de hilo de oro y un recubrimiento de polímero.

El marco conductor es una estructura metálica delgada que sostiene el chip de silicio y proporciona conexiones eléctricas con el exterior. El sustrato del paquete es una pieza delgada de material aislante que soporta y conecta eléctricamente el marco conductor y el chip de silicio.

El chip de silicio es el corazón del paquete DIP, ya que contiene los circuitos electrónicos que realizan la función deseada. Los hilos de oro conectan el chip de silicio al marco conductor, lo que permite que las señales eléctricas fluyan entre el chip de silicio y el exterior.

El recubrimiento de polímero es una capa protectora que cubre el marco conductor, el sustrato del paquete, el chip de silicio y los hilos de oro. Proporciona protección mecánica, evita la entrada de humedad y mejora la fiabilidad general del paquete DIP.

Ventajas y desventajas del paquete dual en línea

Pros

- Sencillo y económico.

- Fácil de fabricar y montar para la producción en serie.

- Compatible con técnicas de montaje con orificios pasantes.

- Buena disipación del calor.

- Fácil de sustituir sin dañar los componentes circundantes.

Contras

- Los DIP ocupan más espacio en la placa de circuito impreso en comparación con otros tipos de encapsulado, como los SMT.

- No son adecuados para aplicaciones de alta densidad, ya que el espacio entre sus pines es limitado.

- Los DIP no son tan resistentes como otros tipos de encapsulados y pueden dañarse por esfuerzos mecánicos, como flexiones o torsiones.

- También pueden verse afectados por las fluctuaciones de temperatura, que pueden hacer que los pines se expandan o contraigan y provocar fallos en las juntas de soldadura.

Pines de DIP

Los componentes DIP (paquete dual en línea) tienen dimensiones estándar que cumplen con las normas JEDEC. La distancia entre dos pines (paso) es de 0,1 pulgadas (2,54 mm). El espaciado entre filas, que se refiere a la distancia entre dos filas de pines, depende del número de pines del paquete. Los espaciados entre filas más comunes son 0,3 pulgadas (7,62 mm) o 0,6 pulgadas (15,24 mm). Otros espaciados menos comunes son 0,4 pulgadas (10,16 mm) o 0,9 pulgadas (22,86 mm). También hay algunos paquetes con un paso de 0,07 pulgadas (1,778 mm) y espaciados entre filas de 0,3 pulgadas, 0,6 pulgadas o 0,75 pulgadas.

Los paquetes DIP utilizados en la antigua Unión Soviética y Europa del Este son similares a los estándares JEDEC, pero el paso es de 2,5 milímetros, que se basa en el sistema métrico, en lugar de 0,1 pulgadas (2,54 mm) utilizado en el sistema imperial.

El número de pines en un paquete DIP es siempre par. Si el espaciado entre filas es de 0,3 pulgadas, el número más común de pines es de 8 a 24, y a veces hay paquetes con 4 o 28 pines. Si el espaciado entre filas es de 0,6 pulgadas, los números más comunes de pines son 24, 28, 32 o 40, y también hay paquetes con 36, 48 o 52 pines. El número máximo de pines para los paquetes DIP de uso común es 64, como en el caso de las CPU Motorola 68000 y Zilog Z180.

Cuando la muesca identificativa de un componente está orientada hacia arriba, el pin superior izquierdo es el pin 1, y los demás pines se numeran en sentido antihorario. A veces, el pin 1 también está marcado con un punto. Por ejemplo, en un circuito integrado DIP14, cuando la muesca identificativa está orientada hacia arriba, los pines del lado izquierdo se numeran del 1 al 7 de arriba abajo, y los pines del lado derecho se numeran del 8 al 14 de abajo arriba.

Características eléctricas de los componentes DIP

Los componentes DIP (paquete dual en línea) tienen características eléctricas específicas que determinan su rendimiento y fiabilidad. A continuación se indican algunas de las especificaciones eléctricas más importantes para los componentes DIP:

- Vida eléctrica: cada interruptor se prueba durante 2000 ciclos a 24 VCC y 25 mA.

- Corriente nominal para conmutación poco frecuente: 100 mA, tensión soportada de 50 VCC.

- Corriente nominal para conmutación frecuente: 25 mA, tensión soportada de 24 VCC.

- Resistencia de contacto: (a) valor inicial máximo de 50 mΩ; (b) valor máximo tras la prueba de 100 mΩ.

- Resistencia de aislamiento: mínimo de 100 mΩ a 500 VCC.

- Tensión soportada: 500 VCA/1 minuto.

- Capacitancia entre electrodos: máximo de 5 pF.

- Circuito: Hay disponibles configuraciones de un polo y un tiro (SPST) o de dos polos y dos tiros (DPDT).

Estas características eléctricas son cruciales para garantizar el rendimiento y la fiabilidad óptimos de los componentes DIP. Los fabricantes deben cumplir con las normas JEDEC para garantizar que sus componentes cumplan con las especificaciones requeridas. Al diseñar circuitos que utilizan componentes DIP, es importante tener en cuenta estas características eléctricas para garantizar que el circuito funcione de manera adecuada y segura.

DIP frente a SOIC

DIP (paquete dual en línea) y SOIC (circuito integrado de contorno pequeño) son dos tipos de encapsulado comúnmente utilizados para circuitos integrados (IC). Ambos tipos tienen sus ventajas y desventajas, y la elección entre ellos depende de los requisitos específicos de la aplicación. La siguiente tabla resume las principales diferencias entre DIP y SOIC.

| Feature | DIP | SOIC |

|---|---|---|

| Pin Count | Up to 64 pins | Up to 48 pins |

| Pitch | 0.1 inches (2.54 mm) | 0.5 mm to 1.27 mm |

| Size | Larger than SOIC | Smaller than DIP |

| Through-Hole Mounting | Yes | No |

| Surface Mounting | No | Yes |

| Lead Count | Even | Even or Odd |

| Lead Position | Inline | Gull-wing and J-lead |

| Electrical Performance | Good | Better than DIP |

| Cost | Lower than SOIC | Higher than DIP |

Los paquetes DIP se han utilizado ampliamente durante muchos años, pero su tamaño y montaje con orificios pasantes los hacen menos adecuados para las aplicaciones modernas de tecnología de montaje superficial (SMT). Por otro lado, los paquetes SOIC son más pequeños, ligeros y adecuados para el montaje SMT. La posición de los conductores de los paquetes SOIC también permite un mejor rendimiento eléctrico, ya que los conductores tienen trayectorias más cortas hasta el IC.

En términos de coste, los paquetes DIP son generalmente menos costosos que los paquetes SOIC. Sin embargo, la diferencia de coste puede verse compensada por las ventajas de los paquetes SOIC en términos de rendimiento, tamaño y facilidad de montaje.

En resumen, los paquetes DIP son adecuados para aplicaciones que requieren un menor número de pines y montaje con orificios pasantes, mientras que los paquetes SOIC son más adecuados para aplicaciones que requieren un mayor número de pines, un tamaño más pequeño y tecnología de montaje superficial.