IC Failure Analysis

Comprehensive technical resource for semiconductor failure analysis methodologies, tools, and case studies

What is IC Failure Analysis?

Integrated Circuit (IC) Failure Analysis is a systematic process used to identify, isolate, and determine the root cause of semiconductor device failures. This critical engineering discipline combines advanced imaging techniques, electrical testing, and material science to resolve issues in integrated circuits across various industries.

Effective failure analysis improves product reliability, reduces manufacturing costs, accelerates time-to-market, and ensures compliance with industry standards. It plays a vital role in quality control, reliability engineering, and product improvement cycles.

Key Objectives of IC Failure Analysis

- Identify root causes of IC failures through systematic investigation

- Determine whether failures originate from design, manufacturing, or application

- Develop corrective actions to prevent future failures

- Validate reliability and performance of integrated circuits

- Support failure reporting and reliability data analysis

Technical Guides & Methodologies

Diagnostic Flowchart

Systematic approach from failure symptom to root cause identification

No Power/Output Failure Path

- 1 Check for ESD damage using SEM/EDS analysis

- 2 Verify solder joints with 3D X-ray inspection

- 3 Test for gate oxide breakdown using EMMI

- 4 Perform continuity testing with OBIRCH

- 5 Analyze package integrity with C-SAM

Intermittent Glitches Failure Path

- 1 Rule out BGA microcracks using C-SAM

- 2 Check for thermal stress with infrared imaging

- 3 Test for design-related latch-up through circuit simulation

- 4 Verify power distribution network integrity

EMMI Operation Guide

Step-by-step workflow for Emission Microscopy analysis

Device Preparation

Power up the device in failure-reproducing state, ensure proper cooling

Darkroom Setup

Position device under EMMI microscope, ensure proper alignment

Camera Configuration

Set appropriate exposure time (typically 10-60 seconds) and sensitivity

Image Acquisition

Capture multiple images with varying exposure times for optimal results

Analysis & Overlay

Overlay emission spots with design layout to identify failing structures

Troubleshooting Tip

If no hotspots appear, verify the chip is in a failure-reproducing state and check if the failure mechanism produces photon emissions (open circuits typically do not)

Common Failure Analysis Pitfalls

ESD Damage Overlook

Failing to account for electrostatic discharge damage during handling, especially in CMOS chips. Always verify wrist strap functionality and grounding protocols.

Inadequate Power Derating

Resistor burnout from operating at 80%+ power load. Recommended practice is 50% derating to ensure reliability under varying conditions.

Incorrect Failure Reproduction

Analyzing devices under conditions that don't accurately reproduce the field failure scenario, leading to incorrect root cause identification.

Overlooking Packaging Issues

Focusing exclusively on die-level issues while missing package-related failures like delamination, lead corrosion, or solder joint fatigue.

Insufficient Documentation

Failing to document each analysis step thoroughly, making it difficult to replicate results or perform trend analysis across multiple failures.

Tool Calibration Issues

Using improperly calibrated equipment, leading to inaccurate measurements and incorrect failure analysis conclusions.

Industry Case Studies

IGBT Module Failure in EVs

Symptom

Sudden power loss during charging, with no visible external damage to the EV powertrain.

Analysis Process

- Thermal imaging revealed hotspots in IGBT module during power cycling

- SEM/EDS analysis identified excessive IMC (Cu₆Sn₅) growth in solder joints

- Cross-sectioning showed Kirkendall void formation at the solder-substrate interface

- FEA simulation linked failure to insufficient solder reflow profile

Solution & Outcome

Adjusted reflow profile to ensure proper wetting and added nickel-plated pads to control IMC growth.

Result: Field failure rate reduced by 0.58% annually, saving $2M in warranty costs.

Relevant Standards

Thermal Imaging Results

SEM Image of IMC Growth

GaAs Amplifier Failure in 5G AAUs

Symptom

Field failures in 5G Active Antenna Units (AAUs) within 6 months of deployment, resulting in signal degradation.

Analysis Process

- C-SAM inspection detected die cracks in GaAs power amplifiers

- Packaging audit found abnormal ejector marks on die backside

- Reliability data analysis showed failure distribution fitting early failure mode

- Finite element analysis confirmed mechanical stress during die bonding

Solution & Outcome

Modified die bonding blue film to reduce mechanical stress and implemented 100% post-bond inspection using automated optical inspection.

Result: Failure rate reduced by 92%, extending mean time between failures to over 5 years.

Relevant Standards

C-SAM Image of Die Cracks

Failure Distribution Analysis

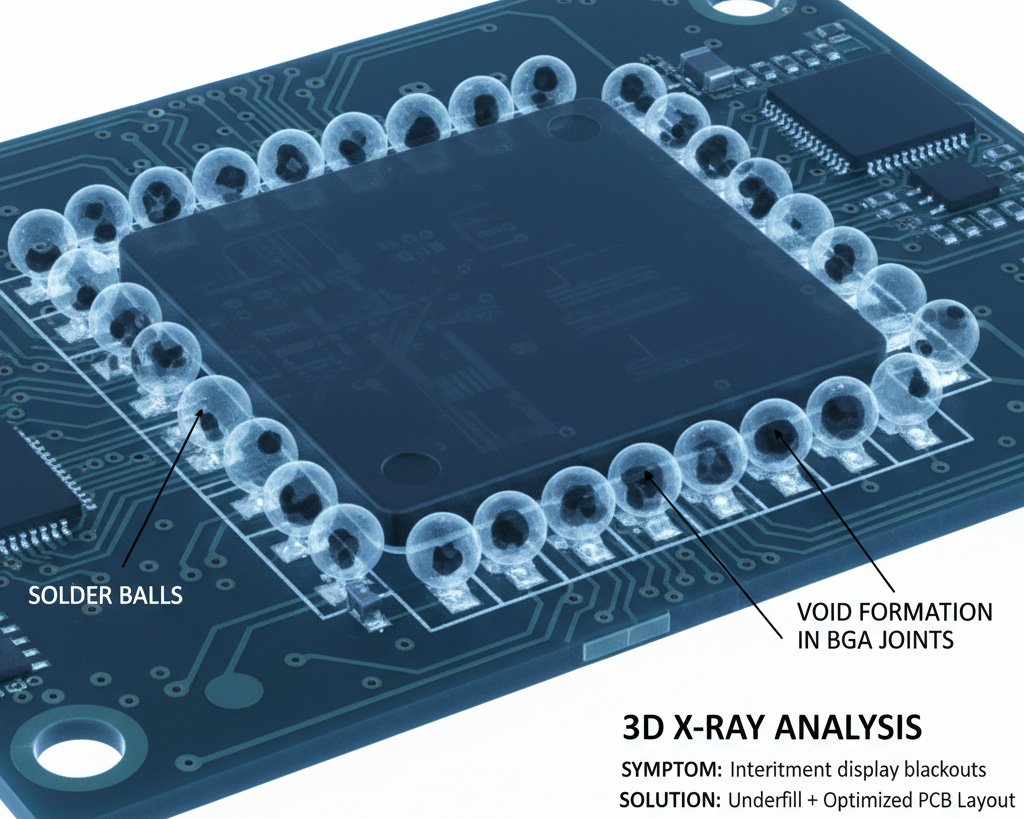

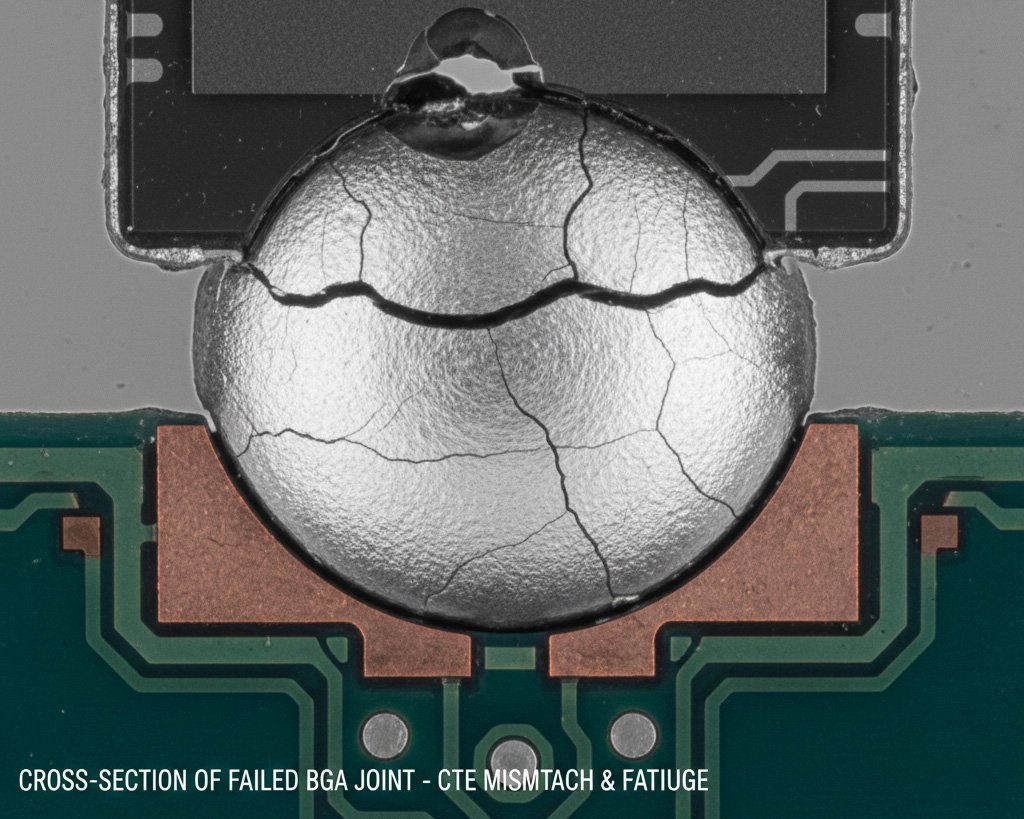

BGA Failure in Smartphones

Symptom

Intermittent display blackouts and unresponsive touchscreen in high-end smartphones after 6-8 months of use.

Analysis Process

- Thermal cycling ( -40°C to 85°C) reproduced the failure in lab conditions

- SAM (Scanning Acoustic Microscopy) revealed solder joint fatigue

- Cross-sectioning confirmed CTE (Coefficient of Thermal Expansion) mismatch

- 3D X-ray analysis quantified void formation in 18% of BGA joints

Solution & Outcome

Implemented underfill with higher Tg (Glass Transition Temperature) and optimized PCB layout to reduce thermal gradients.

Result: Field returns reduced by 76%, with no failures reported beyond 18 months of use.

Relevant Standards

3D X-ray of BGA Voids

Cross-section of Failed Joint

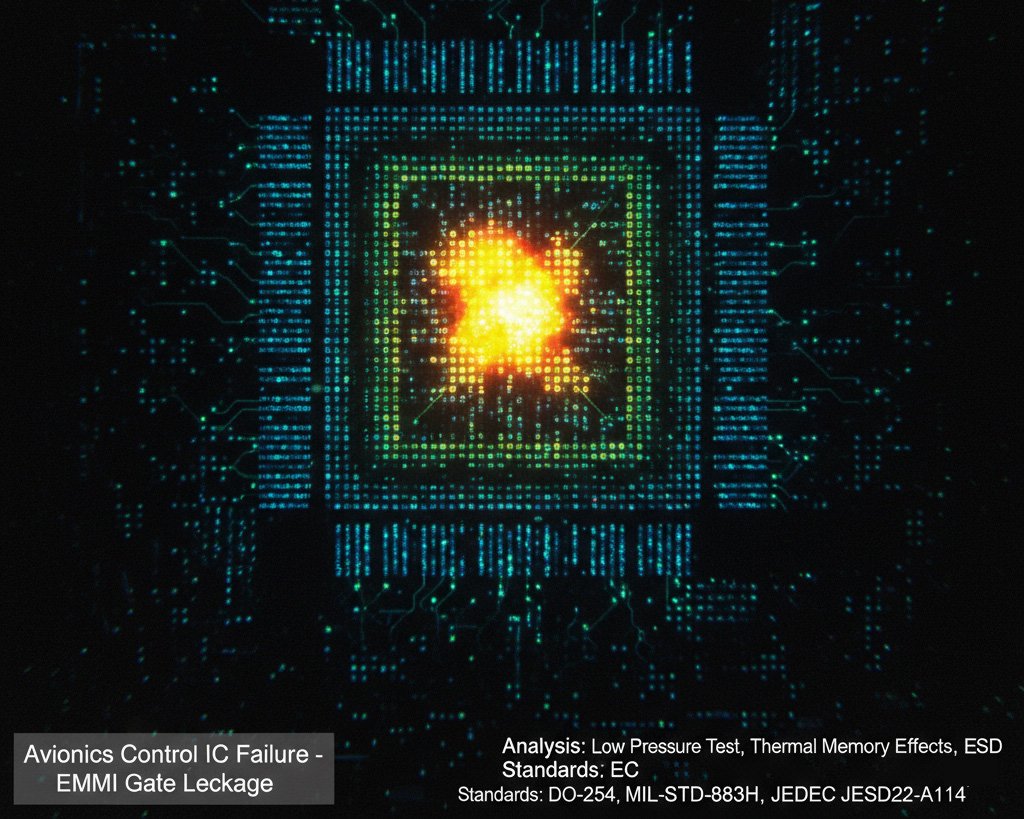

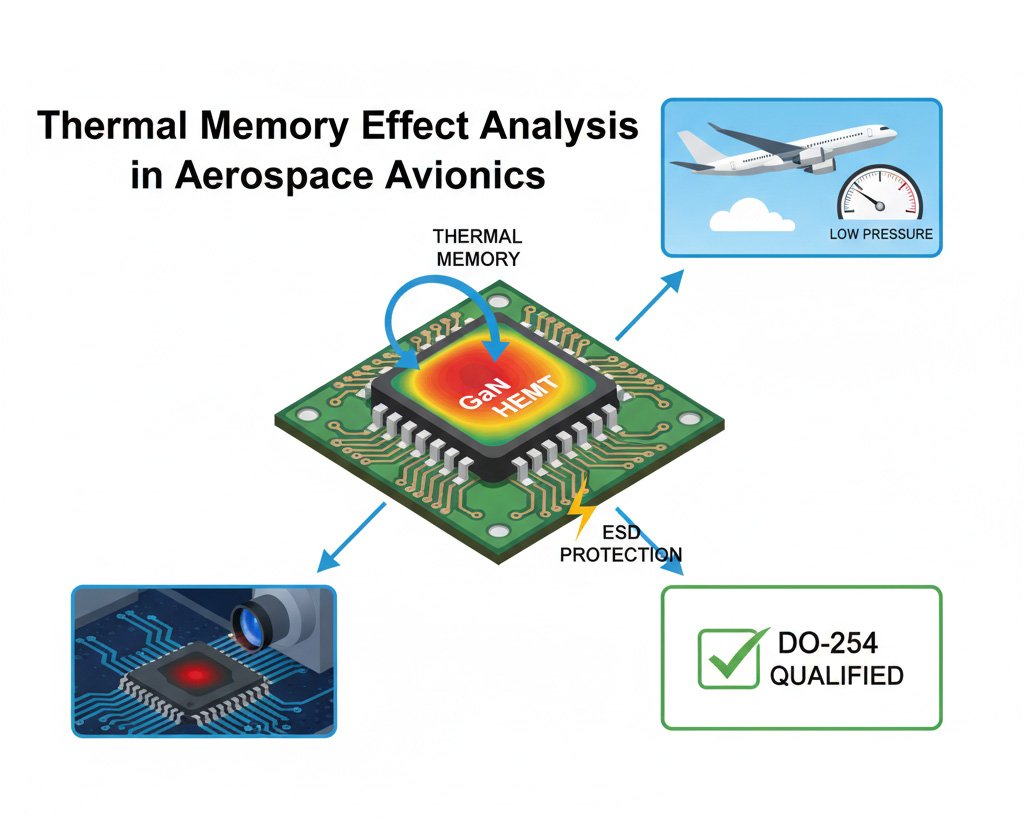

Avionics Control IC Failure

Symptom

Random system resets in avionics control modules during high-altitude flight, with no clear pattern.

Analysis Process

- Environmental testing reproduced failure under low pressure (high altitude) conditions

- EMMI detected intermittent gate leakage in power management IC

- IC-CAP modeling identified unmodeled thermal memory effects in GaN HEMTs

- ESD testing revealed insufficient protection in input circuitry

Solution & Outcome

Updated ASM-HEMT model to include thermal memory effects and enhanced ESD protection circuitry.

Result: Complete elimination of in-flight resets, with successful qualification under DO-254 standards.

Relevant Standards

EMMI Image of Gate Leakage

Thermal Memory Effect Analysis

Tools & Equipment

| Tool | Core Use Case | Resolution Limit | Best For | Limitation |

|---|---|---|---|---|

| EMMI | Hotspot localization (leaks, breakdowns) | ~1μm | CMOS/FinFETs | No signal for open circuits |

| C-SAM | Delamination/void detection | 50nm | Flip-chip, BGA | Requires liquid coupling |

| 3D X-ray CT | TSV/stacked die inspection | 100nm | 3D ICs | High cost for high resolution |

| Lock-in Thermography | Sub-°C thermal mapping | 0.1°C | Power ICs (IGBTs) | Slow scan time |

| SEM/EDS | Material characterization, defect imaging | 1-5nm | Die-level physical analysis | Requires conductive coating for insulators |

| FIB-SEM | Cross-sectioning, circuit editing | 5nm | 3D ICs, advanced packaging | Destructive, time-consuming |

Tool-Technique Pairing Guide

Matching the right tools to specific failure scenarios ensures efficient and accurate root cause analysis:

ESD Damage Analysis

- Start with EMMI to locate leakage sites

- Follow with FIB-SEM for nanoscale imaging of damage

- Use EDS to check for contamination at failure sites

- Verify with electrical testing (IV curve analysis)

3D IC TSV Cracks

- Use 3D X-ray CT for non-destructive inspection

- Validate with FIB cross-sectioning at critical locations

- Perform SEM imaging to characterize crack morphology

- Apply finite element analysis to determine stress origins

Thermal-Related Failures

- Begin with lock-in thermography for thermal mapping

- Use C-SAM to check for delamination due to thermal stress

- Perform cross-sectioning to examine solder joint integrity

- Validate with thermal cycling tests

Intermittent Failures

- Use environmental chamber to reproduce failure conditions

- Apply OBIRCH for dynamic current path analysis

- Employ thermal imaging during stress testing

- Verify with vibration testing if mechanical stress is suspected

Emerging Tools & Technologies

AI-Enhanced EMMI

Machine learning algorithms that automatically distinguish normal vs. abnormal photon emission patterns, reducing analysis time by up to 70%.

Quantum Dot Labeling

Nanoscale fluorescent markers that highlight defect regions in semiconductors, enabling earlier detection of potential failure sites.

Predictive FA Platforms

Integrated systems that combine manufacturing data, in-field failure reports, and AI to predict potential failure mechanisms before they occur.

Standards & Compliance

JEDEC Standards

JESD22-A121: ESD Testing

Defines procedures for human body model (HBM), machine model (MM), and charged device model (CDM) electrostatic discharge testing.

JESD47: Stress Test Methods for Integrated Circuits

Comprehensive standard covering various stress tests including temperature cycling, voltage temperature, electromigration, and time-dependent dielectric breakdown.

JESD22-A104: Temperature Cycling

Specific standard for temperature cycling tests to evaluate component reliability under thermal stress conditions.

Industry-Specific Standards

AEC-Q100: Automotive ICs

Qualification specification for integrated circuits used in automotive applications, with stringent reliability requirements.

DO-254: Aerospace Avionics

Design assurance guidance for airborne electronic hardware, including integrated circuits used in flight-critical systems.

Telcordia GR-468: Telecommunications

Requirements for reliability assurance of semiconductor devices used in telecommunications equipment.

Reliability Data Analysis

Effective failure analysis requires statistical analysis of reliability data to understand failure distributions and predict product lifetime:

Failure Distributions

- Log-normal distribution: Common for semiconductor failures

- Weibull distribution: Useful for analyzing early, random, and wear-out failures

- Exponential distribution: Appropriate for constant failure rate regions

Key Metrics

- MTBF (Mean Time Between Failures)

- Failure Rate (λ) - typically expressed in FITs (Failures In Time: 1 FIT = 1 failure per 10^9 device-hours)

- Accelerated Life Testing (ALT) conversion factors

Failure Rate Analysis Example

Future Trends in IC Failure Analysis

Advanced Process Nodes (2nm/1nm)

Analysis challenges at the atomic scale with quantum effects becoming significant factors in failure mechanisms.

Key Challenges

- • Quantum tunneling effects

- • Backside power delivery defects

- • Atomic-level contamination detection

Emerging Solutions

- • Cryogenic TEM for atomic-level inspection

- • AI-driven nanoprobing techniques

- • Advanced atom probe tomography

3D IC & Heterogeneous Integration

Complex failure modes in stacked die architectures requiring new non-destructive analysis techniques.

Key Challenges

- • TSV (Through-Silicon Via) cracking

- • Underfill delamination in stacked dies

- • Thermal management issues

Emerging Solutions

- • Advanced 3D X-ray CT with higher resolution

- • Multi-modal imaging techniques

- • Design-for-testability in 3D ICs

AI & Machine Learning

Automated failure detection and classification to handle the increasing complexity of ICs.

Key Applications

- • Automated defect classification in SEM images

- • Predictive failure analysis from manufacturing data

- • Anomaly detection in wafer test data

Benefits

- • 50-70% reduction in analysis time

- • Improved accuracy in root cause identification

- • Early failure prediction before field deployment