Análisis de fallos de circuitos integrados

Recurso técnico integral sobre metodologías, herramientas y estudios de caso para el análisis de fallos en semiconductores.

¿Qué es el análisis de fallos de circuitos integrados?

El análisis de fallas en circuitos integrados (CI) es un proceso sistemático que se utiliza para identificar, aislar y determinar la causa raíz de las fallas en dispositivos semiconductores. Esta disciplina de ingeniería fundamental combina técnicas avanzadas de imagen, pruebas eléctricas y ciencia de los materiales para resolver problemas en circuitos integrados en diversas industrias.

Un análisis de fallos eficaz mejora la fiabilidad del producto, reduce los costes de fabricación, acelera el lanzamiento al mercado y garantiza el cumplimiento de las normas del sector. Desempeña un papel fundamental en el control de calidad, la ingeniería de fiabilidad y los ciclos de mejora del producto.

Objetivos clave del análisis de fallos de circuitos integrados

- Identificar las causas fundamentales de las fallas de los circuitos integrados mediante una investigación sistemática.

- Determinar si las fallas se originan en el diseño, la fabricación o la aplicación.

- Desarrollar acciones correctivas para prevenir fallas futuras.

- Validar la fiabilidad y el rendimiento de los circuitos integrados.

- Soporte para la notificación de fallos y el análisis de datos de fiabilidad.

Guías técnicas y metodologías

Diagrama de flujo de diagnóstico

Enfoque sistemático desde la identificación de los síntomas de falla hasta la identificación de la causa raíz.

Ruta de fallo de alimentación/salida no disponible

- 1. Comprobar si hay daños por ESD mediante análisis SEM/EDS.

- 2. Verificar las uniones de soldadura mediante inspección por rayos X 3D.

- 3 Prueba de ruptura del óxido de puerta mediante EMMI

- 4. Realizar pruebas de continuidad con OBIRCH.

- 5. Analizar la integridad del paquete con C-SAM.

Ruta de fallos intermitentes

- 1. Descartar microfisuras BGA mediante C-SAM

- 2. Comprobar si hay estrés térmico mediante imágenes infrarrojas.

- 3. Prueba de enganche relacionado con el diseño mediante simulación de circuitos.

- 4. Verificar la integridad de la red de distribución de energía.

Guía de funcionamiento de EMMI

Flujo de trabajo paso a paso para el análisis mediante microscopía de emisión.

Preparación del dispositivo

Encienda el dispositivo en el estado en el que se reproduce la falla y asegúrese de que haya una refrigeración adecuada.

Configuración del cuarto oscuro

Coloque el dispositivo bajo el microscopio EMMI y asegúrese de que esté correctamente alineado.

Configuración de la cámara

Ajuste el tiempo de exposición adecuado (normalmente de 10 a 60 segundos) y la sensibilidad.

Adquisición de imágenes

Captura varias imágenes con diferentes tiempos de exposición para obtener resultados óptimos.

Análisis y superposición

Superponga los puntos de emisión con el diseño para identificar estructuras defectuosas.

Consejo para solucionar problemas

Si no aparecen puntos calientes, verifique que el chip se encuentre en un estado que reproduzca la falla y compruebe si el mecanismo de falla produce emisiones de fotones (los circuitos abiertos normalmente no las producen).

Errores comunes en el análisis de fallos

Anomalía de los daños por descarga electrostática

No tener en cuenta los daños por descarga electrostática durante la manipulación, especialmente en los chips CMOS. Verifique siempre el funcionamiento de la pulsera antiestática y los protocolos de conexión a tierra.

Reducción de potencia inadecuada

Quema de resistencias por operar a una carga de potencia superior al 80 %. Se recomienda reducir la potencia nominal en un 50 % para garantizar la fiabilidad en diversas condiciones.

Reproducción de fallos incorrectos

Analizar los dispositivos en condiciones que no reproducen con precisión el escenario de fallo en condiciones reales, lo que lleva a una identificación incorrecta de la causa raíz.

Pasar por alto los problemas de embalaje

Centrarse exclusivamente en problemas a nivel del chip, pasando por alto fallos relacionados con el encapsulado, como la deslaminación, la corrosión de los cables o la fatiga de las juntas de soldadura.

Documentación insuficiente

No documentar minuciosamente cada paso del análisis dificulta la replicación de los resultados o la realización de análisis de tendencias en múltiples fallos.

Problemas de calibración de herramientas

El uso de equipos mal calibrados conlleva mediciones inexactas y conclusiones erróneas en el análisis de fallos.

Estudios de casos de la industria

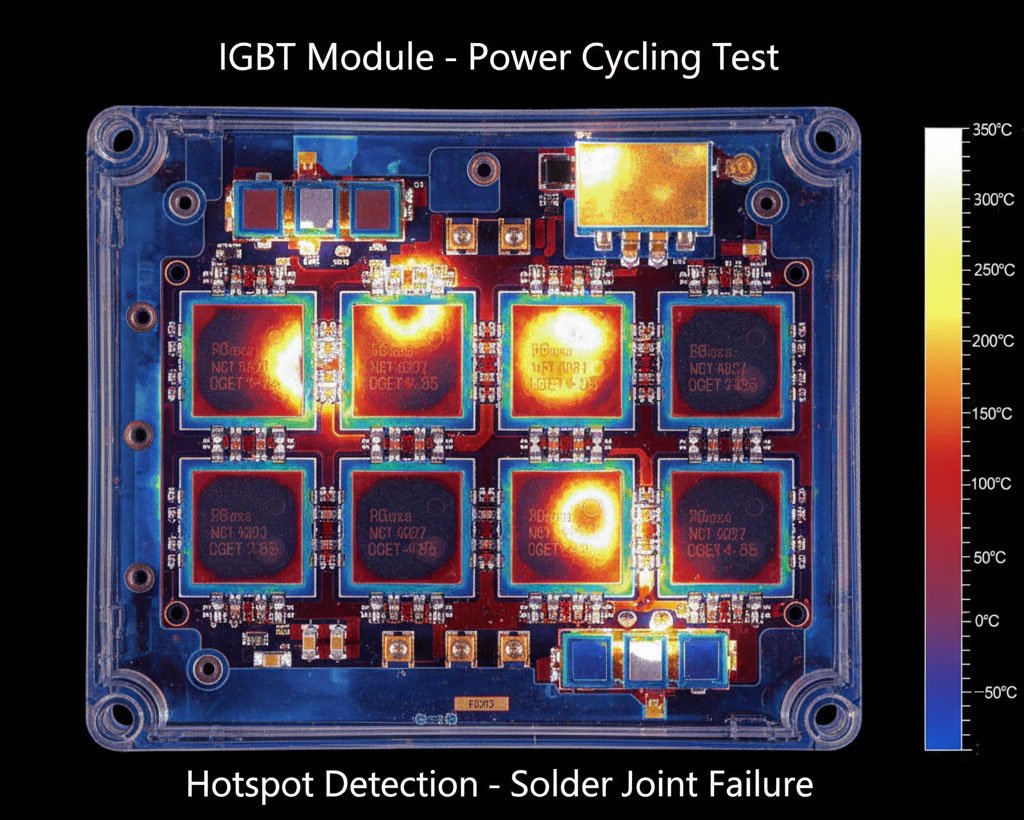

Fallo del módulo IGBT en vehículos eléctricos

Síntoma

Pérdida repentina de potencia durante la carga, sin daños externos visibles en el sistema de propulsión del vehículo eléctrico.

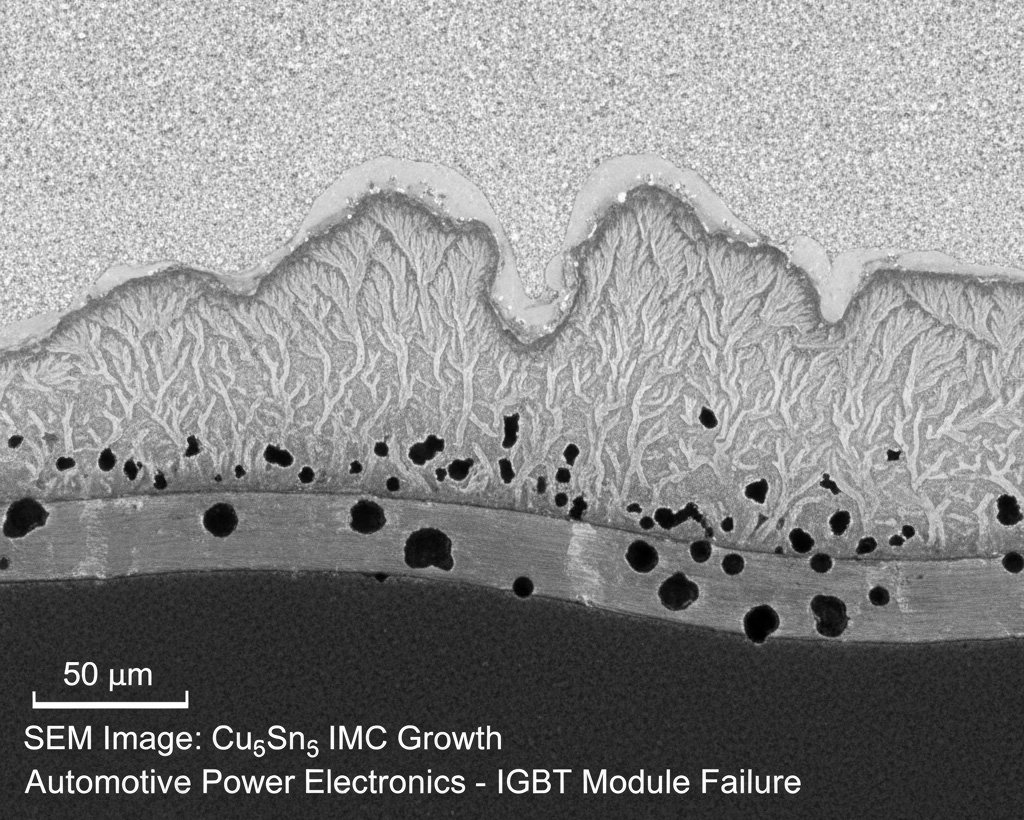

Proceso de análisis

- Las imágenes térmicas revelaron puntos calientes en el módulo IGBT durante el ciclo de potencia.

- El análisis SEM/EDS identificó un crecimiento excesivo de IMC (Cu₆Sn₅) en las uniones de soldadura.

- El análisis de secciones transversales mostró la formación de vacíos de Kirkendall en la interfaz soldadura-sustrato.

- La simulación FEA relacionó el fallo con un perfil de reflujo de soldadura insuficiente.

Solución y resultado

Se ajustó el perfil de reflujo para asegurar una humectación adecuada y se añadieron almohadillas niqueladas para controlar el crecimiento de la capa intermetálica.

Resultado: La tasa de fallos en campo se redujo en un 0,58 % anual, lo que supuso un ahorro de 2 millones de dólares en costes de garantía.

Normas pertinentes

Resultados de imágenes térmicas

Imagen SEM del crecimiento de IMC

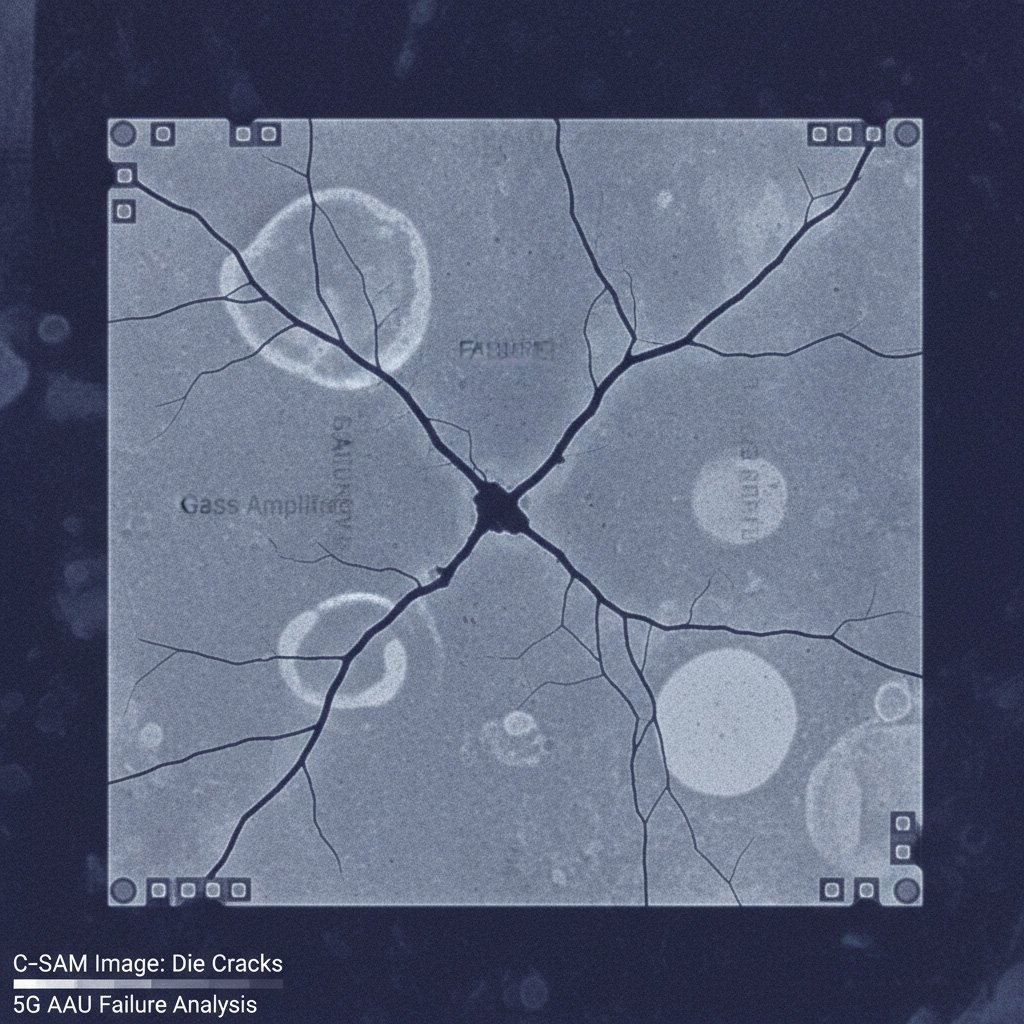

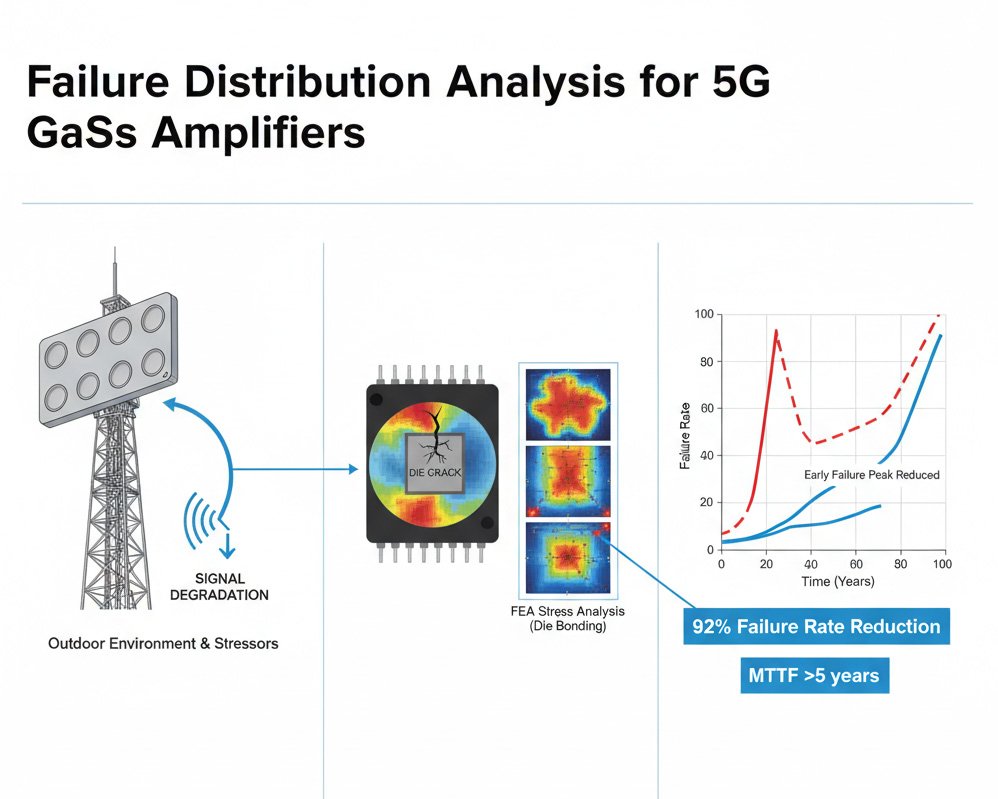

Fallo del amplificador de GaAs en las unidades de amplificación de señal (AAU) 5G.

Síntoma

Fallos en las unidades de antena activa (AAU) 5G en los 6 meses posteriores a su despliegue, lo que provoca una degradación de la señal.

Proceso de análisis

- La inspección mediante C-SAM detectó grietas en los chips de los amplificadores de potencia de GaAs.

- La auditoría de empaquetado encontró marcas de eyector anormales en la parte posterior del chip.

- El análisis de datos de confiabilidad mostró que la distribución de fallas se ajustaba al modo de falla temprana.

- El análisis de elementos finitos confirmó la tensión mecánica durante la unión de los chips.

Solución y resultado

Se modificó la película azul de unión de chips para reducir la tensión mecánica y se implementó una inspección posterior a la unión del 100 % mediante inspección óptica automatizada.

Resultado: La tasa de fallos se redujo en un 92%, lo que amplió el tiempo medio entre fallos a más de 5 años.

Normas pertinentes

Imagen C-SAM de grietas en el chip

Análisis de distribución de fallas

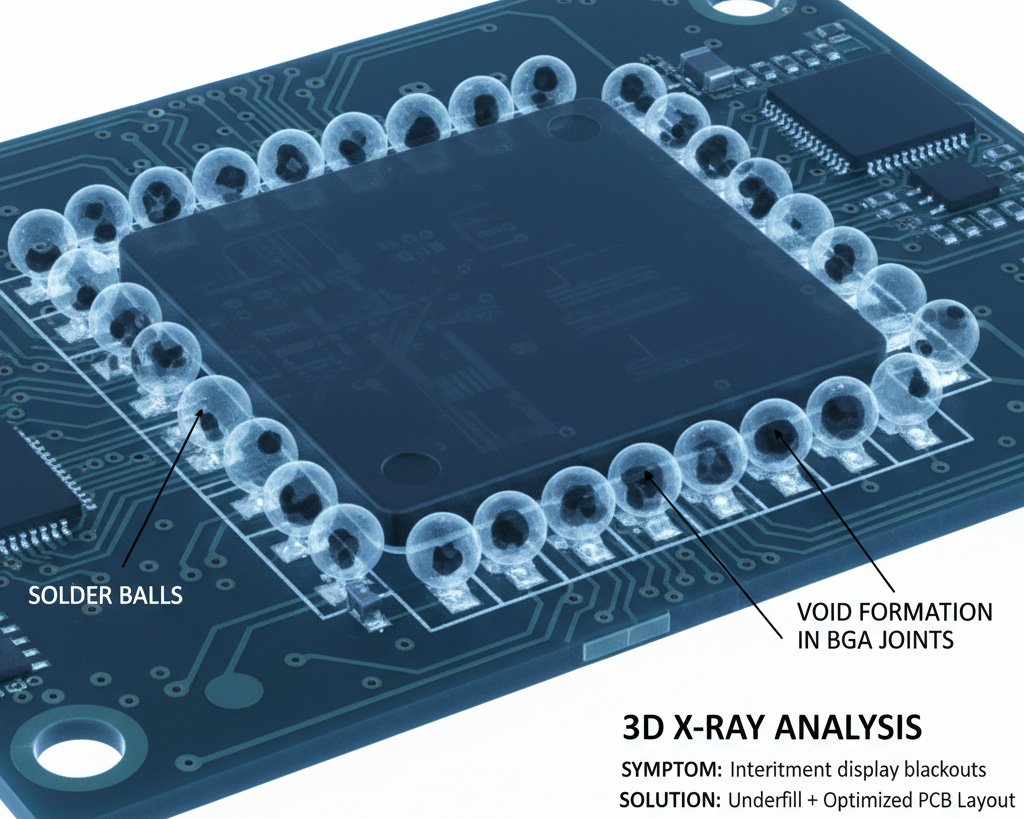

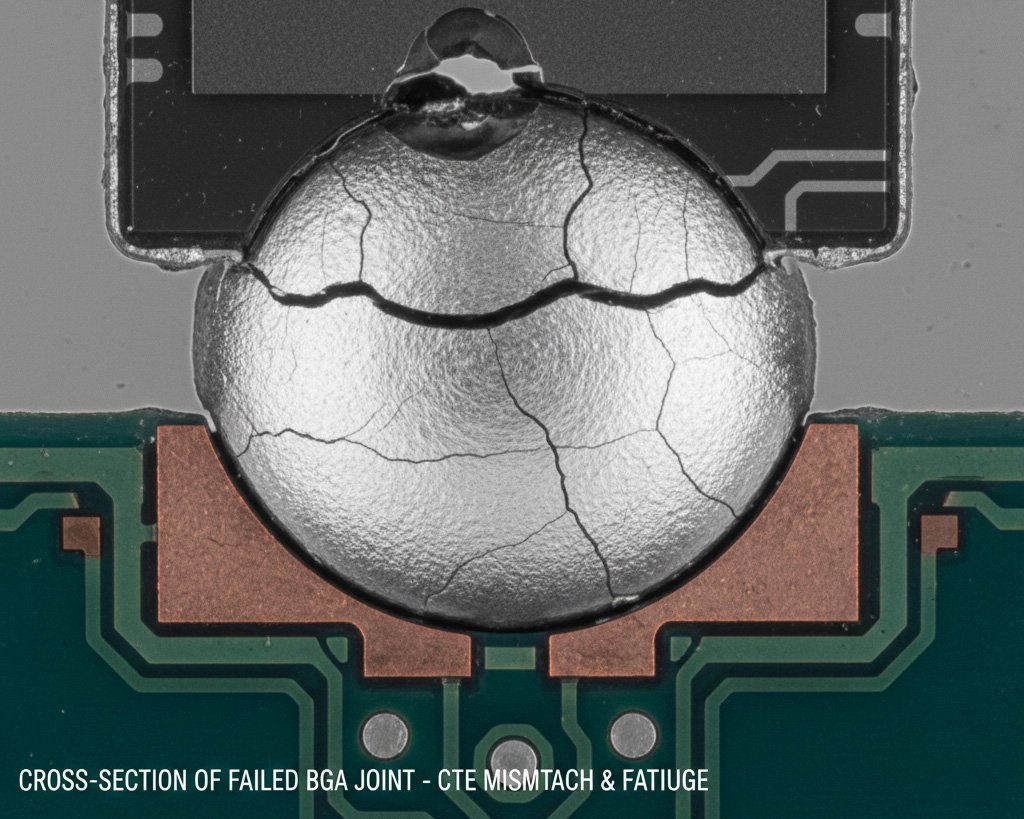

Fallo de BGA en teléfonos inteligentes

Síntoma

Apagones intermitentes de la pantalla y falta de respuesta de la pantalla táctil en teléfonos inteligentes de gama alta después de 6 a 8 meses de uso.

Proceso de análisis

- El ciclo térmico (de -40 °C a 85 °C) reprodujo la falla en condiciones de laboratorio.

- La microscopía acústica de barrido (SAM) reveló fatiga en la unión de soldadura.

- El seccionamiento transversal confirmó la discrepancia en el CTE (coeficiente de expansión térmica).

- El análisis de rayos X en 3D cuantificó la formación de huecos en el 18% de las uniones BGA.

Solución y resultado

Se implementó un encapsulado con una temperatura de transición vítrea (Tg) más alta y se optimizó el diseño de la placa de circuito impreso para reducir los gradientes térmicos.

Resultado: Las devoluciones en campo se redujeron en un 76%, sin que se registraran fallos después de 18 meses de uso.

Normas pertinentes

Radiografía 3D de los huecos de BGA

Sección transversal de la junta defectuosa

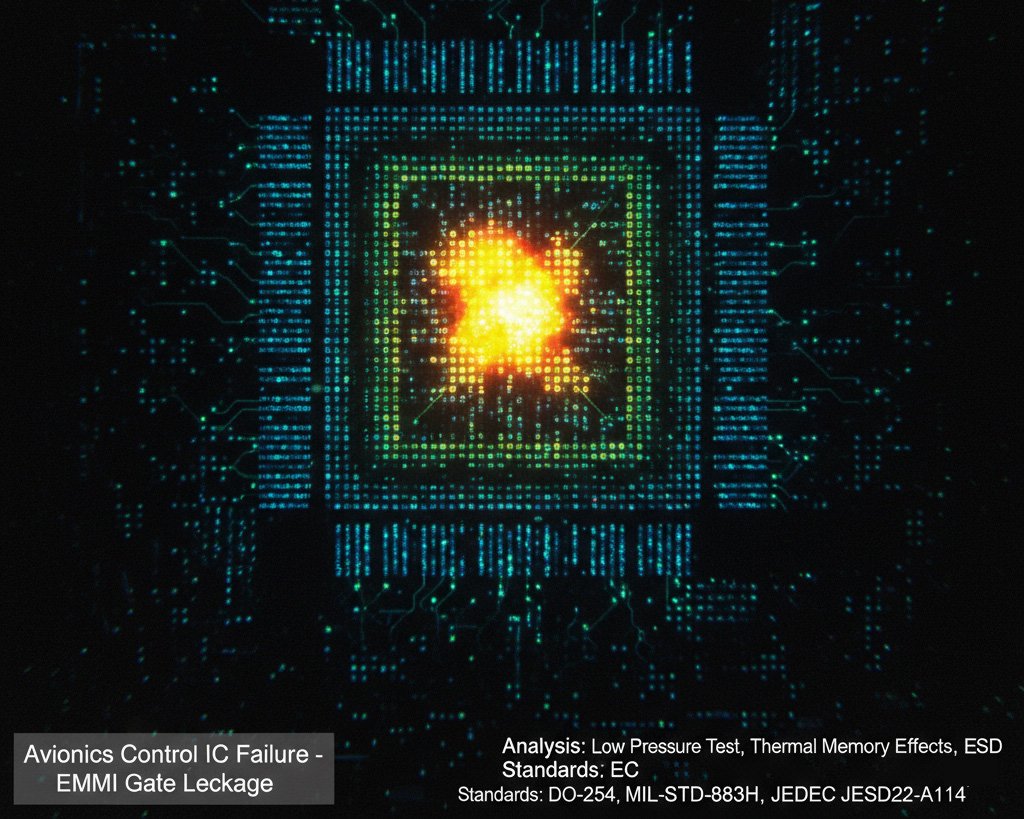

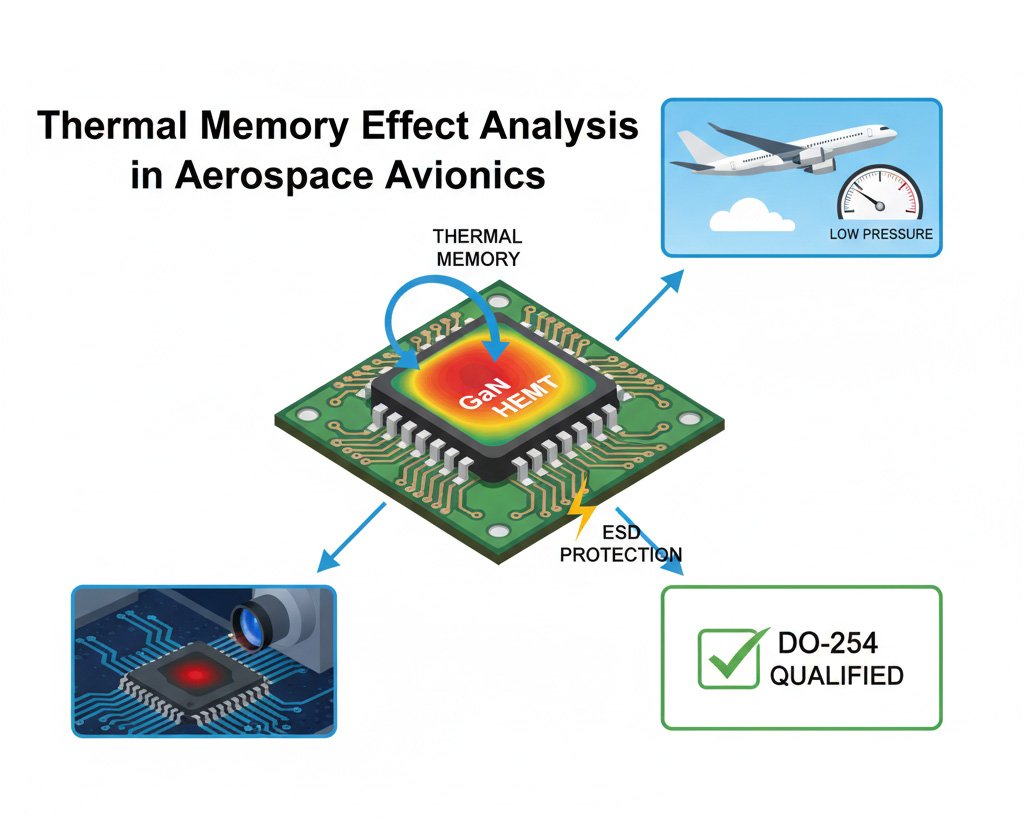

Fallo del circuito integrado de control de aviónica

Síntoma

Reinicios aleatorios del sistema en los módulos de control de aviónica durante el vuelo a gran altitud, sin un patrón claro.

Proceso de análisis

- Las pruebas ambientales reprodujeron el fallo en condiciones de baja presión (gran altitud).

- EMMI detectó fugas intermitentes en la puerta del circuito integrado de gestión de energía.

- El modelado IC-CAP identificó efectos de memoria térmica no modelados en los HEMT de GaN.

- Las pruebas ESD revelaron una protección insuficiente en los circuitos de entrada.

Solución y resultado

Modelo ASM-HEMT actualizado para incluir efectos de memoria térmica y circuitos de protección ESD mejorados.

Resultado: Eliminación total de los reinicios en vuelo, con calificación satisfactoria según los estándares DO-254.

Normas pertinentes

Imagen EMMI de fugas en la puerta

Análisis del efecto de memoria térmica

Herramientas y equipos

| Herramienta | Caso de uso principal | Límite de resolución | Lo mejor para | Limitación |

|---|---|---|---|---|

| EMMI | Localización de puntos críticos (fugas, averías) | ~1 μm | CMOS/FinFETs | No hay señal de circuitos abiertos |

| C-SAM | Detección de deslaminación/vacío | 50 nm | Flip-chip, BGA | Requiere acoplamiento líquido |

| Tomografía computarizada de rayos X 3D | Inspección de chips apilados/TSV | 100 nm | Circuitos integrados 3D | Alto costo para alta resolución |

| Termografía de bloqueo | Mapeo térmico por debajo de °C | 0,1 °C | Circuitos integrados de potencia (IGBT) | Tiempo de escaneo lento |

| Microscopía electrónica de barrido/EDS | Caracterización de materiales, obtención de imágenes de defectos | 1-5 nm | Análisis físico a nivel de chip | Requiere recubrimiento conductor para los aislantes. |

| FIB-SEM | Corte transversal, edición de circuitos | 5 nm | Circuitos integrados 3D, encapsulado avanzado | Destructivo, requiere mucho tiempo. |

Guía de combinación de herramientas y técnicas

La elección de las herramientas adecuadas para cada escenario de fallo específico garantiza un análisis de la causa raíz eficiente y preciso:

Análisis de daños por descarga electrostática

- Comience con EMMI para localizar los puntos de fuga.

- A continuación, utilice FIB-SEM para obtener imágenes a nanoescala del daño.

- Utilice EDS para comprobar la contaminación en los puntos de fallo.

- Verificar mediante pruebas eléctricas (análisis de curva I-V).

Grietas en TSV de circuitos integrados 3D

- Utilice la tomografía computarizada de rayos X 3D para la inspección no destructiva.

- Validar mediante cortes transversales con FIB en ubicaciones críticas.

- Realizar imágenes SEM para caracterizar la morfología de las grietas.

- Aplicar el análisis de elementos finitos para determinar el origen de las tensiones.

Fallos relacionados con el calor

- Comience con termografía de bloqueo para mapeo térmico.

- Utilice C-SAM para comprobar la delaminación debida a la tensión térmica.

- Realizar un corte transversal para examinar la integridad de la junta de soldadura.

- Validar mediante pruebas de ciclos térmicos.

Fallos intermitentes

- Utilice una cámara ambiental para reproducir las condiciones de falla.

- Aplicar OBIRCH para el análisis dinámico de la trayectoria de la corriente.

- Utilice imágenes térmicas durante las pruebas de estrés.

- Verificar mediante pruebas de vibración si se sospecha de tensión mecánica.

Herramientas y tecnologías emergentes

EMMI mejorado con IA

Algoritmos de aprendizaje automático que distinguen automáticamente los patrones de emisión de fotones normales de los anormales, reduciendo el tiempo de análisis hasta en un 70 %.

Etiquetado de puntos cuánticos

Marcadores fluorescentes a nanoescala que resaltan las regiones defectuosas en los semiconductores, lo que permite una detección más temprana de posibles puntos de fallo.

Plataformas predictivas de análisis de fallos

Sistemas integrados que combinan datos de fabricación, informes de fallos en campo e inteligencia artificial para predecir posibles mecanismos de fallo antes de que se produzcan.

Normas y cumplimiento

Estándares JEDEC

JESD22-A121: Pruebas ESD

Define los procedimientos para las pruebas de descarga electrostática en modelos de cuerpo humano (HBM), modelos de máquina (MM) y modelos de dispositivos cargados (CDM).

JESD47: Métodos de prueba de estrés para circuitos integrados

Norma integral que abarca diversas pruebas de estrés, incluyendo ciclos de temperatura, temperatura de voltaje, electromigración y ruptura dieléctrica dependiente del tiempo.

JESD22-A104: Ciclo de temperatura

Norma específica para ensayos de ciclos de temperatura para evaluar la fiabilidad de los componentes en condiciones de estrés térmico.

Normas específicas del sector

AEC-Q100: Circuitos integrados para automoción

Especificación de cualificación para circuitos integrados utilizados en aplicaciones automotrices, con estrictos requisitos de fiabilidad.

DO-254: Aviónica aeroespacial

Guía de garantía de diseño para hardware electrónico aeronáutico, incluidos los circuitos integrados utilizados en sistemas críticos para el vuelo.

Telcordia GR-468: Telecomunicaciones

Requisitos para garantizar la fiabilidad de los dispositivos semiconductores utilizados en equipos de telecomunicaciones.

Análisis de datos de fiabilidad

Un análisis de fallos eficaz requiere un análisis estadístico de los datos de fiabilidad para comprender la distribución de los fallos y predecir la vida útil del producto:

Distribuciones de fallas

- Distribución lognormal: común en fallos de semiconductores.

- Distribución de Weibull: Útil para analizar fallas tempranas, aleatorias y por desgaste.

- Distribución exponencial: apropiada para regiones con tasa de fallos constante.

Métricas clave

- MTBF (Tiempo medio entre fallos)

- Tasa de fallos (λ): normalmente se expresa en FIT (Fallos en el tiempo: 1 FIT = 1 fallo por cada 10^9 horas de dispositivo).

- Factores de conversión de las pruebas de vida acelerada (ALT, por sus siglas en inglés)

Ejemplo de análisis de la tasa de fallos

Tendencias futuras en el análisis de fallos de circuitos integrados

Nodos de proceso avanzados (2 nm/1 nm)

Los análisis presentan desafíos a escala atómica, donde los efectos cuánticos se convierten en factores importantes en los mecanismos de falla.

Principales desafíos

- • Efectos de tunelización cuántica

- • Defectos en el suministro de energía en la parte posterior

- • Detección de contaminación a nivel atómico

Soluciones emergentes

- • Microscopio electrónico de transmisión criogénico para inspección a nivel atómico

- • Técnicas de nanosondeo impulsadas por IA

- • Tomografía de sonda atómica avanzada

Circuitos integrados 3D e integración heterogénea

Modos de fallo complejos en arquitecturas de chips apilados que requieren nuevas técnicas de análisis no destructivo.

Principales desafíos

- • Agrietamiento de TSV (vías pasantes de silicio)

- • Delaminación del encapsulado en chips apilados

- • Problemas de gestión térmica

Soluciones emergentes

- • Tomografía computarizada de rayos X 3D avanzada con mayor resolución.

- • Técnicas de imagen multimodal

- • Diseño para la comprobabilidad en circuitos integrados 3D

Inteligencia artificial y aprendizaje automático

Detección y clasificación automatizada de fallos para gestionar la creciente complejidad de los circuitos integrados.

Aplicaciones clave

- • Clasificación automatizada de defectos en imágenes SEM

- • Análisis predictivo de fallos a partir de datos de fabricación

- • Detección de anomalías en los datos de prueba de obleas

Beneficios

- • Reducción del 50-70% en el tiempo de análisis

- • Mayor precisión en la identificación de la causa raíz

- • Predicción temprana de fallos antes de la implementación en campo