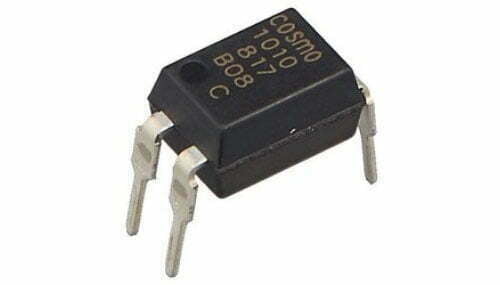

O que é um circuito integrado?

Um circuito integrado (IC) é um circuito eletrônico construído em um único chip semicondutor. É o tipo de dispositivo eletrônico mais comumente usado em computadores, telefones celulares e outros aparelhos eletrônicos. Geralmente, um IC é um pequeno pedaço de silício, com cerca de um oitavo de polegada quadrada, que contém milhares ou milhões de transistores, resistores e outros componentes de placa de circuito. Esse tipo de circuito miniatura permite que uma variedade de funções seja executada em um tamanho muito menor e com maior eficiência do que se os componentes fossem construídos separadamente.

Componentes de um circuito integrado

Os circuitos integrados são compostos por vários componentes, cada um dos quais desempenha uma função específica. Esses componentes são normalmente conectados entre si por minúsculos traços metálicos, que são usados para transportar sinais elétricos entre as várias partes do circuito. Os componentes são geralmente muito pequenos, variando de alguns micrômetros a alguns milímetros de tamanho. Isso permite que um grande número de componentes seja colocado em um único chip, permitindo um maior grau de complexidade e funcionalidade.

Benefícios dos circuitos integrados

Os circuitos integrados são ferramentas poderosas que nos permitem aumentar a complexidade e a funcionalidade dos nossos aparelhos eletrônicos. Ao colocar vários componentes em um único chip, podemos reduzir o espaço necessário para um dispositivo. Isso, por sua vez, reduz os custos e aumenta a eficiência do dispositivo. A integração dos componentes também ajuda a reduzir a interferência eletromagnética, permitindo que nossos aparelhos eletrônicos funcionem de forma mais confiável. Os circuitos integrados são a base da eletrônica moderna e são essenciais para a nossa vida cotidiana.

Aplicações dos circuitos integrados

Os circuitos integrados são a base da maioria dos aparelhos eletrônicos modernos. Eles são usados em computadores, telefones celulares, televisores, rádios e muitos outros dispositivos eletrônicos. Também podem ser encontrados em eletrodomésticos, como máquinas de lavar, micro-ondas e máquinas de lavar louça. Além disso, estão sendo cada vez mais utilizados em dispositivos médicos, máquinas industriais e sistemas automotivos.

Visão geral do processo de design de circuitos integrados

O design de IC é um processo complexo para projetar circuitos eletrônicos. Envolve várias etapas, incluindo design front-end, design back-end e montagem final. O processo é altamente iterativo e requer uma estreita colaboração entre o designer e os engenheiros para garantir que o design atenda a todas as especificações exigidas. Em cada etapa do processo, protótipos são criados para testar e verificar se os designs estão funcionando conforme o esperado.

Design front-end

O design front-end de circuitos integrados é o processo de projetar os componentes básicos de um circuito integrado (IC), como transistores, resistores e capacitores. Isso é feito usando uma variedade de ferramentas, como captura esquemática, síntese lógica e software de layout. O objetivo do design front-end é criar um IC que atenda às especificações desejadas.

Especificações do IC

As especificações do projeto do IC definem os componentes e atributos essenciais que o circuito deve incorporar. É a base sobre a qual todo o processo de projeto será construído. As especificações devem ser capazes de capturar todos os requisitos necessários para criar um projeto de IC bem-sucedido. Além disso, devem ser capazes de se adaptar às necessidades e tecnologias em constante mudança do setor. As especificações corretas do IC são cruciais para um processo de projeto eficiente e eficaz, por isso é importante garantir que elas sejam estabelecidas adequadamente para garantir o sucesso.

Projeto detalhado

A Fabless apresenta uma solução de design e uma arquitetura de implementação específica de acordo com os requisitos de especificação apresentados pelo cliente e divide as funções do módulo.

Codificação HDL

HDL é uma poderosa linguagem de descrição de hardware para o design de circuitos integrados. Ela fornece um meio eficiente de descrever designs complexos e permite a validação antecipada da funcionalidade do design. HDL é amplamente utilizada na indústria, tornando-se uma tecnologia essencial para os designers de circuitos integrados modernos. A flexibilidade e escalabilidade da HDL tornam-na vantajosa para uso em uma variedade de aplicações e em várias plataformas. Isso permite que os designers desenvolvam projetos de circuitos integrados eficientes e abrangentes, adequados às suas necessidades específicas. A HDL é uma ferramenta crítica para o sucesso de qualquer projeto de circuito integrado e seu uso deve ser fortemente considerado por qualquer designer que deseje criar um circuito integrado de sucesso.

Verificação da simulação

A verificação por simulação é uma etapa essencial no processo de design de circuitos integrados. Ela ajuda os designers a identificar possíveis erros e falhas de design durante a fase de desenvolvimento. Esse processo envolve a execução de simulações e testes nos designs de circuitos integrados para garantir que eles atendam às especificações e padrões exigidos. A verificação por simulação é útil para detectar bugs, resolver problemas de design e otimizar o desempenho do design do circuito integrado. Além disso, ela permite que os designers entendam melhor como seus designs de circuitos integrados se comportarão em condições reais. Portanto, a verificação por simulação desempenha um papel importante para garantir a confiabilidade dos projetos de IC antes de serem implantados na produção.

(ferramenta de verificação de simulação: VCS da Synopsys e NC-Verilog da Cadence.)

Síntese lógica——Compilador de projetos

A verificação da simulação é aprovada e a síntese lógica é realizada. O resultado da síntese lógica é traduzir o código HDL projetado e implementado em uma lista de redes em nível de porta. A síntese precisa definir restrições, que são os padrões que você deseja que o circuito sintetizado atenda em termos de parâmetros de destino, como área e tempo. A síntese lógica precisa ser baseada em uma biblioteca abrangente específica. Em bibliotecas diferentes, a área da célula padrão básica (célula padrão) do circuito de porta e os parâmetros de temporização são diferentes.

Portanto, as bibliotecas abrangentes selecionadas são diferentes e os circuitos sintetizados são diferentes em termos de tempo e área. De modo geral, após a conclusão da síntese, a verificação da simulação precisa ser feita novamente (isso também é chamado de pós-simulação, e a anterior é chamada de pré-simulação).

(Ferramenta de síntese lógica: Design Compiler da Synopsys)

STA

STA, ou análise de temporização estática média, também pertence à categoria de verificação. Ela verifica principalmente o circuito em termos de temporização e verifica se o circuito apresenta violações do tempo de configuração e do tempo de retenção (violação). Esse é o conhecimento básico dos circuitos digitais. Quando essas duas violações de temporização ocorrem em um registro, não há como amostrar e produzir dados corretamente, portanto, haverá definitivamente problemas com a função dos chips digitais baseados em registros.

(A ferramenta STA: Prime Time da Synopsys.)

Verificação formal

Esta é também a categoria de verificação, que consiste em verificar a lista de redes sintetizada a partir da função (STA é temporização). O método mais utilizado é o método de verificação de equivalência. Com o projeto HDL após a verificação funcional como referência, compare as funções da lista de redes após a síntese para ver se são funcionalmente equivalentes. Isso é feito para garantir que a função do circuito descrita pelo HDL original não tenha sido alterada durante o processo de síntese lógica.

(A ferramenta de verificação formal: Synopsys Formality.)

Design de back-end

O design back-end de circuitos integrados é a etapa do processo de design em que o layout físico do circuito é criado. Isso inclui o design das máscaras metálicas, o roteamento das camadas metálicas e outros aspectos físicos do circuito. O design back-end é frequentemente a parte mais longa e detalhada do processo de design e é fundamental para garantir que o circuito funcione corretamente. Isso também pode envolver técnicas avançadas, como o uso de camadas de redistribuição (RDL) para conectividade otimizada.

Transferência de força direcionada

Design For Test, design para testabilidade. Os chips geralmente têm circuitos de teste integrados, e o objetivo do DFT é considerar testes futuros durante o design. Uma abordagem comum ao DFT é inserir cadeias de varredura no design para transformar unidades não varridas (como registros) em unidades varridas. Em relação ao DFT, há introduções detalhadas em alguns livros, por isso é mais fácil compreendê-lo comparando-o com imagens.

(Ferramenta DFT: DFT Compiler da Synopsys)

Planta baixa

O plano de layout consiste em posicionar o módulo macrocelular do chip e, de modo geral, determinar o posicionamento de vários circuitos funcionais, como módulos IP, RAM, pinos de E/S, etc. O plano de layout pode afetar diretamente a área final do chip.

(Ferramentas de planta baixa: Astro da Synopsys)

CTS

Síntese da árvore de clock, síntese da árvore de clock, em termos simples, é a conexão do clock. Devido à função de comando global do sinal de clock no chip digital, sua distribuição deve ser conectada simetricamente a cada unidade de registro, de modo que, quando o clock atinge cada registro da mesma fonte de clock, a diferença de atraso do clock seja a menor possível. É também por isso que os sinais de clock precisam ser roteados separadamente.

(A ferramenta CTS: Compilador Físico da Synopsys.)

Layout e rota

A rota aqui é a fiação de sinal comum, incluindo a fiação entre várias unidades padrão (circuitos lógicos básicos). Por exemplo, o processo de 0,13 um que normalmente ouvimos, ou o processo de 90 nm, é na verdade a largura mínima que a fiação metálica pode atingir aqui, e é o comprimento do canal do tubo MOS de um ponto de vista microscópico.

(A ferramenta de roteamento: Astro da Synopsys)

Extração parasitária

A extração parasitária do projeto de IC é um processo importante no desenvolvimento de circuitos integrados. É um processo de extração de elementos parasitários, como capacitância, indutância e resistência, do layout físico do circuito. Esse processo é fundamental para garantir que o projeto do IC atenda aos requisitos de desempenho desejados pelo usuário. A precisão da extração parasitária também desempenha um papel fundamental para garantir que o projeto se comporte conforme o esperado. No geral, a extração parasitária do design de IC é uma etapa crucial para obter um bom desempenho operacional de um circuito integrado.

(Ferramenta de extração parasitária: Synopsys Star-RCXT)

Verificação física

A verificação física do layout do circuito integrado é uma etapa crucial no processo de design de IC. Ela ocorre após o design esquemático e normalmente envolve o uso da verificação LVS (Layout vs Schematic), DRC (Design Rule Checker) e ERC (Electrical Rule Checker). A verificação LVS verifica se o layout físico corresponde ao projeto esquemático. O DRC verifica se há violações das regras de projeto definidas pelo processo de fabricação, enquanto o ERC verifica se há erros elétricos. Todas essas verificações são importantes para garantir que o projeto esteja correto e pronto para ser fabricado. A verificação física ajuda a garantir que o projeto do IC atenda às especificações e requisitos desejados.

(A ferramenta de verificação física: Hercules da Synopsys)

A conclusão da verificação do layout físico significa que toda a fase de projeto do chip está concluída, e o próximo passo é a fabricação do chip.

Dicas e truques para o design de circuitos integrados

– Compreender detalhadamente os requisitos do projeto.

– Dividir o projeto em blocos e atribuir tarefas.

– Analisar os requisitos de energia e escolher os dispositivos corretos.

– Projetar o circuito cuidadosamente,

tendo em mente as regras de projeto.- Validar o projeto com simulações

.- Depurar o projeto e realizar a otimização do layout.

– Gerar GDS e validar o projeto na placa de destino.

– Use

técnicas de estimativa e otimização de energia.- Escolha

os componentes certos.- Considere as restrições

de tempo e energia.- Use

ferramentas de automação de projeto.- Faça a verificação

e a depuração do projeto.- Aproveite

as ferramentas avançadas de projeto de IC.- Use o projeto

hierárquico para projetos complexos.- Esteja atento às compensações entre energia, área e desempenho.

– Projete para testabilidade e depurabilidade.

– Crie uma documentação de projeto abrangente.