FPGA, abreviação de Field Programmable Gate Array (matriz de portas programáveis em campo), é uma arquitetura de hardware reconfigurável. Em outras palavras, é um chip que pode ser programado para alterar sua estrutura interna. Os FPGAs têm sido usados há muitos anos como substitutos de baixo volume para chips específicos para aplicações (ASICs).

Estrutura básica do FPGA

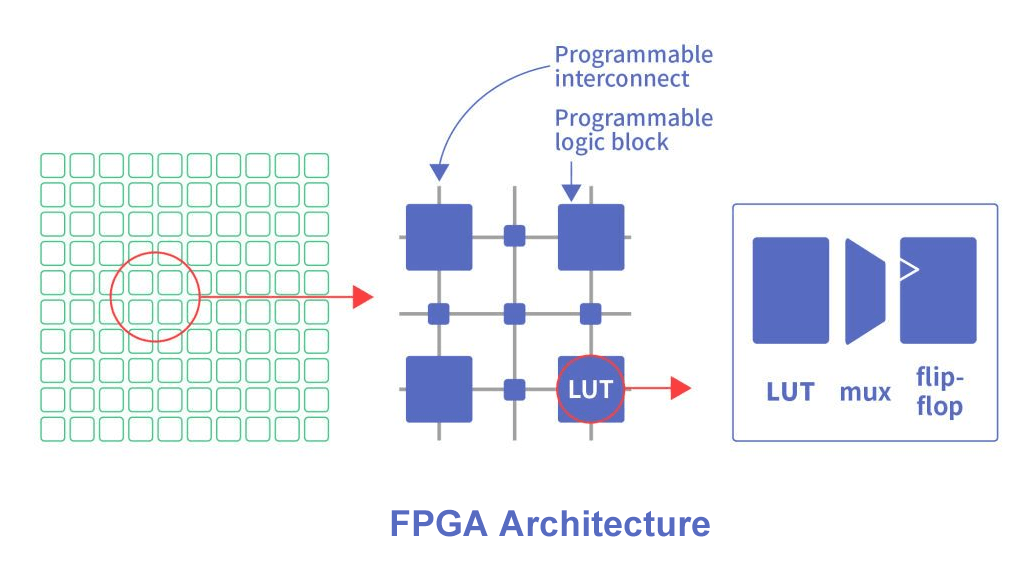

A arquitetura FPGA inclui principalmente quatro partes: bloco lógico configurável (CLB), bloco de entrada e saída (IOB), fiação interna (Interconnect) e outras unidades incorporadas. A estrutura interna do dispositivo FPGA é mostrada abaixo.

Bloco Lógico Configurável (CLB)

CLB é a unidade lógica básica do FPGA. O número real e as características variam de dispositivo para dispositivo, mas cada CLB contém uma matriz de comutação configurável de 4 ou 6 entradas, vários circuitos de seleção (multiplexadores, etc.) e flip-flops.

Bloco de Entrada e Saída (IOB)

Os FPGAs podem suportar muitos padrões de E/S, tornando-os uma ponte de interface ideal para projetos de sistemas. A E/S no FPGA é agrupada por banco, e cada banco pode suportar independentemente diferentes padrões de E/S. Atualmente, o FPGA mais avançado oferece mais de dez bancos de E/S, que podem fornecer suporte flexível de E/S.

Fiação interna (interconexão)

Os CLBs fornecem o desempenho lógico, e o roteamento de interconexão flexível é responsável por passar os sinais entre os CLBs e as E/S. Existem vários tipos de roteamento, desde interconexões CLB dedicadas (recursos de fios curtos) até fios longos horizontais e verticais de alta velocidade (recursos de fios longos) dentro do dispositivo, até roteamento global de baixo desvio para relógios e outros sinais globais (recursos de roteamento globais dedicados).

Unidades incorporadas

As unidades de núcleo rígido incorporadas incluem RAM, DSP, DCM (Módulo de Gerenciamento de Relógio Digital) e outros núcleos rígidos de interface específicos, etc.

Recursos do FPGA

- Usando FPGA para projetar circuitos ASIC, o ciclo é curto, o custo é baixo, o risco é pequeno e a qualidade é estável;

- O FPGA adota tecnologia CHMOS de alta velocidade com baixo consumo de energia;

- Arquitetura FPGA, unidade lógica flexível, alta integração, ampla gama de aplicações;

- O FPGA é compatível com as vantagens do PLD e do gate array geral e pode realizar circuitos em grande escala;

- É possível reprogramar no local e o custo de manutenção posterior é baixo;

- O FPGA é uma computação paralela que pode atender a requisitos multifuncionais ao mesmo tempo.

Como funciona o FPGA?

O FPGA implementa funções lógicas carregando dados de programação em unidades de armazenamento estáticas internas. O valor armazenado na unidade de armazenamento determina a função lógica da unidade lógica e o modo de conexão entre cada módulo da unidade lógica ou entre o módulo e a E/S, e finalmente determina a função realizada pelo FPGA. O FPGA usa uma pequena tabela de consulta para implementar a lógica combinacional, cada tabela de consulta é conectada à entrada de um flip-flop D, e o flip-flop D é usado para acionar outros circuitos lógicos ou E/S, formando assim uma função lógica combinada e realizando o módulo básico da unidade lógica da função lógica sequencial. Esses módulos são conectados entre si ou ao módulo E/S por fios metálicos.

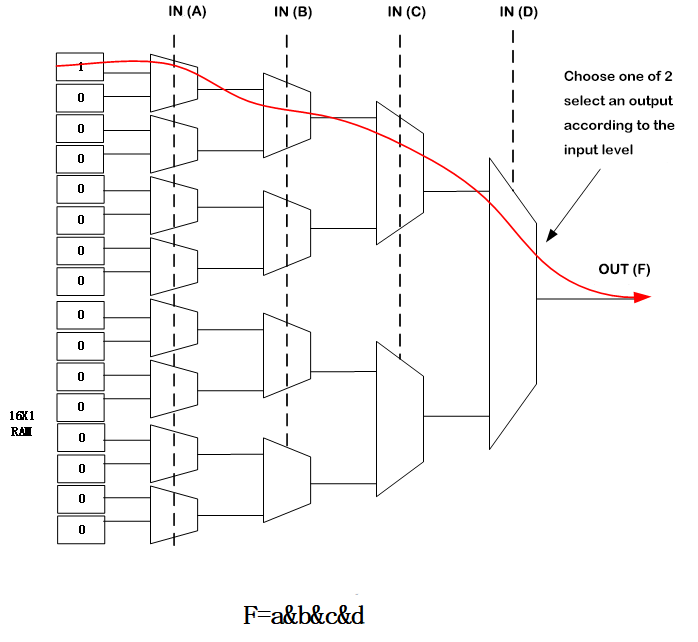

Aqui está um exemplo simples para explicar o princípio do FPGA:

Conforme mostrado na figura acima, configuramos 16bitRAM como 0000000000000001, e este circuito é equivalente a F=A&B&C&D;

Somente quando A=B=C=D=1, F=1, caso contrário, F=0;

"0000000000000001" Esta sequência de números é a programação FPGA.

Bloco lógico do FPGA

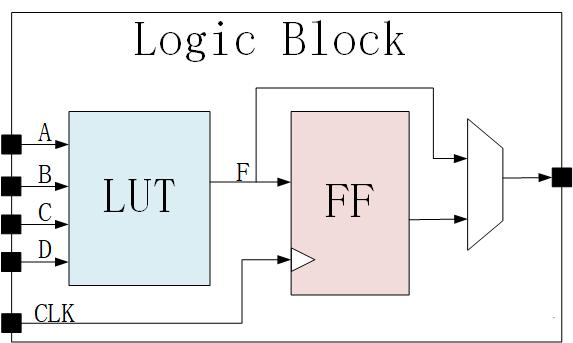

Existe um termo específico em FPGA, chamado LUT, tabela de consulta (lookup table).

A LUT constitui a unidade mais básica de qualquer FPGA.

A LUT só pode implementar lógica combinacional digital, por isso é adicionado um flipflop de registo (ff) para realizar o bloqueio de dados;

Conforme mostrado na figura abaixo: LUT + registros formam a estrutura básica dos FPGAs modernos.

Processo de desenvolvimento de FPGA

O processo de desenvolvimento de FPGA é o processo de utilização de software de desenvolvimento EDA e ferramentas de programação para desenvolver chips FPGA. O processo de desenvolvimento de FPGA é geralmente mostrado na figura abaixo, incluindo etapas principais, tais como definição de funções/seleção de dispositivos, entrada de projeto, simulação de funções, síntese lógica, layout e roteamento e implementação, programação e depuração.

Definição da função/seleção do dispositivo:

Antes do início do projeto de design FPGA, deve haver uma definição das funções do sistema e uma divisão dos módulos. Além disso, de acordo com os requisitos da tarefa, como a função e a complexidade do sistema, a velocidade de trabalho e os recursos, custos e conexões do próprio dispositivo podem ser distribuídos. Pese aspectos como desempenho e selecione o esquema de design apropriado e o tipo de dispositivo adequado.

Contribuição para o design:

A entrada de design refere-se ao uso da linguagem de descrição de hardware para expressar o sistema ou circuito projetado em código. A linguagem de descrição de hardware mais comumente usada é a Verilog HDL.

Simulação funcional:

A simulação funcional refere-se à verificação da função lógica do circuito projetado pelo usuário antes da síntese lógica. Antes da simulação, é necessário construir uma plataforma de teste e preparar estímulos de teste. Os resultados da simulação gerarão arquivos de relatório e formas de onda de sinal de saída, a partir dos quais as mudanças nos sinais de cada nó podem ser observadas. Se forem encontrados erros, volte ao projeto para revisar o projeto lógico. Ferramentas de simulação comuns incluem ModelSim da Model Tech, VCS da Sysnopsys e outros softwares.

Síntese lógica:

A chamada síntese consiste em transformar a descrição do nível mais alto de abstração na descrição do nível mais baixo. A otimização sintética otimiza as conexões lógicas geradas de acordo com os objetivos e requisitos e torna o projeto hierárquico planar para que o software de layout e roteamento FPGA possa ser implementado. No que diz respeito ao nível atual, a otimização abrangente refere-se à compilação da entrada do projeto em uma lista de redes conectadas logicamente, composta por unidades lógicas básicas, como portas AND, portas OR, portas NOT, RAMs e flip-flops, em vez de circuitos reais em nível de porta.

Layout e implementação:

O layout e o roteamento podem ser entendidos como o uso de ferramentas de implementação para mapear a lógica para os recursos da estrutura do dispositivo de destino, determinar o layout ideal da lógica, selecionar os canais de fiação ligados pela lógica e funções de entrada e saída e gerar os arquivos correspondentes (como arquivos de configuração e relatórios relacionados); a implementação consiste em configurar a lista de redes lógicas gerada pela síntese para um chip FPGA específico. Como apenas o fabricante do chip FPGA conhece melhor a estrutura do chip, o layout e o roteamento devem escolher as ferramentas fornecidas pelo desenvolvedor do chip.

Depuração de programação:

A última etapa do projeto é a programação e a depuração. A programação do chip refere-se à geração de arquivos de dados (arquivos de fluxo de bits, Bitstream Generaon) e ao carregamento dos dados de programação no chip FPGA; depois disso, o teste da placa pode ser realizado. Por fim, baixe o arquivo FPGA (como o arquivo .bit) do computador para o chip FPGA na placa.

FPGA vs. CPU e GPU

Tanto as CPUs quanto as GPUs seguem a arquitetura von Neumann, com decodificação de instruções e memória compartilhada. Em contrapartida, os FPGAs têm uma arquitetura inerentemente diferente, que não depende de instruções nem requer memória compartilhada. A tabela abaixo mostra as diferenças entre eles:

| Feature | FPGA | CPU | GPU |

|---|---|---|---|

| Architecture | Reconfigurable logic | Von Neumann | Von Neumann |

| Instruction | No instructions | Instructions | Instructions |

| Shared Memory | No shared memory | Arbitration and shared memory | Arbitration and shared memory |

| Parallel Processing | Pipeline and data parallelism | Data parallelism | Data parallelism |

| Flexibility | Reprogrammable | Fixed functionality | Fixed functionality |

| Computational Power | Suitable for complex tasks | General-purpose computing | Parallel computing and vector processing |

| Latency | Low latency | Medium latency | Relatively high latency |

| Power Consumption | High power consumption | Medium power consumption | High power consumption |

| Application Areas | Electronics, communication, embedded systems | General-purpose computing | Graphics processing, scientific computing |

Competências necessárias para engenheiros FPGA

- Linguagem Verilog e sua relação com circuitos de hardware

- Ferramentas de desenvolvimento (proficiência em Synplify, vivodo, ISE, Modelsim)

- Familiaridade com o processo de design FPGA (simulação, síntese, layout e roteamento, análise de temporização)

- Proficiência em estimativa de recursos (especialmente a estimativa de slice, lut, ram e outros recursos)

- Proficiência em conceitos básicos (tais como tempo de configuração, tempo de retenção, cálculo de fluxo, cálculo de tempo de atraso, risco competitivo, métodos para eliminar falhas, etc.)

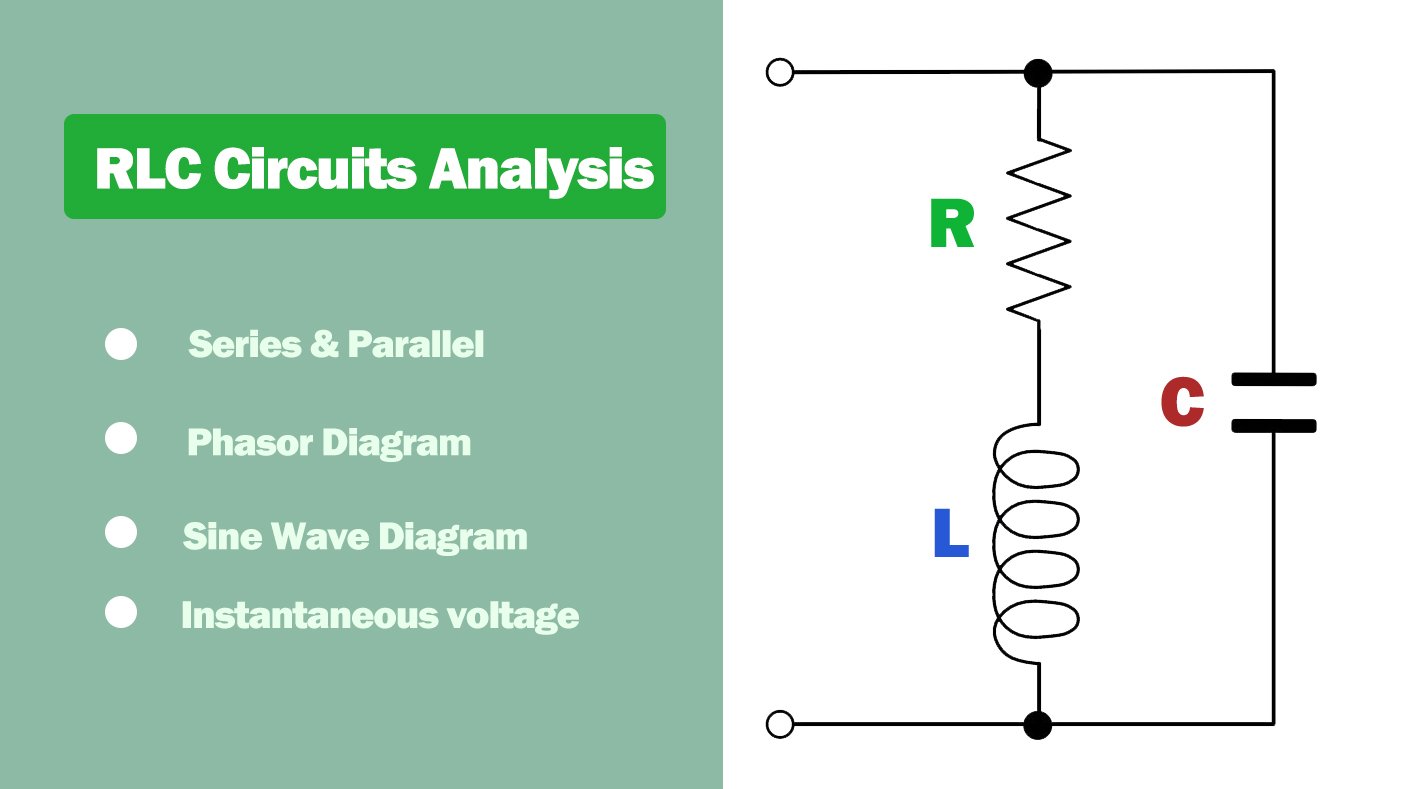

- Circuitos digitais (circuitos combinacionais, flip-flops, especialmente flip-flops D que constituem um divisor de frequência, circuitos sequenciais e podem ser descritos na linguagem Verilog)

Fabricantes de FPGA

- Xilinx: a plataforma de desenvolvimento é ISE, a inventora do FPGA;

- Altera: a plataforma de desenvolvimento é Quartus II, o inventor dos dispositivos lógicos programáveis;

- Actel: a plataforma de desenvolvimento é Libero;

- Lattice: a plataforma de desenvolvimento é ISPLEVER;

- Atmel