Présentation du MSP430F169

Le microcontrôleur MSP430F169 fait partie de la gamme MSP430 de Texas Instruments. Il comprend plusieurs dispositifs dotés de jeux de périphériques distincts conçus pour diverses applications. L'architecture de ces microcontrôleurs, associée à cinq modes basse consommation, a été optimisée pour prolonger l'autonomie des batteries dans les applications de mesure portables. De plus, l'oscillateur à commande numérique (DCO) permet un réveil rapide en moins de 6 µs depuis les modes basse consommation vers le mode actif.

Ces microcontrôleurs trouvent des applications typiques dans les systèmes de capteurs, les applications de contrôle industriel, les compteurs portatifs et d'autres domaines similaires.

Caractéristiques

- Faible consommation d'énergie ;

- Cinq modes d'économie d'énergie ;

- DMA interne à trois canaux ;

- Programmation série intégrée ;

- Protection du code programmable par fusible de sécurité ;

- Avec détecteur de baisse de tension et chargeur d'amorçage ;

- Moniteur de tension d'alimentation avec détection de niveau programmable.

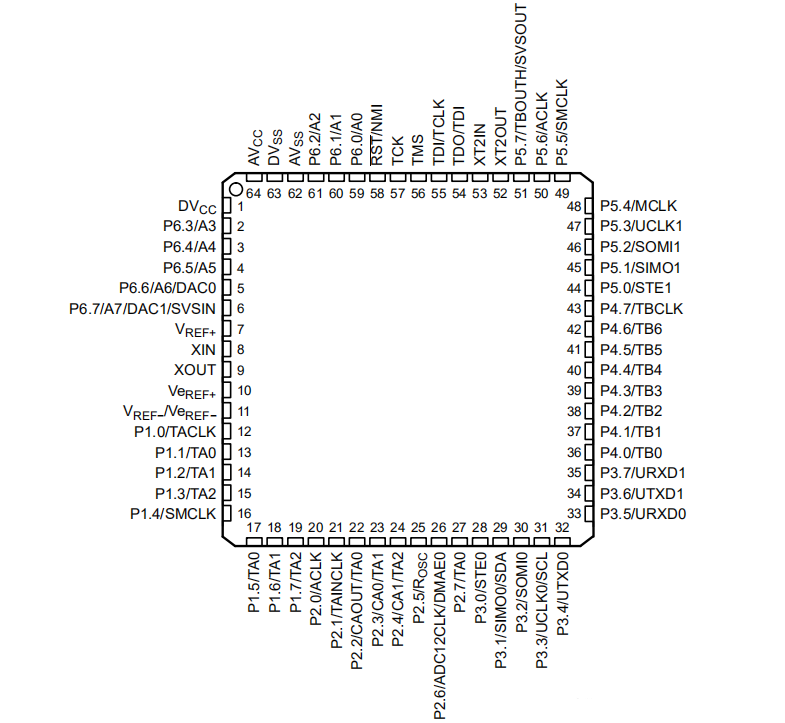

Configuration des broches

Le MSP430F169 est disponible en versions 64 broches et 100 broches, avec des configurations de broches différentes pour chacune.

Pour la version 64 broches, certaines broches clés comprennent :

| Pin Types | Pin Name | Description |

|---|---|---|

| Power Supply Pins | VCC | Positive supply voltage input |

| GND | Ground | |

| RST/NMI | Reset input and non-maskable interrupt | |

| TEST | Test mode input/output | |

| AVSS/AVCC | Ground and voltage reference for ADC | |

| DVSS/DVCC | Ground and voltage reference for digital circuitry | |

| Input/Output Pins | P1.x-P8.x | General-purpose I/O pins |

| Communication Pins | UCA0CLK | USART module A0 clock input/output |

| UCA0STE | USART module A0 STE input/output | |

| UCA0TXD | USART module A0 transmit data output | |

| UCA0RXD | USART module A0 receive data input | |

| UCB0CLK | SPI module B0 clock input/output | |

| UCB0STE | SPI module B0 STE input/output | |

| UCB0SIMO | SPI module B0 transmit data output | |

| UCB0SOMI | SPI module B0 receive data input | |

| UCB0SDA | I2C module B0 data input/output | |

| UCB0SCL | I2C module B0 clock input/output | |

| Timers and Counters | TA0CCR0-TA0CCR6 | Timer A0 capture/compare register 0-6 |

| Timer A0 control register | ||

| TB0CCR0-TB0CCR2 | Timer B0 capture/compare register 0-2 | |

| Timer B0 control register | ||

| Analog Pins | ADC12CLK | ADC12 clock input |

| ADC12MEM0-ADC12MEM15 | ADC12 memory register 0-15 | |

| AVREF+ | Positive reference voltage input for ADC | |

| AVREF- | Negative reference voltage input for ADC | |

| JTAG Pins | TCLK | Test clock input/output |

| TDI | Test data input | |

| TDO | Test data output | |

| Special Function Pins | ACLK | 32.768 kHz crystal oscillator input |

| SMCLK | System master clock output | |

| RTCCLK | Real-time clock input/output |

Spécification

| Specification | Value |

|---|---|

| CPU | 16-bit RISC |

| Frequency | 8 MHz |

| Flash memory | 16 KB |

| RAM | 2 KB |

| Standby power | 1.1 µA |

| Active power | 330 µA at 1 MHz, 2.2 V |

| Wake-up time | in less than 6 µs |

| Instruction cycle time | 125 ns |

| Supply voltage | 1.8 V to 3.6 V |

| A/D converter | 12-bit |

| Timer/Counter | 2 * 16-bit |

| Operating Temp | -40 to 85 ℃ |

| DMA | 3 |

| I2C | 1 |

| SPI | 2 |

| Peripherals | timers, serial ports, I2C |

| Package | 64-pin QFP or 64-pin QFN |

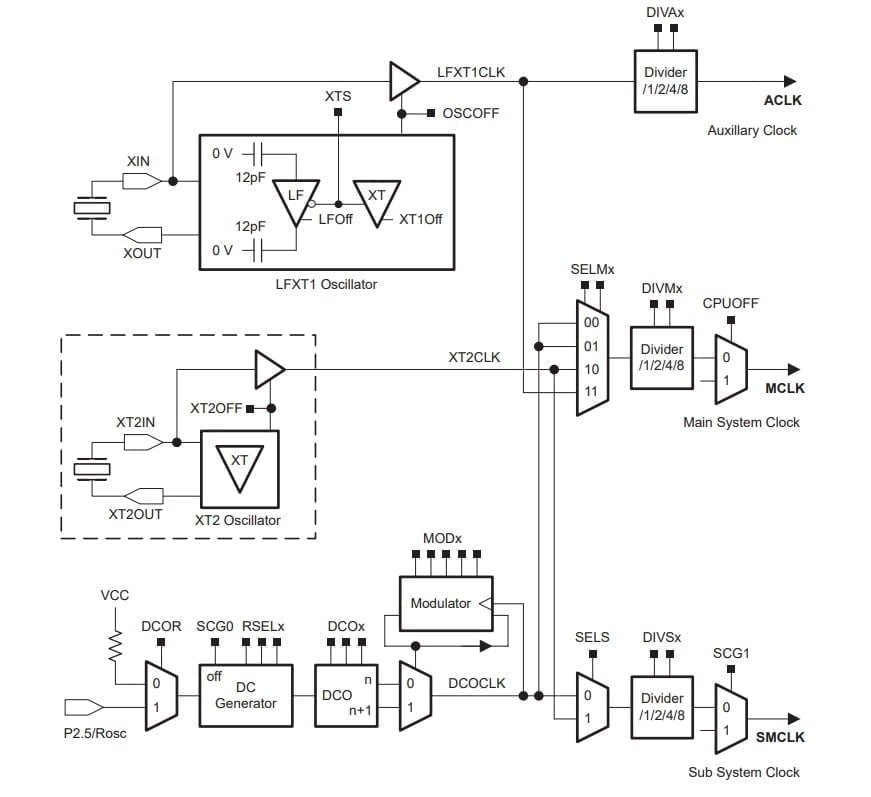

Système d'horloge du MSP430F169

Le système d'horloge est très important pour le micro-ordinateur monopuce. La raison pour laquelle le micro-ordinateur monopuce MSP430F169 a une consommation d'énergie aussi faible est qu'il dispose d'un système d'horloge puissant !

Trois sources de signal d'horloge

1. Basse fréquence LFXT1CLK (32,768 kHz)

Un oscillateur à quartz standard, un oscillateur ou une source d'horloge externe peuvent être utilisés pour entrer une fréquence comprise entre 4 MHz et 32 MHz. XT1CLK peut être utilisé comme horloge de référence pour le module FLL interne.

L'oscillateur à quartz basse fréquence (32,768 kHz) est directement connecté au micro-ordinateur monopuce via les broches XIN et XOUT, et aucun autre dispositif externe n'est nécessaire (il y a une capacité de charge de 12 pF à l'intérieur). À ce moment, l'oscillateur LFXT1 fonctionne en mode basse fréquence (XTS=0).

Si le microcontrôleur est connecté à un oscillateur ou un résonateur haute vitesse, 0SCOFF=0 permet à l'oscillateur LFXT1 de fonctionner en mode haute fréquence (XTS=1). À ce moment-là, l'oscillateur à quartz ou le résonateur haute vitesse est connecté via les broches XIN et XOUT, et un condensateur externe est nécessaire. La taille du condensateur est choisie en fonction des caractéristiques de l'oscillateur à quartz ou du résonateur.

Si le signal LFXT1CLK n'est pas utilisé comme signal SMCLK ou MCIK, le logiciel peut définir OSCOFF=1 pour désactiver le fonctionnement du LFXT1, réduisant ainsi la consommation d'énergie du microcontrôleur.

BCSCTL1 :

XTS(BIT6)——Sélection du mode haute/basse vitesse LFXT1. 0 : LFXT1 fonctionne en mode oscillateur à quartz basse vitesse (par défaut) ; 1 : LFXT1 fonctionne en mode oscillateur à quartz haute vitesse.

2. XT2CLK haute fréquence (8 MHz)

Un oscillateur à quartz standard, un oscillateur ou une source d'horloge externe peuvent être utilisés pour entrer une fréquence comprise entre 4 MHz et 32 MHz.

L'oscillateur XT2 génère le signal d'horloge XT2CLK, et ses caractéristiques de fonctionnement sont similaires à celles de l'oscillateur LFXT1 lorsqu'il fonctionne en mode haute fréquence. Si XT2CLK n'est pas utilisé comme signal d'horloge MCLK et SMCLK, l'oscillateur XT2 peut être désactivé à l'aide du bit de contrôle XT2OFF.

BCSCTL1 :

XT2OFF (BIT7) – Contrôle de l'oscillateur à quartz haute vitesse XT2. 0 : oscillateur à quartz haute vitesse XT2 activé ; 1 : oscillateur à quartz haute vitesse XT2 désactivé.

3. Oscillateur interne DCOCLK (1 MHz)

Stabilisé par le module FLL.

En cas de défaillance de l'oscillateur, le DCO est automatiquement sélectionné comme source d'horloge pour MCLK.

La fréquence de l'oscillateur DCO peut être réglée à l'aide du logiciel en configurant les bits DCOx. MODx et RSEL.x. Lorsque le signal DCOCLK n'est pas utilisé comme signal d'horloge SMCLK et MCLK, le générateur DC peut être désactivé à l'aide du bit de contrôle SCGO.

Après le signal PUC, DCOCLK est automatiquement sélectionné comme signal d'horloge MCLK, et la source d'horloge de MCLK peut être réglée en plus sur LFXT1 ou XT2 selon les besoins. La séquence de configuration est la suivante :

- Let OSCOFF=1;

- Que OFIFG=0 ;

- Attendre au moins 50 ps ;

- Vérifier à nouveau OFIFG, si OFIFG=1, répéter les étapes (3) et (4) jusqu'à ce que OFIFG=0.

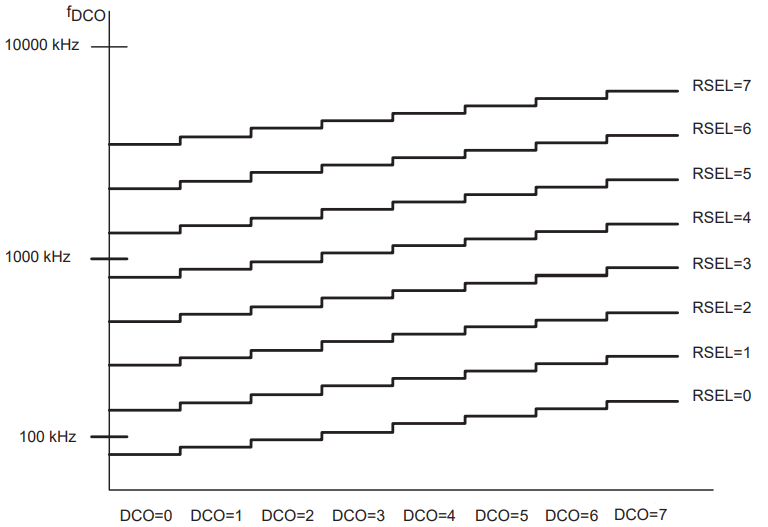

DCOCTL :

DCOx (BIT7, BIT6, BIT5)——Sélection de la fréquence DCO, 8 types de fréquences peuvent être sélectionnés et la fréquence DCOCLK peut être ajustée par sections. La sélection de la fréquence est basée sur la bande de fréquence sélectionnée par RSELx. La relation entre DCOx, RSELx et l'horloge interne est la suivante :

MODx (BIT4, BIT3, BIT2, BIT1, BIT0) – Réglage du modulateur DAC. La commande commute les deux fréquences sélectionnées par DCOx et DCOx+1 pour régler avec précision la fréquence de sortie du DCO. Si la constante DCOx est 7, cela signifie que la fréquence la plus élevée a été sélectionnée. À ce moment, MODx n'est pas valide et ne peut pas être utilisé pour le réglage de la fréquence.

BCSCTL1 :

RSELx (BIT2, BIT1, BIT0) – sélection de la bande de fréquence de l'oscillateur DCO, ces 3 bits contrôlent une résistance interne pour déterminer la fréquence nominale. 0 : sélectionne la fréquence nominale la plus basse… 7 : sélectionne la fréquence nominale la plus élevée.

BCSCTL2 :

DCOR(BIT0)——Sélectionne la résistance de l'oscillateur DCO. 0 : résistance interne ; 1 : résistance externe.

Trois sources d'horloge

1. Horloge auxiliaire ACLK

ACLK est obtenu après division de LFXT1CLK par 1, 2, 4 et 8. Il peut être utilisé comme signal d'horloge de chaque module périphérique et est généralement utilisé pour les périphériques à faible vitesse.

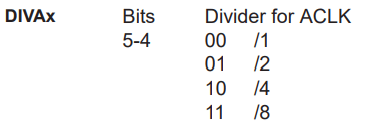

BCSCTL1 :

DIVAx (BIT5, BIT4)——Sélection de la division de fréquence ACLK, la relation de sélection de la division de fréquence est la suivante :

Définition macro : DIVA_0 (1 division de fréquence/aucune division de fréquence), DIVA_1 (2 divisions de fréquence), DIVA_2 (4 divisions de fréquence), DIVA_3 (8 divisions de fréquence)

2. Horloge principale du système MCLK

Le MCLK peut être obtenu à partir du LFXT1CLK, du XT2CLK et du DCOCLK après division de fréquence par 1, 2, 4 et 8. Il est souvent utilisé pour le fonctionnement du CPU, l'exécution de programmes et d'autres modules qui utilisent des horloges à haute vitesse.

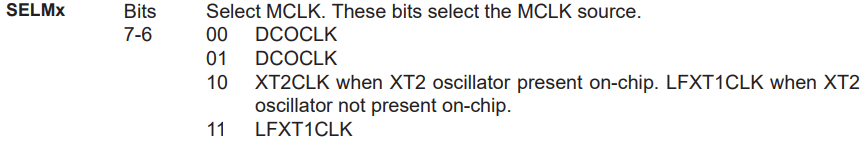

BCSCTL2 :

SELMx (BIT7, BIT6) – sélectionne la source d'horloge MCLK, la relation de sélection d'horloge est la suivante :

Définition macro : SELM_0 (DCOCLK par défaut), SELM_1 (DCOCLK), SELM_2 (XT2CLK), SELM_3 (LFXT1CLK)

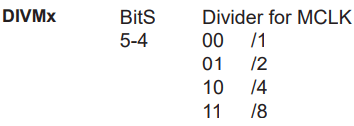

DIVMx (BIT5, BIT4) – Sélection de la division de fréquence MCLK, la relation de sélection de la division de fréquence est la suivante :

Définition macro : DIVM_0 (1 division de fréquence/aucune division de fréquence), DIVM_1 (2 divisions de fréquence), DIVM_2 (4 divisions de fréquence), DIVM_3 (8 divisions de fréquence)

3. Horloge du sous-système SMCLK

SMCLK peut être obtenu par division de fréquence de XT2CLK et DCOCLK par 1, 2, 4 et 8, et est souvent utilisé dans les modules périphériques à haute vitesse.

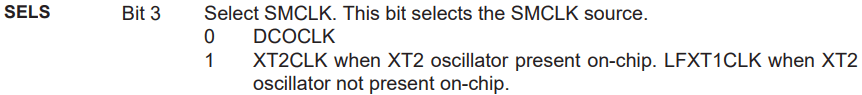

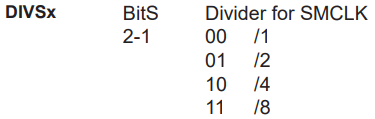

BCSCTL2 :

SELSx (BIT3) – sélectionnez la source d'horloge MCLK, la relation de sélection d'horloge est la suivante :

DIVSx (BIT2, BIT1) – Sélection de la division de fréquence SMCLK, la relation de sélection de la division de fréquence est la suivante :

Définition macro : DIVS_0 (1 division de fréquence/aucune division de fréquence), DIVS_1 (2 divisions de fréquence), DIVS_2 (4 divisions de fréquence), DIVS_3 (8 divisions de fréquence)