Dalam beberapa tahun terakhir, teknologi redistribution layer (RDL) semakin populer. Ini adalah solusi pengemasan revolusioner yang telah mengubah cara kita mengemas IC.

Dalam artikel ini, kita akan membahas definisi RDL, fungsinya, manfaatnya, prosesnya, aplikasinya, serta perbandingannya dengan teknologi pengemasan IC lainnya.

Apa itu Teknologi Lapisan Redistribusi?

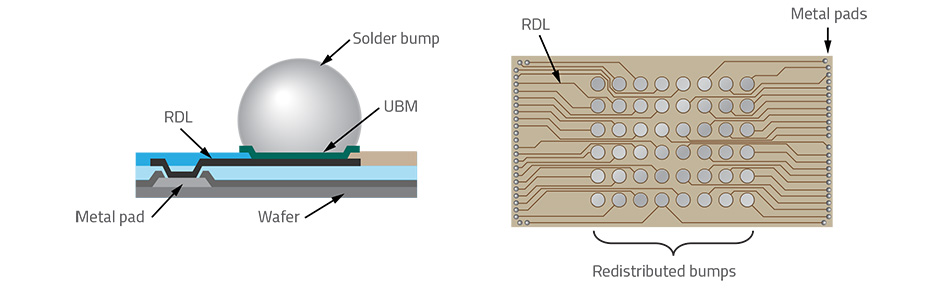

Lapisan redistribusi, yang juga dikenal sebagai RDL, adalah lapisan logam yang ditambahkan ke sirkuit terpadu atau mikrochip untuk mendistribusikan ulang sambungan listrik. Teknologi RDL ini merupakan solusi pengemasan canggih untuk sirkuit terpadu (IC), yang memungkinkan integrasi beberapa die ke dalam satu kemasan. Ini adalah proses pembuatan lapisan logam berpola di atas lapisan dielektrik, yang mendistribusikan ulang input/output (I/O) IC ke lokasi baru. Lokasi baru tersebut biasanya berada di tepi die, yang memungkinkan IC terhubung ke papan sirkuit cetak (PCB) menggunakan teknologi pemasangan permukaan standar (SMT). Teknologi RDL memungkinkan perancang menempatkan die secara kompak dan efisien, sehingga mengurangi jejak keseluruhan perangkat.

Teknologi RDL memegang peranan penting dalam pengembangan perangkat elektronik modern yang semakin ringkas dan kompleks. Teknologi ini memungkinkan chip menjadi lebih kecil, lebih cepat, dan lebih efisien. Teknologi ini umumnya digunakan dalam proses pengemasan perangkat MEMS, sensor, perangkat daya, memori, mikroprosesor, dan prosesor grafis.

Fungsi Lapisan Redistribusi

Lapisan redistribusi (RDL) memainkan peran penting dalam memperluas dan menghubungkan bidang XY dalam desain dan manufaktur chip.

Mengarahkan Ulang Koneksi I/O

Pad I/O (input/output) adalah modul pemrosesan pin chip yang biasanya tersebar di tepi atau pinggiran chip. Modul ini dapat memproses sinyal dari pin chip dan mengeluarkan sinyal chip ke pin setelah diproses.

RDL dapat memfasilitasi redistribusi koneksi I/O dari chip ke kemasan. RDL menghubungkan pad ikatan pada chip ke kabel atau bola kemasan, yang memungkinkan perakitan yang lebih mudah dan kinerja IC yang lebih baik.

Hal ini tentu saja memudahkan proses kabel pengikat, tetapi agak menantang untuk chip flip. Oleh karena itu, RDL menjadi kunci pada saat ini. RDL mengendapkan lapisan logam dan lapisan dielektrik yang sesuai pada permukaan chip, membentuk kabel logam dan mendesain ulang port IO ke area baru yang lebih luas, membentuk tata letak susunan permukaan.

Sinyal dan Daya Jalur

Selain itu, RDL juga berfungsi sebagai sarana untuk mengalirkan sinyal dan daya di dalam IC. Penggunaan RDL semakin penting seiring dengan meningkatnya kompleksitas IC dan kebutuhan akan koneksi I/O yang lebih banyak. RDL digunakan dalam berbagai macam aplikasi, seperti mikroprosesor, chip memori, dan sensor.

Manfaat Lapisan Redistribusi

Teknologi RDL menawarkan sejumlah manfaat bagi para perancang yang ingin menciptakan perangkat elektronik berkinerja tinggi, ringkas, dan hemat biaya. Beberapa manfaat penggunaan teknologi RDL pada kemasan IC adalah:

Jejak Karbon yang Lebih Kecil

Teknologi RDL memungkinkan integrasi beberapa chip ke dalam satu kemasan, sehingga mengurangi ukuran keseluruhan perangkat. Hal ini memungkinkan para perancang untuk menciptakan perangkat elektronik yang lebih kecil dan ringkas, yang sangat penting untuk aplikasi seperti ponsel pintar, perangkat yang dapat dikenakan, dan perangkat IoT.

Peningkatan Kinerja Listrik

Teknologi RDL memungkinkan perancang untuk menempatkan chip secara ringkas dan efisien, sehingga dapat memperpendek panjang jalur interkoneksi. Hal ini, pada gilirannya, mengurangi penundaan sinyal dan meningkatkan kinerja listrik perangkat. Teknologi RDL juga mengurangi kapasitansi dan induktansi parasit, yang pada gilirannya meningkatkan integritas sinyal perangkat.

Biaya yang Lebih Rendah

Teknologi RDL menghilangkan kebutuhan akan proses wire bonding dan flip-chip bonding, yang merupakan proses yang mahal dan memakan waktu. Teknologi RDL juga mengurangi jumlah komponen yang diperlukan untuk perangkat tersebut, sehingga semakin menekan biaya perangkat. Teknologi RDL merupakan solusi hemat biaya untuk membuat IC berkinerja tinggi yang membutuhkan bentuk fisik yang ringkas.

Jenis-jenis Teknologi Lapisan Redistribusi

Ada dua jenis teknologi lapisan redistribusi (RDL): fan-in dan fan-out. Teknologi RDL fan-in digunakan untuk mengemas satu chip, sedangkan teknologi RDL fan-out digunakan untuk mengemas beberapa chip.

Teknologi Fan-in RDL

Teknologi fan-in RDL digunakan untuk mengemas satu chip. Teknologi fan-in RDL juga dikenal sebagai wafer-level package (WLP), yaitu proses pembuatan kemasan langsung di atas wafer. Teknologi fan-in RDL merupakan solusi hemat biaya untuk membuat kemasan yang kecil dan tipis.

Teknologi fan-in RDL cocok untuk aplikasi seperti sensor, perangkat MEMS, perangkat RF, mikroprosesor, dan perangkat memori.

Teknologi RDL Fan-out

Teknologi fan-out RDL digunakan untuk mengemas beberapa chip. Teknologi fan-out RDL juga dikenal sebagai wafer-level fan-out (WLFO), yaitu proses pembuatan kemasan pada wafer yang telah direkonstruksi. Teknologi fan-out RDL merupakan solusi hemat biaya untuk membuat kemasan berkinerja tinggi dengan bentuk yang ringkas.

Teknologi fan-out RDL cocok untuk aplikasi seperti prosesor grafis, sistem-on-chip (SoC), perangkat memori, perangkat daya, dan perangkat LED.

Proses Lapisan Redistribusi

Teknologi RDL merupakan proses yang kompleks yang melibatkan banyak tahap, seperti pengendapan dielektrik, pengendapan logam, pembentukan pola, dan pengikisan. Berikut ini adalah alur proses untuk Fan-in RDL dan Fan-out RDL.

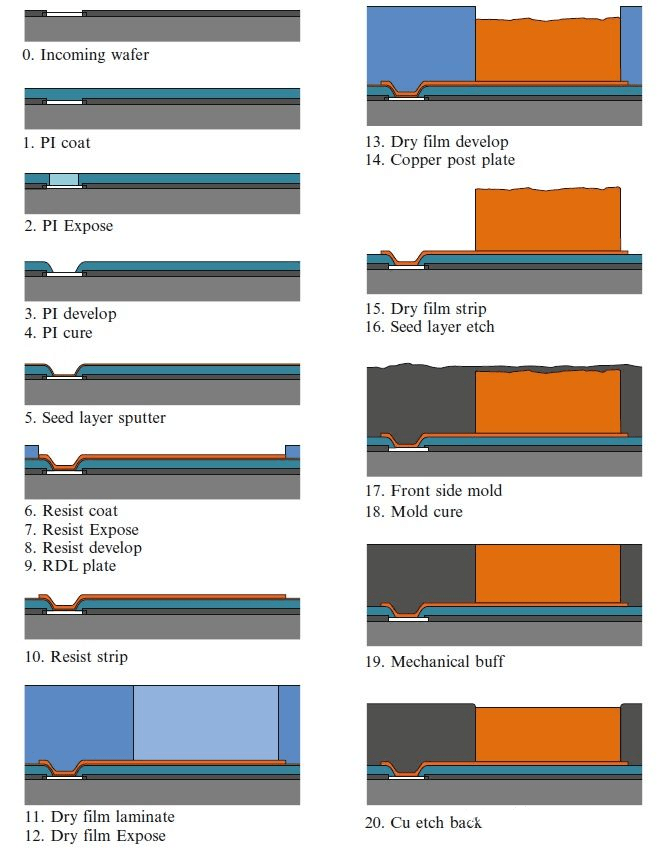

Proses Fan-in RDL

Proses Fan-in RDL digunakan dalam produksi solusi pengemasan canggih seperti Wafer-Level Chip-Scale Packaging (WLCSP) dan desain System-in-Package (SiP). Proses ini memungkinkan tingkat integrasi yang lebih tinggi, ukuran yang lebih ringkas, serta peningkatan kinerja perangkat semikonduktor. Proses ini melibatkan beberapa langkah sebagai berikut:

Proses ini dimulai dengan wafer yang masuk, yang kemudian dilapisi dengan PI (Photoresist Insulator) pada langkah 1. Selanjutnya dilakukan pemaparan PI pada langkah 2, pengembangan PI pada langkah 3, dan pengeringan PI pada langkah 4.

Pada langkah 5, lapisan benih disemprotkan ke wafer, yang kemudian dilapisi dengan resist pada langkah 6. Resist tersebut kemudian diekspos pada langkah 7, dikembangkan pada langkah 8, dan RDL dilapisi pada langkah 9.

Setelah itu, resist dihilangkan pada langkah 10, dan film kering dilaminasi ke atas wafer pada langkah 11. Film kering tersebut kemudian diekspos pada langkah 12 dan dikembangkan pada langkah 13. Selanjutnya, tiang tembaga dilapisi ke atas wafer pada langkah 14, dan film kering dihilangkan pada langkah 15.

Pada langkah 16, lapisan benih (seed layer) dietch, dan pada langkah 17, cetakan sisi depan (front side mold) dibuat. Cetakan tersebut kemudian dikeringkan pada langkah 18, dan wafer dipoles secara mekanis pada langkah 19. Akhirnya, pada langkah 20, tembaga berlebih dietch kembali, menyelesaikan alur proses Fan-in RDL.

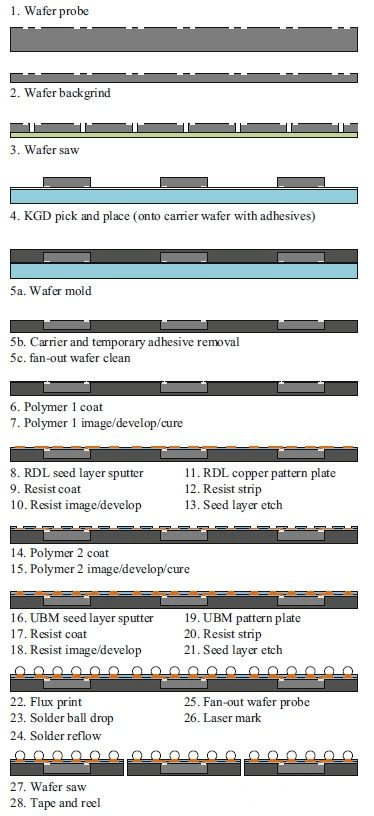

Proses RDL Fan-out

Sama seperti proses Fan-in RDL, proses Fan-out RDL juga merupakan cara untuk membuat kemasan chip yang lebih kecil dan berkinerja lebih tinggi dengan jumlah koneksi yang lebih banyak. Berikut adalah langkah-langkah pembuatannya:

1. Pengujian wafer: Ini adalah tahap pengujian awal wafer untuk memastikan bahwa wafer tersebut memenuhi spesifikasi yang disyaratkan sebelum dilanjutkan ke tahap pemrosesan berikutnya.

2. Penggerindaan bagian belakang wafer: Bagian belakang wafer digerinda hingga ketebalan yang ditentukan untuk mengurangi ketebalan kemasan.

3. Pemotongan wafer: Wafer dipotong menjadi die-die individual.

4. Pemilihan dan penempatan KGD (Known Good Die): Die yang baik diambil dan dipindahkan ke wafer pembawa dengan perekat.

5a. Cetakan wafer: Wafer dengan die yang terpasang pada wafer pembawa dicetak dengan bahan dielektrik untuk membentuk struktur fan-out.

5b. Penghapusan pembawa dan perekat sementara: Wafer pembawa dilepas dari wafer fan-out, dan perekat sementara yang digunakan selama proses juga dihilangkan.

5c. Pembersihan wafer fan-out: Wafer fan-out dibersihkan untuk menghilangkan partikel atau kotoran yang tersisa.

6. Lapisan polimer 1: Lapisan polimer diaplikasikan ke permukaan wafer fan-out untuk berfungsi sebagai lapisan dielektrik.

7. Polimer 1 gambar/pengembangan/pengeringan: Lapisan polimer dipola menggunakan fotolitografi untuk menciptakan bentuk dan ukuran struktur RDL yang diinginkan.

8. Sputtering lapisan benih RDL: Lapisan tipis tembaga atau bahan konduktif lainnya diendapkan di atas lapisan polimer menggunakan sputtering.

9. Lapisan resist: Lapisan bahan resist diaplikasikan di atas lapisan benih.

10. Pembentukan pola resist/pengembangan: Lapisan resist dipola menggunakan fotolitografi untuk menciptakan bentuk dan ukuran struktur RDL yang diinginkan.

11. Pelat pola tembaga RDL: Tembaga diendapkan di atas area lapisan benih yang terpapar menggunakan pelapisan listrik, sehingga menciptakan pola RDL yang diinginkan.

12. Penghapusan resist: Bahan resist yang tersisa dihilangkan, sehingga hanya menyisakan pola RDL tembaga.

13. Pengikisan lapisan benih: Bagian lapisan benih yang tidak diperlukan dihilangkan menggunakan pengikisan.

14. Lapisan polimer 2: Lapisan polimer lain diaplikasikan di atas struktur RDL untuk berfungsi sebagai lapisan dielektrik.

15. Gambar/pengembangan/pengeringan polimer 2: Lapisan polimer dipola menggunakan fotolitografi untuk menciptakan bentuk dan ukuran struktur UBM yang diinginkan.

16. Sputtering lapisan benih UBM: Lapisan tipis tembaga atau bahan konduktif lainnya diendapkan di atas lapisan polimer menggunakan sputtering.

17. Lapisan resist: Lapisan bahan resist diaplikasikan di atas lapisan benih.

18. Pembuatan pola/pengembangan resist: Lapisan resist dipola menggunakan fotolitografi untuk menciptakan bentuk dan ukuran struktur UBM yang diinginkan.

19. Pelat pola UBM: Tembaga diendapkan di atas area lapisan benih yang terbuka menggunakan pelapisan listrik, sehingga menciptakan pola UBM yang diinginkan.

20. Penghapusan resist: Bahan resist yang tersisa dihilangkan, sehingga hanya menyisakan pola UBM tembaga.

21. Pengikisan lapisan benih: Bagian lapisan benih yang tidak diperlukan dihilangkan menggunakan pengikisan.

22. Pencetakan fluks: Bahan fluks diaplikasikan ke bantalan UBM.

23. Penempatan bola timah: Bola timah ditempatkan pada pad UBM.

24. Refluks solder: Bola-bola solder dipanaskan hingga meleleh dan membentuk sambungan antara bantalan UBM dan kabel eksternal atau tonjolan.

25. Pengujian wafer fan-out: IC yang telah dikemas diuji untuk memastikan bahwa IC tersebut memenuhi spesifikasi yang disyaratkan.

26. Penandaan laser: Pengenal unik atau kode batang diukir pada permukaan IC menggunakan laser.

27. Pemotongan wafer: Wafer fan-out dipotong menjadi paket-paket individual.

28. Pita dan gulungan: IC yang telah dikemas secara individual dipasang pada gulungan untuk memudahkan penanganan dan pengiriman.

Menerapkan RDL pada Kemasan Canggih

Dalam kemasan tingkat lanjut seperti fan-in wafer-level package (FIWLP) dan fan-out wafer-level package (FOWLP), RDL merupakan teknologi yang paling krusial. Kemunculan teknologi inilah yang memungkinkan pabrik kemasan bersaing dengan pabrik wafer dalam teknologi kemasan fan-out. Melalui RDL, IOPad dapat diolah menjadi berbagai jenis kemasan tingkat wafer dalam bentuk FIWLP atau FOWLP. Dalam FIWLP, semua bump ditumbuhkan di atas die, dan koneksi antara die dan pad terutama bergantung pada jalur logam RDL. Setelah pengemasan, IC memiliki ukuran yang hampir sama dengan area die. Dalam FOWLP, bump dapat ditumbuhkan di luar die, dan IC setelah pengemasan berukuran lebih besar dari area die (1,2 kali lipat).

Secara khusus, dalam kemasan canggih 2.5D, selain TSV pada substrat silikon, RDL juga tidak dapat dipisahkan. Mengambil contoh InFO dari TSMC, yang merupakan perwakilan dari kemasan canggih 2.5D, InFO menggunakan satu atau lebih die telanjang pada carrier, yang kemudian disematkan dalam wafer yang direkonstruksi dari bahan cetakan. Kemudian, interkoneksi RDL dan lapisan dielektrik diproduksi pada wafer, yang merupakan alur proses "chip first". InFO single-die menyediakan jumlah bump yang tinggi, dan jalur RDL memanjang dari area chip ke luar, membentuk topologi "fan-out".

Teknologi Lapisan Redistribusi mana yang sebaiknya saya gunakan?

Seperti yang telah kami sebutkan sebelumnya, terdapat dua jenis teknologi RDL: Fan-in RDL dan Fan-out RDL. Lalu, bagaimana cara memilih yang tepat untuk membuat perangkat elektronik berkinerja tinggi, ringkas, dan hemat biaya? Hal ini bergantung pada beberapa faktor, seperti jenis aplikasi, jumlah chip, dan persyaratan kinerja.

Aplikasi

Teknologi RDL tipe fan-in cocok untuk aplikasi seperti sensor, perangkat MEMS, dan perangkat RF. Teknologi RDL tipe fan-out cocok untuk aplikasi seperti prosesor grafis, sistem-on-chip (SoC), dan perangkat memori.

Jumlah cetakan

Teknologi RDL tipe fan-in cocok untuk pengemasan satu chip, sedangkan teknologi RDL tipe fan-out cocok untuk pengemasan beberapa chip.

Persyaratan Kinerja

Teknologi RDL tipe fan-in cocok untuk membuat kemasan yang kecil dan tipis, sedangkan teknologi RDL tipe fan-out cocok untuk membuat kemasan berkinerja tinggi dengan bentuk yang ringkas.

Perbandingan RDL dengan Teknologi Pengemasan IC Lainnya

Karena proses yang berbeda-beda, terdapat beberapa teknologi pengemasan yang tersedia untuk sirkuit terpadu. Informasi lebih lanjut mengenai perbedaannya dapat dilihat pada tabel di bawah ini:

| IC Packaging | Description | Advantages | Disadvantages | Applications |

|---|---|---|---|---|

| Wire Bonding | Connecting the IC to the PCB using wires | Low cost, flexible, proven technology | Limited performance, not suitable for high-frequency and high-power applications | Consumer electronics, automotive, medical devices |

| Flip-Chip Bonding | Chips are bonded face-down to the substrate, Connecting the IC to the PCB using solder bumps | High performance, high-density, low inductance | Expensive, requires precise alignment and underfilling | High-speed data communication, high-power applications, microprocessors |

| Through-Silicon Via (TSV) | Creating vertical interconnects through the silicon substrate | Shorter interconnect lengths, higher performance, smaller form factor | Complex and expensive manufacturing process, thermal and mechanical stress issues | Memory devices, image sensors, 3D ICs |

| Chip-scale package (CSP) | Replacing the lead frame with a substrate | Small form factor, high density, low cost | Limited I/O, susceptibility to mechanical and thermal stress | Mobile devices, wearable technology |

| Integrated Fan-out (InFO) | Integrated package of multiple chips and the soldering point of the pin is outside of the chip | High density, small form factor, low power consumption | Complex manufacturing process, high cost | Mobile devices, IoT, wearable technology |

| High Bandwidth Memory (HBM) | 3D stacking technology | High bandwidth, low power consumption | Expensive, limited scalability | High-performance computing, graphics processing |

| Chip on Wafer on Substrate (CoWoS) | Integrate chip and silicon wafer (substrate) together | High bandwidth, low power consumption, heterogeneous integration | Complex manufacturing process, high cost | High-performance computing, graphics processing |

| Redistribution Layer (RDL) | Creating a patterned metal layer on top of the dielectric layer | High density, fine pitch, low profile | Limited power handling capability, susceptibility to mechanical and thermal stress | Mobile devices, consumer electronics |

| Bump Technology | Depositing small metal bumps on the chip | Low cost, simple manufacturing process, flexible design | Limited performance, not suitable for high-speed and high-power applications | Consumer electronics, automotive, medical devices |

Perusahaan yang Menyediakan Solusi Teknologi Lapisan Redistribusi

Ada beberapa perusahaan yang menawarkan solusi teknologi redistribution layer (RDL), seperti:

Grup ASE

ASE Group adalah penyedia layanan manufaktur semikonduktor berskala global. ASE Group menawarkan beragam solusi teknologi RDL untuk berbagai aplikasi, seperti memori, mikroprosesor, dan prosesor grafis.

Amkor Technology

Amkor Technology adalah penyedia layanan pengemasan dan pengujian semikonduktor berskala global. Amkor Technology menawarkan beragam solusi teknologi RDL untuk berbagai aplikasi, seperti sensor, perangkat MEMS, dan perangkat daya.

Perusahaan Manufaktur Semikonduktor Taiwan

TSMC adalah perusahaan manufaktur semikonduktor global yang menawarkan beragam solusi teknologi RDL untuk berbagai aplikasi, seperti sistem-on-chip (SoC), perangkat memori, dan perangkat daya.

Kesimpulan

Teknologi redistribution layer (RDL) merupakan solusi pengemasan revolusioner yang telah mengubah cara kita mengemas sirkuit terpadu (IC). Teknologi ini memungkinkan lebih banyak koneksi dibuat pada satu chip, sehingga mengurangi ukuran fisik perangkat secara keseluruhan. Oleh karena itu, teknologi ini digunakan dalam berbagai aplikasi seperti ponsel pintar, perangkat yang dapat dikenakan, dan perangkat IoT. Masa depan teknologi RDL dalam kemasan IC sangat menjanjikan, dan diperkirakan akan memberikan dampak signifikan pada industri elektronik dalam beberapa tahun mendatang.