En los últimos años, la tecnología de capa de redistribución (RDL) ha ganado un gran impulso. Se trata de una solución de encapsulado revolucionaria que ha transformado la forma en que encapsulamos los circuitos integrados.

En este artículo, exploraremos la definición de RDL, su función, sus ventajas, su proceso, su aplicación y su comparación con otras tecnologías de encapsulado de circuitos integrados.

¿Qué es la tecnología de capa de redistribución?

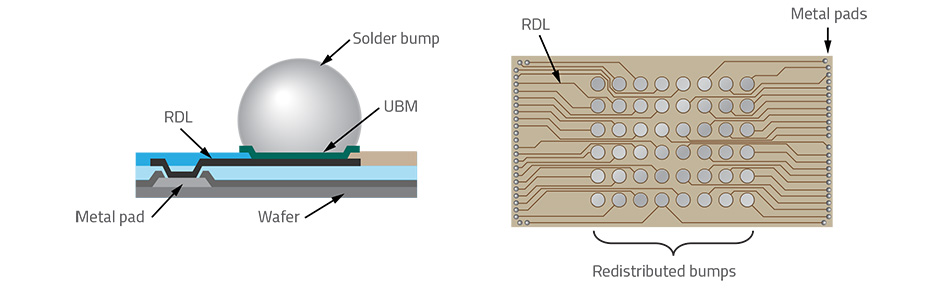

La capa de redistribución, también conocida como RDL, es una capa de metal que se añade a un circuito integrado o microchip para redistribuir las conexiones eléctricas. Esta tecnología RDL es una solución avanzada de encapsulado para circuitos integrados (IC), que permite la integración de múltiples matrices en un solo encapsulado. Se trata de un proceso de creación de una capa metálica con un patrón sobre la capa dieléctrica, que redistribuye la entrada/salida (E/S) del IC a una nueva ubicación. La nueva ubicación suele estar en el borde del chip, lo que permite conectar el IC a la placa de circuito impreso (PCB) utilizando la tecnología de montaje superficial (SMT) estándar. La tecnología RDL permite al diseñador colocar el chip de forma compacta y eficiente, reduciendo así el espacio total que ocupa el dispositivo.

La tecnología RDL es fundamental en el desarrollo de los dispositivos electrónicos modernos, cada vez más compactos y complejos. Permite que los chips sean más pequeños, rápidos y eficientes. Se utiliza habitualmente en el encapsulado de dispositivos MEMS, sensores, dispositivos de potencia, memorias, microprocesadores y procesadores gráficos.

Función de la capa de redistribución

La capa de redistribución (RDL) desempeña un papel fundamental en la ampliación e interconexión del plano XY en el diseño y la fabricación de chips.

Redistribuir la conexión de E/S

Las almohadillas de E/S (entrada/salida) son módulos de procesamiento de pines de chip que suelen distribuirse en el borde o la periferia del chip. Pueden procesar la señal de los pines del chip y enviar la señal del chip al pin después del procesamiento.

El RDL puede facilitar la redistribución de las conexiones de E/S del chip al paquete. El RDL conecta las almohadillas de unión del chip a los conductores o bolas del paquete, lo que permite un montaje más fácil y un mejor rendimiento del IC.

Esto es naturalmente conveniente para el proceso de cable de unión, pero resulta algo complicado para los chips flip. Por lo tanto, el RDL se convirtió en la clave en este momento. Deposita una capa metálica y la capa dieléctrica correspondiente en la superficie del chip, formando un cable metálico y rediseñando los puertos IO a una nueva zona más espaciosa, formando una disposición de matriz superficial.

Señales de ruta y alimentación eléctrica

Además, el RDL también proporciona un medio para enrutar señales y energía dentro del IC. El uso de RDL se ha vuelto cada vez más importante a medida que los IC se han vuelto más complejos y requieren más conexiones de E/S. Se utilizan en una amplia gama de aplicaciones, como microprocesadores, chips de memoria y sensores.

Ventajas de la capa de redistribución

La tecnología RDL ofrece varias ventajas a los diseñadores que buscan crear dispositivos electrónicos de alto rendimiento, compactos y rentables. Algunas de las ventajas de utilizar la tecnología RDL en los paquetes de circuitos integrados son:

Huella reducida

La tecnología RDL permite integrar múltiples chips en un solo paquete, lo que reduce el tamaño total del dispositivo. Esto permite a los diseñadores crear dispositivos electrónicos más pequeños y compactos, lo cual es esencial para aplicaciones como teléfonos inteligentes, dispositivos portátiles y dispositivos IoT.

Rendimiento eléctrico mejorado

La tecnología RDL permite al diseñador colocar el chip de forma compacta y eficiente, lo que reduce la longitud de las interconexiones. Esto, a su vez, reduce el retraso de la señal y mejora el rendimiento eléctrico del dispositivo. La tecnología RDL también reduce la capacitancia y la inductancia parásitas, lo que mejora la integridad de la señal del dispositivo.

Reducción de costes

La tecnología RDL elimina la necesidad de realizar uniones por hilo y uniones flip-chip, que son procesos costosos y que requieren mucho tiempo. La tecnología RDL también reduce el número de componentes necesarios para el dispositivo, lo que reduce aún más su coste. La tecnología RDL es una solución rentable para crear circuitos integrados de alto rendimiento que requieren un factor de forma pequeño.

Tipos de tecnología de capa de redistribución

Existen dos tipos de tecnología de capa de redistribución (RDL): fan-in y fan-out. La tecnología RDL fan-in se utiliza para encapsular un solo chip, mientras que la tecnología RDL fan-out se utiliza para encapsular múltiples chips.

Tecnología Fan-in RDL

La tecnología RDL fan-in se utiliza para encapsular un solo chip. La tecnología RDL fan-in también se conoce como encapsulado a nivel de oblea (WLP), que es un proceso de creación de un encapsulado directamente sobre la oblea. La tecnología RDL fan-in es una solución rentable para crear encapsulados pequeños y delgados.

La tecnología RDL fan-in es adecuada para aplicaciones como sensores, dispositivos MEMS, dispositivos RF, microprocesadores y dispositivos de memoria.

Tecnología RDL de distribución en abanico

La tecnología RDL fan-out se utiliza para empaquetar múltiples matrices. La tecnología RDL fan-out también se conoce como fan-out a nivel de oblea (WLFO), que es un proceso de creación de un paquete en una oblea reconstituida. La tecnología RDL fan-out es una solución rentable para crear paquetes de alto rendimiento con un factor de forma pequeño.

La tecnología RDL fan-out es adecuada para aplicaciones como procesadores gráficos, sistemas en chip (SoC), dispositivos de memoria, dispositivos de potencia y dispositivos LED.

Proceso de la capa de redistribución

La tecnología RDL es un proceso complejo que implica muchos pasos, como la deposición dieléctrica, la deposición metálica, el patrón y el grabado. A continuación se muestra el flujo del proceso para Fan-in RDL y Fan-out RDL.

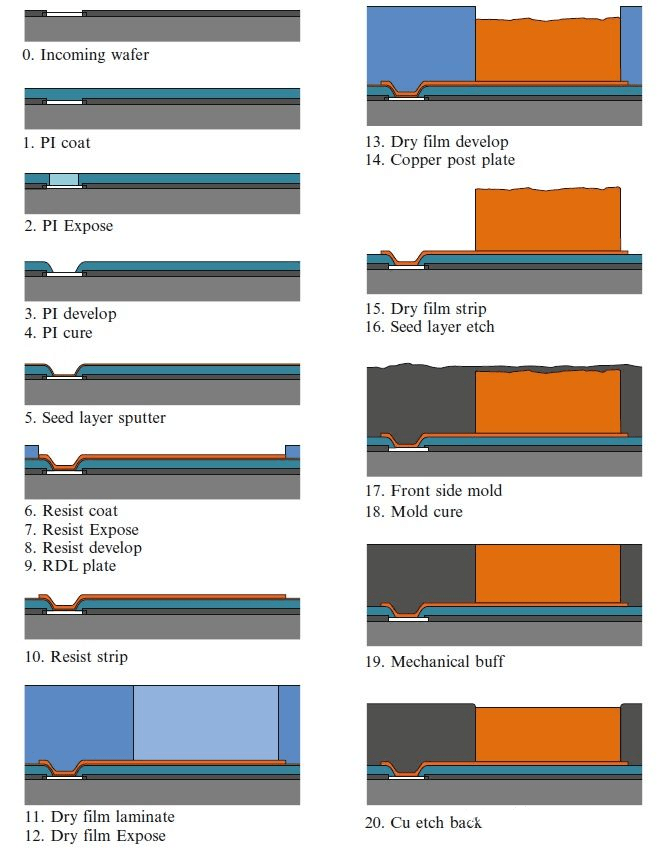

Proceso Fan-in RDL

El proceso Fan-in RDL se utiliza en la producción de soluciones de encapsulado avanzadas, como los diseños de encapsulado a escala de chip a nivel de oblea (WLCSP) y sistema en encapsulado (SiP). Permite mayores niveles de integración, factores de forma reducidos y un rendimiento mejorado para los dispositivos semiconductores. El proceso consta de varios pasos, como se indica a continuación:

El proceso comienza con una oblea entrante, que luego se recubre con PI (aislante fotorresistente) en el paso 1. A continuación, se expone el PI en el paso 2, se revela el PI en el paso 3 y se cura el PI en el paso 4.

En el paso 5, se pulveriza una capa de semillas sobre la oblea, que luego se recubre con resistente en el paso 6. A continuación, el resistente se expone en el paso 7, se revela en el paso 8 y se placa el RDL en el paso 9.

Después, el resistente se retira en el paso 10 y se lamina una película seca sobre la oblea en el paso 11. A continuación, la película seca se expone en el paso 12 y se revela en el paso 13. A continuación, se recubren los postes de cobre sobre la oblea en el paso 14 y se retira la película seca en el paso 15.

En el paso 16, se graba la capa de semilla y, en el paso 17, se crea un molde frontal. A continuación, el molde se cura en el paso 18 y la oblea se pule mecánicamente en el paso 19. Por último, en el paso 20, se graba el exceso de cobre, completando así el flujo del proceso Fan-in RDL.

Proceso RDL de distribución

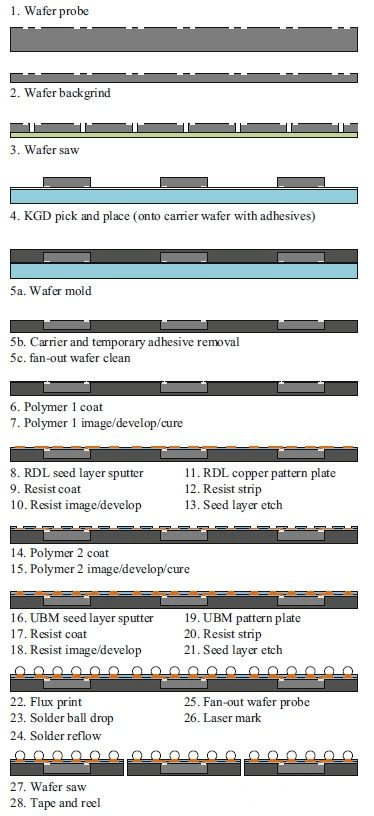

Al igual que el proceso Fan-in RDL, el proceso Fan-out RDL también es una forma de crear paquetes de chips más pequeños y de mayor rendimiento con más conexiones. Estos son los pasos de fabricación:

1. Prueba de la oblea: Se trata de la prueba inicial de la oblea para garantizar que cumple con las especificaciones requeridas antes de pasar a los siguientes pasos del proceso.

2. Esmerilado posterior de la oblea: la parte posterior de la oblea se esmerila hasta alcanzar un grosor específico para reducir el grosor del paquete.

3. Sierra de obleas: la oblea se corta en chips individuales.

4. Selección y colocación de KGD (Known Good Die, chips buenos conocidos): los chips buenos se recogen y se transfieren a una oblea portadora con adhesivo.

5a. Moldeado de la oblea: La oblea con los chips adheridos a la oblea portadora se moldea con un material dieléctrico para formar una estructura en abanico.

5b. Retirada del portador y del adhesivo temporal: La oblea portadora se retira de la oblea en abanico y también se retira cualquier adhesivo temporal utilizado durante el proceso.

5c. Limpieza de la oblea de fan-out: La oblea de fan-out se limpia para eliminar cualquier partícula o impureza restante.

6. Capa de polímero 1: Se aplica una capa de polímero a la superficie de la oblea de distribución para que actúe como capa dieléctrica.

7. Imagen/revelado/curado del polímero 1: La capa de polímero se modela mediante fotolitografía para crear la forma y el tamaño deseados de la estructura RDL.

8. Pulverización de la capa semilla RDL: Se deposita una fina capa de cobre u otro material conductor sobre la capa de polímero mediante pulverización.

9. Capa de resist: Se aplica una capa de material resistente sobre la capa de semilla.

10. Imagen/revelado de la capa resistente: La capa resistente se modela mediante fotolitografía para crear la forma y el tamaño deseados de la estructura RDL.

11. Placa de patrón de cobre RDL: Se deposita cobre sobre las áreas expuestas de la capa de semilla mediante galvanoplastia, creando el patrón RDL deseado.

12. Retirada de la capa resistente: se retira el material resistente restante, dejando solo el patrón de cobre RDL.

13. Grabado de la capa inicial: La parte innecesaria de la capa inicial se elimina mediante grabado.

14. Capa de polímero 2: se aplica otra capa de polímero sobre la estructura RDL para que actúe como capa dieléctrica.

15. Imagen/revelado/curado del polímero 2: La capa de polímero se modela mediante fotolitografía para crear la forma y el tamaño deseados de la estructura UBM.

16. Pulverización de la capa semilla UBM: Se deposita una fina capa de cobre u otro material conductor sobre la capa de polímero mediante pulverización.

17. Capa de resist: Se aplica una capa de material resistente sobre la capa semilla.

18. Imagen/revelado de la capa resistente: La capa resistente se modela mediante fotolitografía para crear la forma y el tamaño deseados de la estructura UBM.

19. Placa con patrón UBM: Se deposita cobre sobre las áreas expuestas de la capa inicial mediante galvanoplastia, creando el patrón UBM deseado.

20. Retirada de la capa resistente: se retira el material resistente restante, dejando solo el patrón UBM de cobre.

21. Grabado de la capa inicial: La parte innecesaria de la capa inicial se elimina mediante grabado.

22. Impresión de fundente: se aplica un material fundente a las almohadillas UBM.

23. Colocación de bolas de soldadura: Se colocan bolas de soldadura sobre las almohadillas UBM.

24. Reflujo de soldadura: Las bolas de soldadura se calientan para fundirse y formar conexiones entre las almohadillas UBM y los conductores externos o protuberancias.

25. Prueba de la oblea fan-out: Se prueba el IC empaquetado para garantizar que cumple con las especificaciones requeridas.

26. Marca láser: se graba un identificador único o un código de barras en la superficie del IC mediante un láser.

27. Sierra de obleas: La oblea fan-out se corta en paquetes individuales.

28. Cinta y carrete: Los circuitos integrados empaquetados individualmente se montan en un carrete para facilitar su manipulación y envío.

Aplicar RDL al embalaje avanzado

En los encapsulados avanzados, como los encapsulados a nivel de oblea fan-in (FIWLP) y los encapsulados a nivel de oblea fan-out (FOWLP), la RDL es la tecnología más importante. El auge de esta tecnología ha permitido a las plantas de encapsulado competir con las fundiciones de obleas en la tecnología de encapsulado fan-out. A través de la RDL, el IOPad se puede convertir en diferentes tipos de encapsulados a nivel de oblea en FIWLP o FOWLP. En FIWLP, todos los bumps se crean en el chip, y la conexión entre el chip y la almohadilla depende principalmente de la línea metálica de RDL. Después del empaquetado, el IC tiene casi el mismo tamaño que el área del chip. En FOWLP, los bumps pueden crearse fuera del chip, y el IC después del empaquetado es más grande que el área del chip (1,2 veces).

En particular, en el encapsulado avanzado 2.5D, además del TSV en el sustrato de silicio, el RDL también es indispensable. Tomando como ejemplo el InFO de TSMC, un representante del encapsulado avanzado 2.5D, el InFO utiliza uno o más chips desnudos en el soporte, que luego se incrustan en la oblea reconstituida del compuesto de moldeo. A continuación, se fabrican las interconexiones RDL y las capas dieléctricas en la oblea, lo que constituye un flujo de proceso «chip first». El InFO de matriz única proporciona un alto número de protuberancias, y las líneas RDL se extienden desde el área del chip hacia afuera, formando una topología «fan-out».

¿Qué tecnología de capa de redistribución debo utilizar?

Como hemos mencionado anteriormente, existen dos tecnologías RDL: Fan-in RDL y Fan-out RDL. Entonces, ¿cómo elegir la más adecuada para crear dispositivos electrónicos de alto rendimiento, compactos y rentables? Depende de varios factores, como el tipo de aplicación, el número de chips y los requisitos de rendimiento.

Aplicación

La tecnología RDL fan-in es adecuada para aplicaciones tales como sensores, dispositivos MEMS y dispositivos RF. La tecnología RDL fan-out es adecuada para aplicaciones tales como procesadores gráficos, sistemas en chip (SoC) y dispositivos de memoria.

Número de matrices

La tecnología RDL fan-in es adecuada para el encapsulado de un solo chip, mientras que la tecnología RDL fan-out es adecuada para el encapsulado de múltiples chips.

Requisitos de rendimiento

La tecnología RDL fan-in es adecuada para crear paquetes pequeños y delgados, mientras que la tecnología RDL fan-out es adecuada para crear paquetes de alto rendimiento con un factor de forma pequeño.

Comparación de RDL con otras tecnologías de encapsulado de circuitos integrados

Debido a los diferentes procesos, existen varias tecnologías de encapsulado disponibles para los circuitos integrados. En la siguiente tabla se ofrece más información sobre sus diferencias:

| IC Packaging | Description | Advantages | Disadvantages | Applications |

|---|---|---|---|---|

| Wire Bonding | Connecting the IC to the PCB using wires | Low cost, flexible, proven technology | Limited performance, not suitable for high-frequency and high-power applications | Consumer electronics, automotive, medical devices |

| Flip-Chip Bonding | Chips are bonded face-down to the substrate, Connecting the IC to the PCB using solder bumps | High performance, high-density, low inductance | Expensive, requires precise alignment and underfilling | High-speed data communication, high-power applications, microprocessors |

| Through-Silicon Via (TSV) | Creating vertical interconnects through the silicon substrate | Shorter interconnect lengths, higher performance, smaller form factor | Complex and expensive manufacturing process, thermal and mechanical stress issues | Memory devices, image sensors, 3D ICs |

| Chip-scale package (CSP) | Replacing the lead frame with a substrate | Small form factor, high density, low cost | Limited I/O, susceptibility to mechanical and thermal stress | Mobile devices, wearable technology |

| Integrated Fan-out (InFO) | Integrated package of multiple chips and the soldering point of the pin is outside of the chip | High density, small form factor, low power consumption | Complex manufacturing process, high cost | Mobile devices, IoT, wearable technology |

| High Bandwidth Memory (HBM) | 3D stacking technology | High bandwidth, low power consumption | Expensive, limited scalability | High-performance computing, graphics processing |

| Chip on Wafer on Substrate (CoWoS) | Integrate chip and silicon wafer (substrate) together | High bandwidth, low power consumption, heterogeneous integration | Complex manufacturing process, high cost | High-performance computing, graphics processing |

| Redistribution Layer (RDL) | Creating a patterned metal layer on top of the dielectric layer | High density, fine pitch, low profile | Limited power handling capability, susceptibility to mechanical and thermal stress | Mobile devices, consumer electronics |

| Bump Technology | Depositing small metal bumps on the chip | Low cost, simple manufacturing process, flexible design | Limited performance, not suitable for high-speed and high-power applications | Consumer electronics, automotive, medical devices |

Empresas que ofrecen soluciones tecnológicas de capa de redistribución

Hay varias empresas que ofrecen soluciones tecnológicas de capa de redistribución (RDL), tales como:

Grupo ASE

ASE Group es un proveedor global de servicios de fabricación de semiconductores. ASE Group ofrece una amplia gama de soluciones tecnológicas RDL para diversas aplicaciones, como memorias, microprocesadores y procesadores gráficos.

Amkor Technology

Amkor Technology es un proveedor global de servicios de encapsulado y pruebas de semiconductores. Amkor Technology ofrece una amplia gama de soluciones tecnológicas RDL para diversas aplicaciones, como sensores, dispositivos MEMS y dispositivos de potencia.

Compañía de Fabricación de Semiconductores de Taiwán

TSMC es una fundición de semiconductores global que ofrece una amplia gama de soluciones tecnológicas RDL para diversas aplicaciones, como sistemas en chip (SoC), dispositivos de memoria y dispositivos de potencia.

Conclusión

La tecnología de capa de redistribución (RDL) es una solución de encapsulado revolucionaria que ha transformado la forma en que encapsulamos los circuitos integrados (IC). Permite realizar más conexiones en un solo chip, lo que reduce el tamaño total del dispositivo. Por lo tanto, se utiliza en diversas aplicaciones, como teléfonos inteligentes, dispositivos portátiles y dispositivos IoT. El futuro de la tecnología RDL en el encapsulado de circuitos integrados es prometedor y se espera que tenga un impacto significativo en la industria electrónica en los próximos años.