MSP430F169 Übersicht

Der Mikrocontroller MSP430F169 gehört zur MSP430-Familie von Texas Instruments. Er umfasst mehrere Geräte mit unterschiedlichen Peripheriegeräten, die für verschiedene Anwendungen entwickelt wurden. Die Architektur dieser Mikrocontroller wurde in Verbindung mit fünf Energiesparmodi optimiert, um die Batterielebensdauer für tragbare Messanwendungen zu verlängern. Darüber hinaus ermöglicht der digital gesteuerte Oszillator (DCO) schnelle Aufwachzeiten von weniger als 6 µs aus den Energiesparmodi in den aktiven Modus.

Diese Mikrocontroller finden typische Anwendungen in Sensorsystemen, industriellen Steuerungsanwendungen, Handmessgeräten und anderen ähnlichen Bereichen.

Funktionen

- Geringer Stromverbrauch;

- Fünf Energiesparmodi;

- Dreikanaliger interner DMA;

- Serielle Onboard-Programmierung;

- Programmierbarer Code-Schutz durch Sicherheits-Fuse;

- Mit Brownout-Detektor und Bootstrap-Loader;

- Versorgungsspannungsüberwachung mit programmierbarer Pegelerkennung.

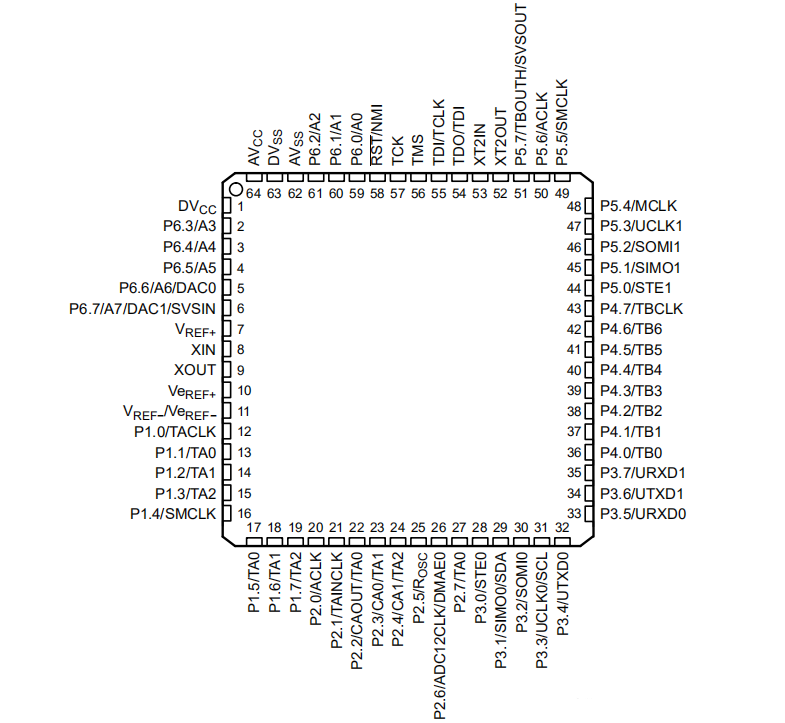

Pinbelegungskonfiguration

Der MSP430F169 ist sowohl in einer 64-Pin- als auch in einer 100-Pin-Version mit jeweils unterschiedlichen Pin-Konfigurationen erhältlich.

Bei der 64-Pin-Version gehören zu den wichtigsten Pins:

| Pin Types | Pin Name | Description |

|---|---|---|

| Power Supply Pins | VCC | Positive supply voltage input |

| GND | Ground | |

| RST/NMI | Reset input and non-maskable interrupt | |

| TEST | Test mode input/output | |

| AVSS/AVCC | Ground and voltage reference for ADC | |

| DVSS/DVCC | Ground and voltage reference for digital circuitry | |

| Input/Output Pins | P1.x-P8.x | General-purpose I/O pins |

| Communication Pins | UCA0CLK | USART module A0 clock input/output |

| UCA0STE | USART module A0 STE input/output | |

| UCA0TXD | USART module A0 transmit data output | |

| UCA0RXD | USART module A0 receive data input | |

| UCB0CLK | SPI module B0 clock input/output | |

| UCB0STE | SPI module B0 STE input/output | |

| UCB0SIMO | SPI module B0 transmit data output | |

| UCB0SOMI | SPI module B0 receive data input | |

| UCB0SDA | I2C module B0 data input/output | |

| UCB0SCL | I2C module B0 clock input/output | |

| Timers and Counters | TA0CCR0-TA0CCR6 | Timer A0 capture/compare register 0-6 |

| Timer A0 control register | ||

| TB0CCR0-TB0CCR2 | Timer B0 capture/compare register 0-2 | |

| Timer B0 control register | ||

| Analog Pins | ADC12CLK | ADC12 clock input |

| ADC12MEM0-ADC12MEM15 | ADC12 memory register 0-15 | |

| AVREF+ | Positive reference voltage input for ADC | |

| AVREF- | Negative reference voltage input for ADC | |

| JTAG Pins | TCLK | Test clock input/output |

| TDI | Test data input | |

| TDO | Test data output | |

| Special Function Pins | ACLK | 32.768 kHz crystal oscillator input |

| SMCLK | System master clock output | |

| RTCCLK | Real-time clock input/output |

Spezifikation

| Specification | Value |

|---|---|

| CPU | 16-bit RISC |

| Frequency | 8 MHz |

| Flash memory | 16 KB |

| RAM | 2 KB |

| Standby power | 1.1 µA |

| Active power | 330 µA at 1 MHz, 2.2 V |

| Wake-up time | in less than 6 µs |

| Instruction cycle time | 125 ns |

| Supply voltage | 1.8 V to 3.6 V |

| A/D converter | 12-bit |

| Timer/Counter | 2 * 16-bit |

| Operating Temp | -40 to 85 ℃ |

| DMA | 3 |

| I2C | 1 |

| SPI | 2 |

| Peripherals | timers, serial ports, I2C |

| Package | 64-pin QFP or 64-pin QFN |

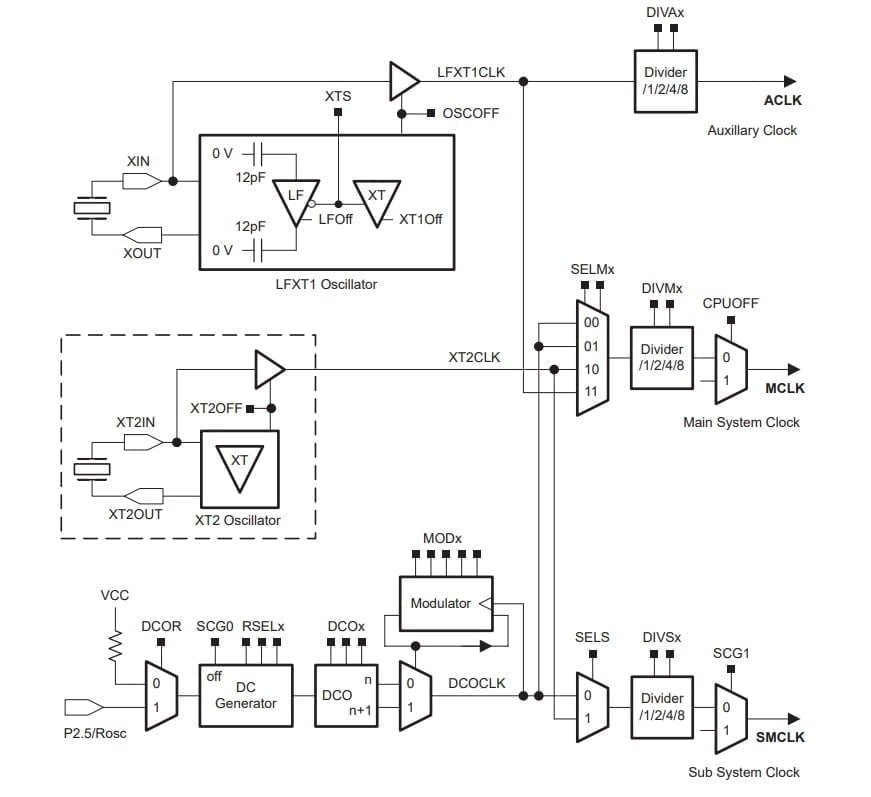

Taktsystem des MSP430F169

Das Taktsystem ist für den Einchip-Mikrocomputer sehr wichtig. Der Grund, warum der Einchip-Mikrocomputer MSP430F169 einen so geringen Stromverbrauch hat, liegt in seinem leistungsstarken Taktsystem!

Drei Taktsignalquellen

1. Niederfrequenz LFXT1CLK (32,768 kHz)

Ein Standard-Quarzoszillator, Oszillator oder eine externe Taktquelle kann für die Eingabe von 4 MHz bis 32 MHz verwendet werden. XT1CLK kann als Referenztakt für das interne FLL-Modul verwendet werden.

Der Niederfrequenz-Quarzoszillator (32,768 kHz) ist über die Pins XIN und XOUT direkt mit dem Einchip-Mikrocomputer verbunden, sodass keine weiteren externen Geräte erforderlich sind (im Inneren befindet sich eine Lastkapazität von 12 pF). Zu diesem Zeitpunkt arbeitet der LFXT1-Oszillator im Niederfrequenzmodus (XTS=0).

Wenn die MCU mit einem Hochgeschwindigkeits-Bulk-Oszillator oder Resonator verbunden ist, kann 0SCOFF=0 den LFXT1-Oszillator im Hochfrequenzmodus (XTS=1) arbeiten lassen. Zu diesem Zeitpunkt ist der Hochgeschwindigkeits-Quarzoszillator oder Resonator über die Pins XIN und XOUT angeschlossen, und es ist ein externer Kondensator erforderlich. Die Größe des Kondensators wird entsprechend den Eigenschaften des Quarzoszillators oder Resonators ausgewählt.

Wenn das LFXT1CLK-Signal nicht als SMCLK- oder MCIK-Signal verwendet wird, kann die Software OSCOFF=1 setzen, um den LFXT1 zu deaktivieren und so den Stromverbrauch des Mikrocontrollers zu reduzieren.

BCSCTL1:

XTS(BIT6)——Auswahl des LFXT1-Hoch-/Niedriggeschwindigkeitsmodus. 0: LFXT1 arbeitet im Niedriggeschwindigkeits-Quarzoszillatormodus (Standard); 1: LFXT1 arbeitet im Hochgeschwindigkeits-Quarzoszillatormodus.

2. Hochfrequenz-XT2CLK (8 MHz)

Es kann ein Standard-Quarzoszillator, Oszillator oder eine externe Taktquelle für die Eingabe von 4 MHz bis 32 MHz verwendet werden.

Der XT2-Oszillator erzeugt das Taktsignal XT2CLK und seine Betriebseigenschaften ähneln denen des LFXT1-Oszillators, wenn dieser im Hochfrequenzmodus arbeitet. Wenn XT2CLK nicht als MCLK- und SMCLK-Taktsignal verwendet wird, kann der XT2-Oszillator mit dem Steuerbit XT2OFF deaktiviert werden.

BCSCTL1:

XT2OFF (BIT7) – Steuerung des XT2-Hochgeschwindigkeits-Quarzoszillators. 0: XT2-Hochgeschwindigkeits-Quarzoszillator eingeschaltet; 1: XT2-Hochgeschwindigkeits-Quarzoszillator ausgeschaltet.

3. Interner Oszillator DCOCLK (1 MHz)

Durch das FLL-Modul stabilisiert.

Wenn der Oszillator ausfällt, wird DCO automatisch als Taktquelle für MCLK ausgewählt.

Die Frequenz des DCO-Oszillators kann durch Softwareeinstellung der Bits DCOx. MODx und RSEL.x angepasst werden. Wenn das DCOCLK-Signal nicht als SMCLK- und MCLK-Taktsignal verwendet wird, kann der DC-Generator mit dem Steuerbit SCGO deaktiviert werden.

Nach dem PUC-Signal wird DCOCLK automatisch als MCLK-Taktsignal ausgewählt, und die Taktquelle von MCLK kann zusätzlich je nach Bedarf auf LFXT1 oder XT2 eingestellt werden. Die Einrichtungssequenz ist wie folgt:

- Lass OSCOFF=1;

- OFIFG=0;

- Verzögern und mindestens 50 ps warten;

- Überprüfe OFIFG erneut. Wenn OFIFG=1, wiederhole die Schritte (3) und (4), bis OFIFG=0 ist.

DCOCTL:

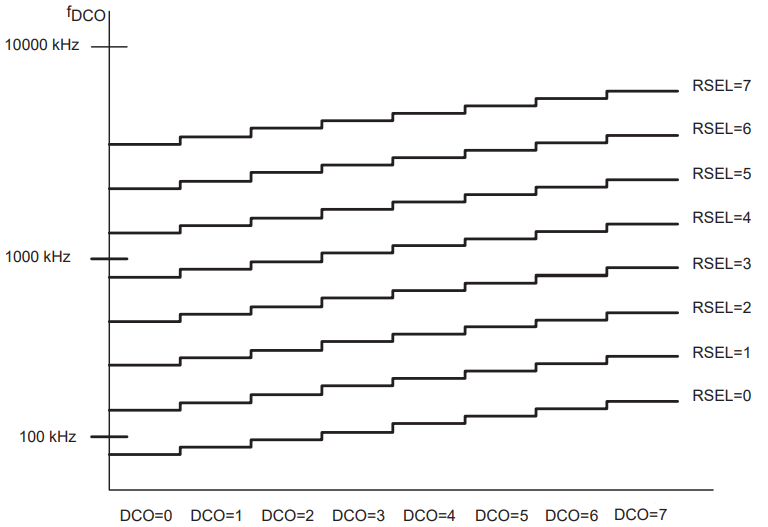

DCOx (BIT7, BIT6, BIT5)——DCO-Frequenzauswahl, 8 Frequenzen können ausgewählt werden, und die DCOCLK-Frequenz kann in Abschnitten angepasst werden. Die Frequenzauswahl basiert auf dem von RSELx ausgewählten Frequenzband. Die Beziehung zwischen DCOx, RSELx und dem internen Takt ist wie folgt:

MODx (BIT4, BIT3, BIT2, BIT1, BIT0) – DAC-Modulator-Einstellung. Der Regler schaltet zwischen den beiden von DCOx und DCOx+1 ausgewählten Frequenzen um, um die Ausgangsfrequenz des DCO fein abzustimmen. Wenn die DCOx-Konstante 7 ist, bedeutet dies, dass die höchste Frequenz ausgewählt wurde. In diesem Fall ist MODx ungültig und kann nicht zur Frequenzeinstellung verwendet werden.

BCSCTL1:

RSELx (BIT2, BIT1, BIT0) – Auswahl des Frequenzbandes des DCO-Oszillators. Diese 3 Bits steuern einen internen Widerstand, um die Nennfrequenz zu bestimmen. 0: Auswahl der niedrigsten Nennfrequenz… 7: Auswahl der höchsten Nennfrequenz.

BCSCTL2:

DCOR(BIT0)——Auswahl des DCO-Oszillatorwiderstands. 0: interner Widerstand; 1: externer Widerstand.

Drei Taktquellen

1. ACLK-Hilfstaktgeber

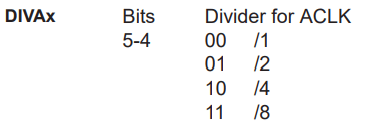

ACLK wird nach der Teilung von LFXT1CLK durch 1, 2, 4 und 8 erhalten. Es kann als Taktsignal für jedes Peripheriemodul verwendet werden und wird in der Regel für Peripheriegeräte mit niedriger Geschwindigkeit verwendet.

BCSCTL1:

DIVAx (BIT5, BIT4) – Auswahl der ACLK-Frequenzteilung, wobei die Auswahl der Frequenzteilung wie folgt erfolgt:

Makrodefinition: DIVA_0 (1 Frequenzteilung/keine Frequenzteilung), DIVA_1 (2 Frequenzteilungen), DIVA_2 (4 Frequenzteilungen), DIVA_3 (8 Frequenzteilungen)

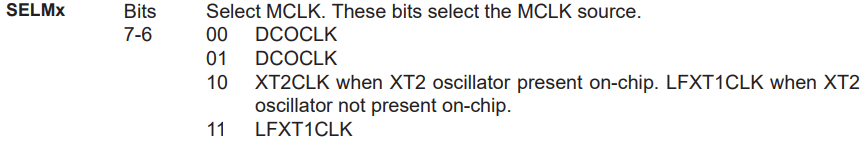

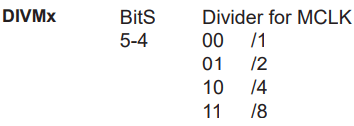

2. MCLK-System-Haupttaktgeber

MCLK kann nach Frequenzteilung durch 1, 2, 4 und 8 aus LFXT1CLK, XT2CLK und DCOCLK gewonnen werden. Es wird häufig für den CPU-Betrieb, die Programmausführung und andere Module verwendet, die Hochgeschwindigkeitstaktgeber verwenden.

BCSCTL2:

SELMx (BIT7, BIT6) – Wählen Sie die MCLK-Taktquelle aus. Die Taktwahlbeziehung ist wie folgt:

Makrodefinition: SELM_0 (DCOCLK-Standard), SELM_1 (DCOCLK), SELM_2 (XT2CLK), SELM_3 (LFXT1CLK)

DIVMx (BIT5, BIT4) – Auswahl der MCLK-Frequenzteilung, die Auswahl der Frequenzteilung verhält sich wie folgt:

Makrodefinition: DIVM_0 (1 Frequenzteilung/keine Frequenzteilung), DIVM_1 (2 Frequenzteilungen), DIVM_2 (4 Frequenzteilungen), DIVM_3 (8 Frequenzteilungen)

3. SMCLK-Subsystem-Taktgeber

SMCLK kann durch Frequenzteilung von XT2CLK und DCOCLK durch 1, 2, 4 und 8 erhalten werden und wird häufig in Hochgeschwindigkeits-Peripheriemodulen verwendet.

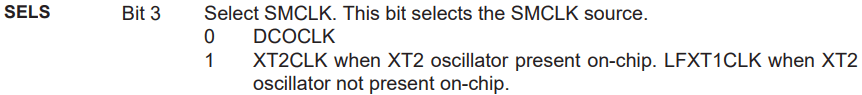

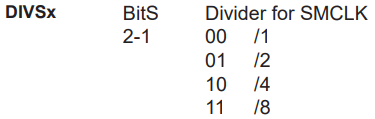

BCSCTL2:

SELSx (BIT3) – Wählen Sie die MCLK-Taktquelle aus. Die Taktwahlbeziehung ist wie folgt:

DIVSx (BIT2, BIT1) – Auswahl der SMCLK-Frequenzteilung, die Beziehung zwischen der Auswahl der Frequenzteilung ist wie folgt:

Makrodefinition: DIVS_0 (1 Frequenzteilung/keine Frequenzteilung), DIVS_1 (2 Frequenzteilung), DIVS_2 (4 Frequenzteilung), DIVS_3 (8 Frequenzteilung)