Présentation de la puce STM32F030

La puce STM32F030 est un microcontrôleur ARM Cortex-M0 32 bits à faible coût de STMicroelectronics. Elle dispose d'une mémoire Flash pouvant atteindre 32 Ko et d'une mémoire SRAM de 4 Ko, et peut fonctionner à une fréquence maximale de 48 MHz. Elle comprend divers périphériques, tels que des comparateurs analogiques, des minuteries et des interfaces I2C et SPI. La puce STM32F030 prend également en charge les applications de contrôle moteur et dispose d'une large gamme de périphériques analogiques et numériques intégrés. Sa petite taille et sa faible consommation d'énergie la rendent idéale pour une utilisation dans diverses applications, de l'électronique grand public aux systèmes médicaux et industriels. Le prix et les performances de la puce font du STM32F030 un excellent choix pour les développeurs soucieux des coûts. Grâce à la prise en charge d'une variété d'outils de développement, notamment STM32Cube et l'outil de configuration graphique STM32CubeMX, il est facile de se lancer avec le STM32F030 et de développer des applications innovantes.

Paramètres

– CPU : cœur ARM Cortex-M0 avec architecture

RISC 32 bits – Fréquence de fonctionnement : jusqu'à 48 MHz

– Mémoire programme : jusqu'à 32 Ko Flash

– RAM : jusqu'à 4 Ko

– Source d'horloge : interne 8 MHz ou externe 32

kHz – Sortie d'horloge : 2 x 32 kHz

– E/S numériques : jusqu'à 36 broches

E/S – Entrées analogiques : jusqu'à 8 canaux

ADC 12 bits – Minuteries : jusqu'à 3 minuteries 16

bits – Interfaces de communication : jusqu'à 2 x I2C, 2 x USART, SPI, CAN

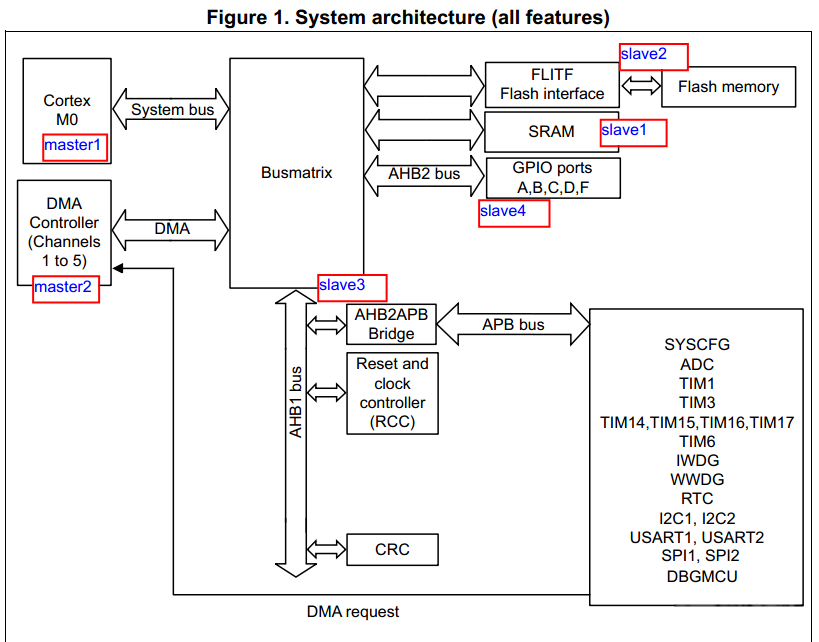

Architecture du système

Le cadre système interne du STM32F030 peut être simplement divisé en 2 systèmes maîtres et 4 systèmes esclaves. Les concepts de maître et d'esclave sont ici relatifs à Busmatrix :

- Maîtres

- Cœur Cortex-M0 Bus AHB

- GP-DMA

- Esclaves

- SRAM interne

- Flash interne

- AHB2APB

- AHB vers ports GPIO

La relation entre 2 maîtres et 4 esclaves est illustrée plus en détail dans la figure suivante et indiquée par :

Pour le pont AHB2APB, si vous souhaitez utiliser les périphériques connectés au bus APB, vous devez d'abord appeler un registre tel que RCC_AHBENR pour activer l'horloge périphérique, et le périphérique est le pilote périphérique. Ces détails sont généralement gérés dans l'API du pilote ST.

Présentation de la mémoire

Dans le programme STM32F030, les données, les registres et les ports E/S sont tous mappés à l'espace d'adressage de 4 Go (machine 32 bits). La carte mémoire du STM32F030 est détaillée dans la fiche technique.

SRAM

La mémoire SRAM du STM32F030 a une taille de 8 Ko et est accessible par octets, mots et demi-mots. Cette section est utilisée pour stocker le code compilé et lié, les données et la pile de programme pendant l'exécution. Les données sont constamment lues ou écrites dans cette mémoire SRAM pendant l'exécution du programme.

Flash

La mémoire flash interne du STM32F030 est généralement suffisante pour une utilisation, car elle est conçue à cet effet. Elle dispose d'un espace flash utilisateur de 64 Ko. La mémoire flash intégrée à la puce est appelée mémoire flash interne ou ROM (la ROM et la mémoire flash diffèrent en ce que la ROM ne peut pas être effacée par l'utilisateur et est fixée lors de la production de la puce, tandis que la mémoire flash peut être effacée et réécrite à tout moment).

La mémoire flash interne du STM32F030 est divisée en deux types :

- 64 Ko d'espace flash utilisateur : utilisé pour télécharger le code .bin généré par la compilation et la liaison de l'utilisateur.

- Flash d'information : comprend les octets d'option et la mémoire système.

Les octets d'option peuvent être utilisés pour configurer certaines fonctions du circuit intégré. La mémoire

système est la mémoire du circuit intégré, qui contient un segment de code fixé lors de la production du circuit intégré, qui n'est pas open source et dont le fonctionnement ne peut être que deviné. La mémoire système a pour but d'agir comme un chargeur d'amorçage intégré. En général, elle n'est pas utilisée pour le débogage. L'utilisation typique consiste à connecter un débogueur via une interface SWD au circuit intégré et à télécharger et déboguer facilement le code. Cependant, pour les produits, l'interface SWD peut ne pas être exposée. Dans ce cas, le code .bin du produit peut être téléchargé et exécuté via le chargeur d'amorçage de la mémoire système interne du circuit intégré via une interface série, ce qui correspond au processus typique pour les mises à jour du micrologiciel. STM fournira l'interface et une démonstration d'utilisation du chargeur d'amorçage de la mémoire système, et il existe de nombreux documents connexes expliquant comment l'utiliser.

Boot Configuration

Le débogage via SWD est appelé « programmation système », tandis que le chargement et le démarrage de programmes à l'aide d'un bootloader sont considérés comme de la « programmation d'application ». STM propose trois modes de démarrage configurables pour différents scénarios d'application.

Configuration du mode de démarrage :

Tout d'abord, il existe une broche de démarrage qui se connecte aux niveaux haut ou bas. Lorsque la puce démarre, elle vérifie le niveau de la broche de démarrage et passe au mode de démarrage correspondant. De plus, nBOOT1 peut être configuré dans l'octet d'option pour sélectionner le mode de démarrage correspondant.

Classification des modes de démarrage :

Il existe trois types : le démarrage flash utilisateur, qui est le plus courant ; après compilation et liaison, téléchargez le code, réinitialisez et exécutez votre propre code flash. Le démarrage de la mémoire système, qui utilise le chargeur d'amorçage interne du circuit intégré pour démarrer. Le démarrage SRAM.

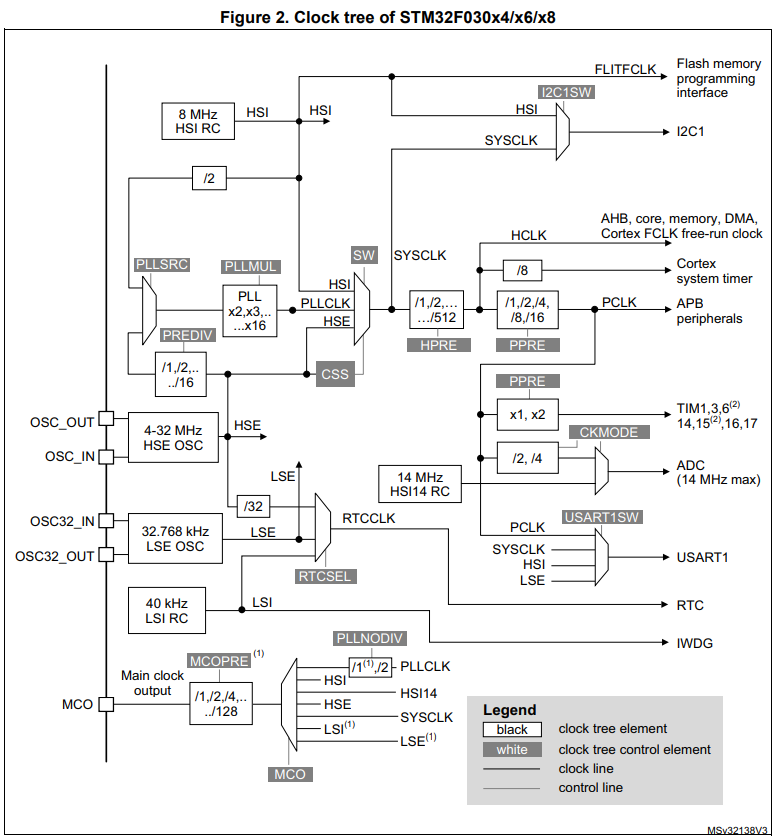

Cadre d'horloge

Le cadre d'horloge du STM32F030 est le suivant, et voici quelques définitions :

- HSI : appelé horloge interne haute vitesse, il est composé d'un oscillateur RC.

- HSE : appelée horloge externe haute vitesse, peut être connectée à un résonateur externe à quartz/céramique ou à une source d'horloge externe.

- LSI : appelée horloge interne basse vitesse, composée d'un oscillateur RC, elle a une fréquence basse, et le STM32F030 est de 40 kHz.

- LSE : appelée horloge externe basse vitesse, généralement connectée à un cristal de quartz avec une fréquence externe de 32,768 kHz.

- PLL : correspond à la sortie multiplicatrice de la boucle à verrouillage de phase.

- HSI14 RC : source d'horloge pouvant être utilisée uniquement pour l'ADC.

Les périphériques qui ne sont pas spécifiquement mentionnés utilisent généralement PCLK. Voici une brève liste des situations qui doivent être activées avec AHB/APB selon le code spécifique :

- Utilisation de l'AHB comme source d'horloge : GPIOA-F, TS, CRC, FLITF, SRAM, DMA1.

- Utilisation de l'APB1 comme source d'horloge : TIM2, TIM3, TIM6, TIM14, WWDG, SPI2, USART2, I2C1, I2C2, PWR, DAC, CEC.

- Utilisation de l'APB2 comme source d'horloge : SYSCFG, ADC1, TIM1, SPI1, USART1, TIM15, TIM16, TIM17, DBGMCU.

Fonction de réinitialisation

La réinitialisation est une étape cruciale du processus de démarrage du système MCU. Lorsque le circuit intégré commence à exécuter le programme, il démarre à partir de la réinitialisation, qui est la première étape après la mise sous tension du système.

Mécanisme de réinitialisation du Cortex-M0

Dans le fichier de démarrage du Cortex-M0, vous verrez toujours le reset_handler, qui se trouve en première position de la table vectorielle. L'adresse du Cortex-M0 est 0x0000 0004, et la valeur PC lorsque le Cortex-M0 commence à fonctionner est cette adresse. Dans le reset_handler, la fonction SystemInit implémentée par l'utilisateur est généralement appelée. Elle configure l'horloge des différents composants nécessaires au bon fonctionnement du système, ce qui facilite le fonctionnement normal du système par la suite. Ensuite, l'entrée __main de la bibliothèque est appelée. Elle doit effectuer un traitement initial de la bibliothèque d'exécution C et configurer la pile.

Types de réinitialisation

Il existe trois principaux types de réinitialisation pour le STM32F030 : la réinitialisation de l'alimentation, la réinitialisation du système et la réinitialisation du domaine RTC.

La réinitialisation de l'alimentation est liée à l'alimentation électrique du circuit intégré. Cette réinitialisation est déclenchée par la mise sous tension et la sortie du mode veille, et l'initialisation du système commence après la réinitialisation.

La réinitialisation du système est déclenchée par le système. Autrement dit, l'alimentation électrique est normale, mais si le bouton de réinitialisation est enfoncé, si le registre correspondant est réinitialisé par le logiciel ou si le Watchdog est déclenché, cette réinitialisation se produit. Lorsque cette réinitialisation se produit, la seule différence par rapport à la réinitialisation de l'alimentation est que le bit correspondant dans le registre RCC_CSR utilisé pour indiquer la source de réinitialisation ne sera pas réinitialisé, tandis que tous les autres registres seront réinitialisés à l'état juste après la mise sous tension.

Le déclenchement de la réinitialisation du domaine RTC est également un déclenchement logiciel. Il est déclenché en écrivant dans le bit correspondant du registre RCC_BDCR. Cependant, ce type de réinitialisation n'affecte que le cristal RTC et LSE, etc.

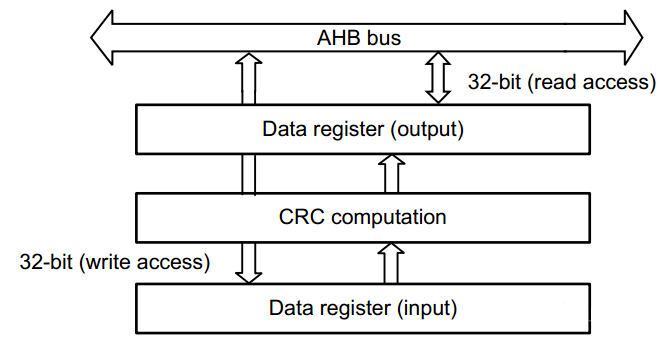

Cycle d'amélioration continue

Le CRC, ou contrôle de redondance cyclique, est un algorithme de vérification qui contrôle l'intégrité des données transmises/stockées. Comme il peut être utilisé dans de nombreux cas, le STM32F030 implémente cet algorithme avec une unité de calcul CRC matérielle dans le circuit intégré. Lorsqu'une application doit utiliser le CRC, l'unité matérielle peut être contrôlée par un logiciel afin de répondre aux exigences (bien sûr, le CRC peut également être implémenté dans un logiciel, mais la vitesse n'est alors pas aussi rapide qu'avec le CRC matériel).

Le processus CRC est implémenté à l'intérieur du circuit intégré, vous devez donc seulement savoir comment l'utiliser, ce qui est très simple. Écrivez les données sources à calculer dans le registre de données (entrée), lancez le calcul de l'unité de calcul CRC, puis lisez les résultats calculés dans le registre de données (sortie).

En fait, l'entrée et la sortie du registre de données CRC du STM32F030 utilisent le même registre, car il faut d'abord entrer les données, puis obtenir la sortie avant de passer à l'entrée suivante. Ce processus montre que l'entrée et la sortie ne sont pas utilisées en même temps, vous pouvez donc utiliser directement un registre pour multiplexer les deux fonctions. Le registre peut fonctionner en 32 bits, 16 bits ou 8 bits, ce qui permet de répondre à différentes exigences.

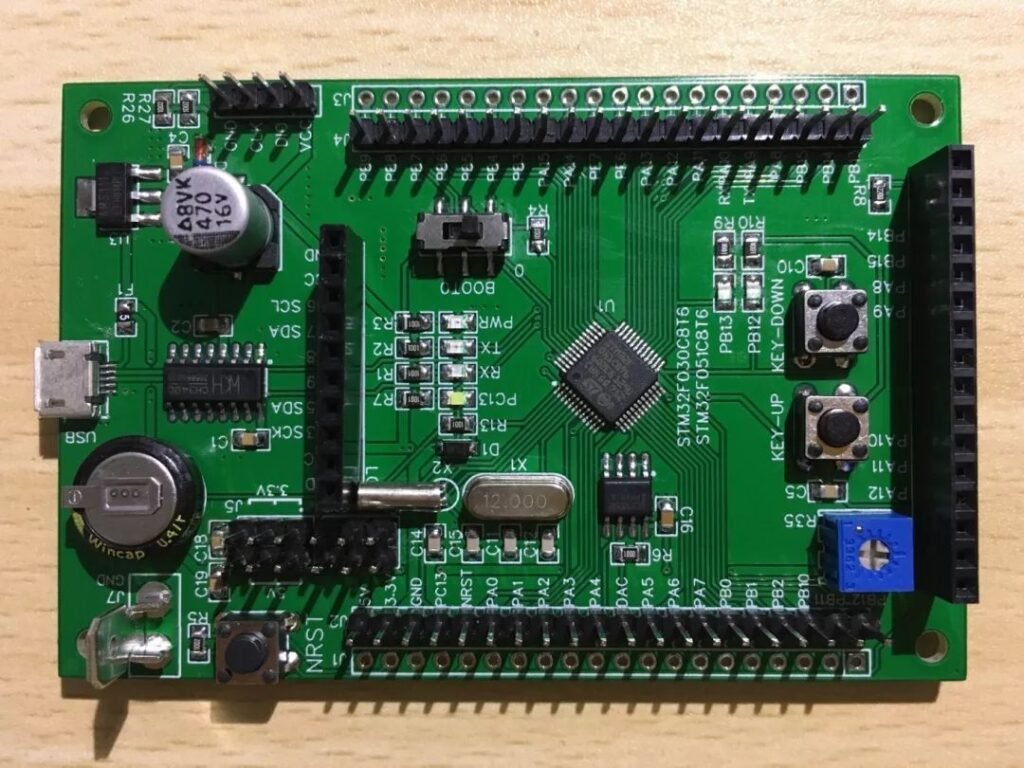

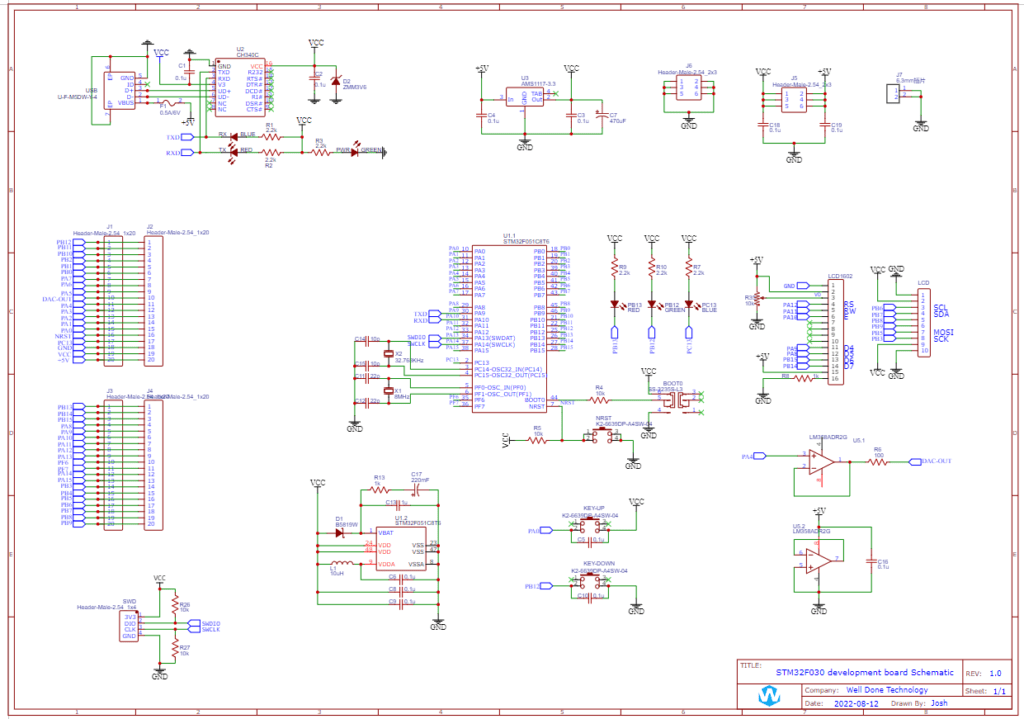

Carte de développement STM32F030 - STM32f0308 Discovery

Le développement de ce microcontrôleur STM32F030 repose sur la dernière bibliothèque HAL de STM32, le code d'initialisation généré par STM32CubeMX, et son compilateur est GCC. Vous trouverez ci-dessous son schéma, son diagramme PCB et sa carte assemblée. STM32 propose de nombreuses cartes de développement d'entrée de gamme, telles que les séries Discovery et Nucleo. La stm32f0308 discovery est l'une des cartes de la série Discovery, équipée de la puce STM32F030.

Les fonctions et caractéristiques de base des cartes de développement de la série Discovery sont similaires, mais les capacités des puces qui les accompagnent peuvent varier. Les caractéristiques de la stm32f0308 discovery sont les suivantes :

Extension pratique des ports E/S : le développement peut être effectué à l'aide d'un simple câble USB connecté à un PC. Les ports E/S de la puce STM32F030 sur la carte de développement sont étendus, ce qui facilite la connexion à différents appareils à l'aide de fils DuPont.

Interface de débogage : la carte de développement est équipée d'une interface de débogage SWD intégrée, qui est mise en œuvre à l'aide d'une autre puce Cortex-M3 de ST (actuellement, la version v9 de JLINK disponible sur le marché devrait également utiliser la puce Cortex-M3 de ST). Cette interface de débogage SWD peut être utilisée séparément grâce à la connexion d'un capuchon de cavalier, ce qui signifie que le stm32f0308-discovery peut être utilisé comme débogueur SWD autonome.

Alimentation flexible : la carte de développement elle-même est alimentée par USB, mais elle dispose d'un circuit de conversion de tension qui peut fournir des alimentations de 5 V et 3 V pour les périphériques externes (notez que le courant d'alimentation reste limité). En général, les petits modules et interfaces peuvent être alimentés directement par celle-ci.

Périphériques au niveau de la carte : comme il s'agit d'une carte de développement d'entrée de gamme et peu coûteuse, les périphériques intégrés sont très simples, composés de deux boutons et de quatre LED. Parmi les deux boutons, l'un sert à la réinitialisation et l'autre est un bouton programmable par l'utilisateur. Parmi les quatre LED, l'une est un indicateur d'alimentation, l'autre est un indicateur d'état de débogage SWD, et les deux autres peuvent être programmées pour le contrôle. Ainsi, en réalité, les périphériques intégrés pouvant être programmés pour le contrôle ne sont qu'un bouton utilisateur et deux LED utilisateur.

Performance

- Interface SWD réservée pour le débogage par ST-LINK ;

- Interface PA4 (sortie DAC) avec capacité d'entraînement de port élevée ;

- Deux boutons tactiles légers et 3 LED pour un débogage facile ;

- Interface LCD1602 et interface compatible avec les écrans LCD TFT courants ;

- Utilisation d'un supercondensateur comme alimentation de secours RTC ;

- Interface USB avec protection d'alimentation ;

- Plusieurs points de test d'alimentation pour oscilloscope ou multimètre.