No hace mucho, Intel logró desarrollar la tecnología de suministro de energía por la parte posterior en un chip de prueba a nivel de producto con el nombre en clave «Blue Sky Creek» para satisfacer las exigencias de rendimiento de la próxima era de la informática. Intel presentó los resultados de esta investigación a través de dos artículos presentados en el Simposio VLSI celebrado en Kioto, Japón, del 11 al 16 de junio de este año. Más información

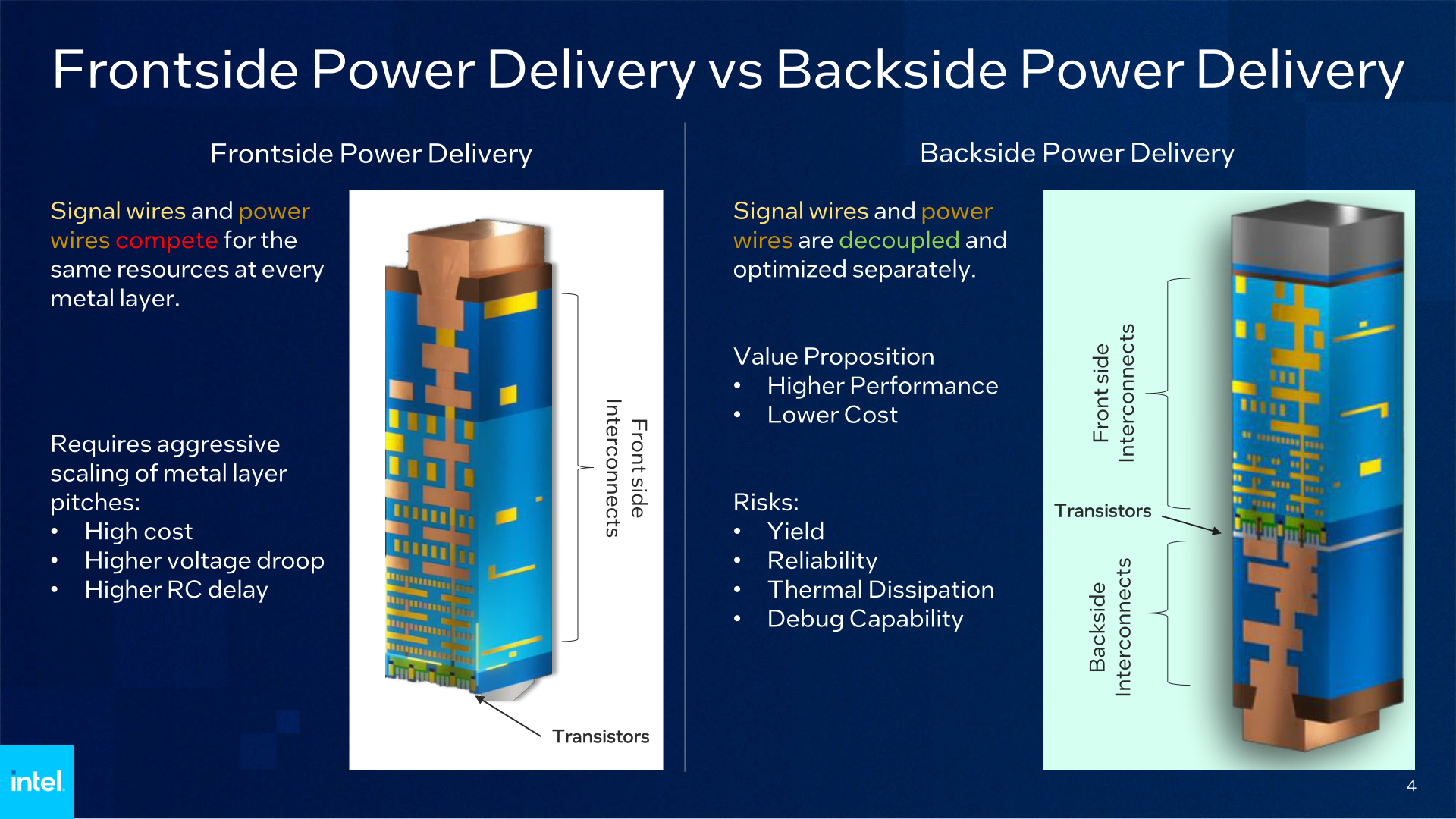

A medida que los nodos de proceso siguen avanzando, la tecnología tradicional de suministro de energía en la parte frontal se enfrenta a numerosos retos. Dado que las líneas de señal y de energía se encuentran en la parte frontal de la oblea, deben compartir o incluso competir por los recursos de cada capa metálica. Esto requiere esfuerzos para aumentar el espacio entre los pines de la capa metálica, lo que conlleva mayores costes y complejidad. Como respuesta, la industria ha comenzado a explorar la posibilidad de trasladar la distribución de energía a la parte posterior. La tecnología de suministro de energía por la parte trasera separa las líneas de señal y de alimentación, trasladando estas últimas a la parte trasera de la oblea, lo que permite una optimización individual. Esto proporciona un mayor rendimiento y menores costes, aunque también plantea retos en términos de rendimiento, fiabilidad, disipación del calor y depuración.

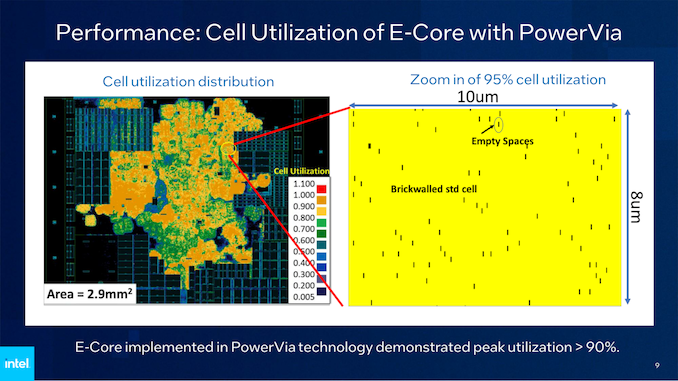

Según se informa, tanto los nodos de proceso Intel 20A como Intel 18A adoptarán la tecnología de suministro de energía trasera PowerVia junto con la tecnología de puerta integral RibbonFET. Para abordar estos retos y acelerar el desarrollo, Intel decidió desarrollar las tecnologías PowerVia y RibbonFET por separado, siendo PowerVia la pionera. A través de las pruebas, la tecnología PowerVia mejora significativamente la eficiencia de los chips, con tasas de utilización que superan el 90 % para la mayoría de las áreas de celdas estándar. El tamaño de los transistores se reduce notablemente, la densidad unitaria aumenta considerablemente y PowerVia alcanza altos índices de rendimiento y fiabilidad durante las pruebas, lo que demuestra el valor esperado de esta tecnología. Las pruebas también revelan que PowerVia reduce el voltaje de la plataforma en un 30 % y aporta una ganancia de frecuencia del 6 %.

Además, Intel ha desarrollado una tecnología de disipación del calor para evitar problemas de sobrecalentamiento. El equipo de depuración también ha ideado nuevas técnicas para abordar diversos problemas que surgen durante la depuración de esta novedosa estructura de diseño de transistores. Los chips de prueba PowerVia muestran características de disipación del calor favorables, en línea con las expectativas de lograr una mayor densidad de potencia mediante la miniaturización lógica.

Ben Sell, vicepresidente de Desarrollo Tecnológico de Intel, afirmó: «Intel está impulsando activamente el plan «Cuatro años, cinco nodos de proceso» y se ha comprometido a integrar un billón de transistores en un solo paquete para 2030. PowerVia representa un hito significativo para ambos objetivos. Al adoptar nodos de proceso producidos experimentalmente y sus chips de prueba, Intel ha reducido el riesgo de aplicar la entrega de energía por la parte posterior a nodos de proceso avanzados y está llevando la tecnología de entrega de energía por la parte posterior al mercado».

Se entiende que en un próximo tercer artículo que se presentará en el Simposio VLSI, el experto técnico de Intel, Mauro Kobrinsky, profundizará en los logros de la investigación de Intel en métodos de implementación más avanzados para PowerVia, como la transmisión simultánea de señales y el suministro de energía en las caras delantera y trasera de la oblea.