Recentemente, a Intel desenvolveu uma tecnologia de fornecimento de energia traseira em um chip de teste de nível de produto com o nome de código "Blue Sky Creek" para atender às demandas de desempenho da próxima era da computação. A Intel apresentou os resultados dessa pesquisa por meio de dois artigos apresentados no Simpósio VLSI, realizado em Kyoto, Japão, de 11 a 16 de junho deste ano. Mais informações

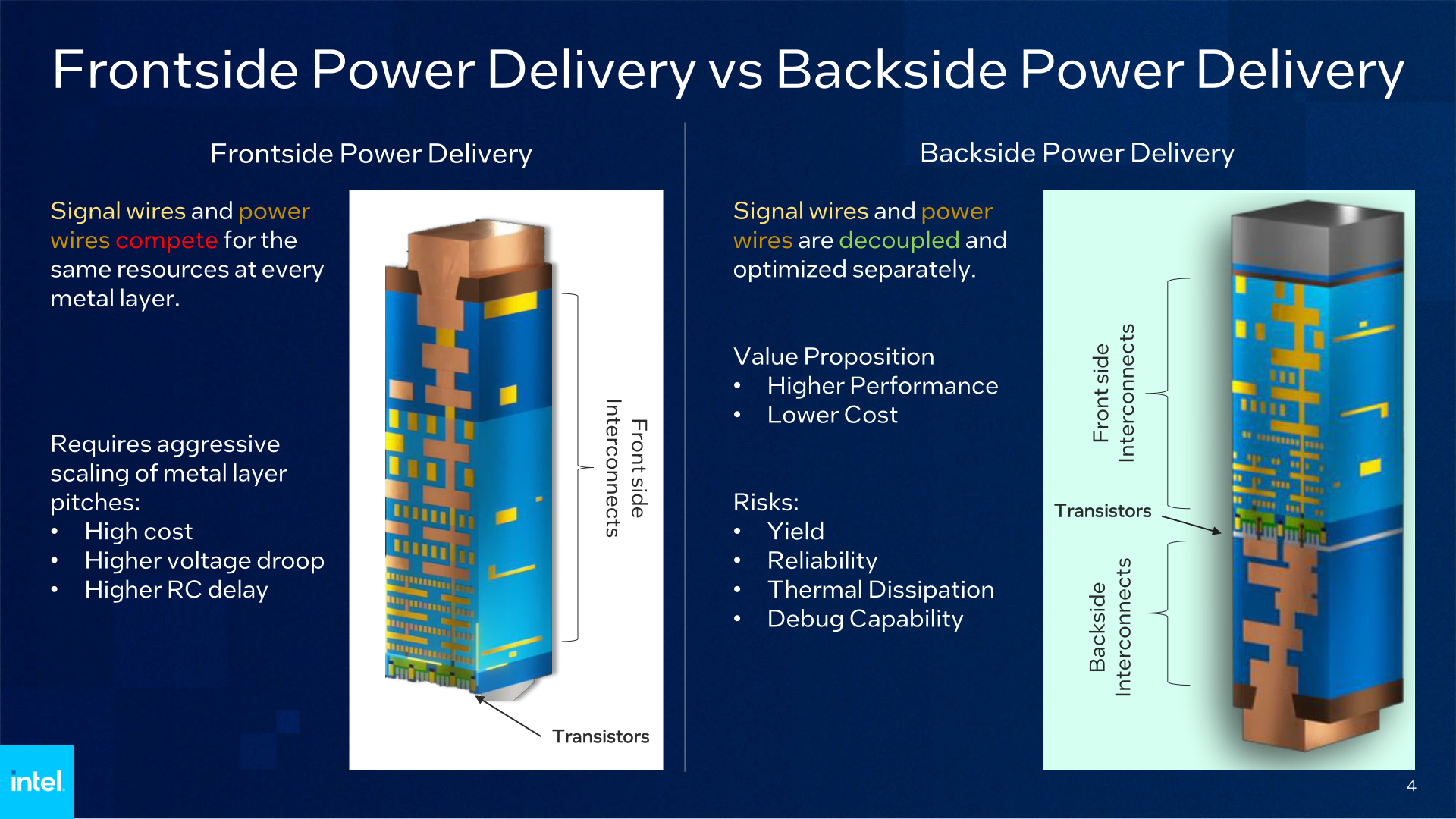

À medida que os nós do processo continuam a avançar, a tecnologia tradicional de fornecimento de energia na parte frontal enfrenta inúmeros desafios. Com as linhas de sinal e energia localizadas na parte frontal do wafer, elas precisam compartilhar ou até mesmo competir por recursos em cada camada metálica. Isso exige esforços para aumentar o espaçamento entre os pinos da camada metálica, levando a custos e complexidade mais elevados. Em resposta, a indústria começou a explorar a possibilidade de transferir a distribuição de energia para a parte traseira. A tecnologia de fornecimento de energia na parte traseira separa as linhas de sinal e energia, movendo estas últimas para a parte traseira do wafer, permitindo a otimização individual. Isso traz maior desempenho e custos mais baixos, embora também apresente desafios em termos de rendimento, confiabilidade, dissipação de calor e depuração.

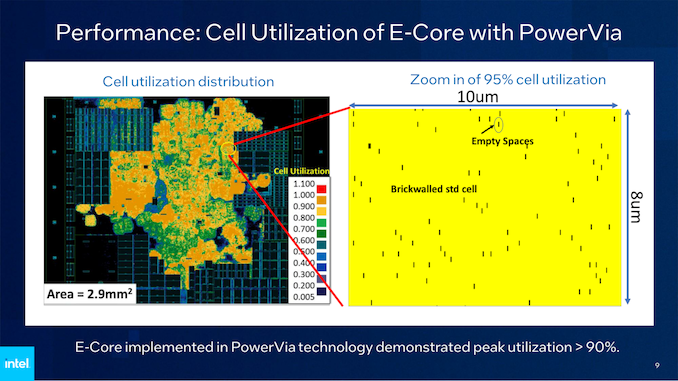

Segundo relatos, os nós de processo Intel 20A e Intel 18A adotarão a tecnologia de fornecimento de energia PowerVia, juntamente com a tecnologia de porta RibbonFET. Para enfrentar esses desafios e acelerar o desenvolvimento, a Intel optou por desenvolver as tecnologias PowerVia e RibbonFET separadamente, com a PowerVia sendo a pioneira. Através de testes, a tecnologia PowerVia melhora significativamente a eficiência do chip, com taxas de utilização superiores a 90% para a maioria das áreas de células padrão. Os tamanhos dos transistores são notavelmente reduzidos, a densidade da unidade é bastante aumentada e a PowerVia alcança altos indicadores de rendimento e confiabilidade durante os testes, demonstrando o valor esperado dessa tecnologia. Os testes também revelam que a PowerVia reduz a tensão da plataforma em 30% e traz um ganho de frequência de 6%.

Além disso, a Intel desenvolveu uma tecnologia de dissipação de calor para evitar problemas de superaquecimento. A equipe de depuração também criou novas técnicas para resolver vários problemas que surgem durante a depuração dessa nova estrutura de design de transistor. Os chips de teste PowerVia apresentam características favoráveis de dissipação de calor, alinhando-se às expectativas de alcançar maior densidade de potência por meio da miniaturização lógica.

Ben Sell, vice-presidente de Desenvolvimento Tecnológico da Intel, afirmou: "A Intel está avançando ativamente com o plano 'Quatro Anos, Cinco Nós de Processo' e está comprometida em integrar um trilhão de transistores em um único pacote até 2030. O PowerVia representa um marco significativo para ambas as metas. Ao adotar nós de processo produzidos experimentalmente e seus chips de teste, a Intel reduziu o risco de aplicar a entrega de energia pela parte traseira a nós de processo avançados e está trazendo a tecnologia de entrega de energia pela parte traseira para o mercado."

Entende-se que, em um terceiro artigo a ser apresentado no Simpósio VLSI, o especialista técnico da Intel, Mauro Kobrinsky, irá detalhar as conquistas da Intel em métodos mais avançados de implantação do PowerVia, tais como transmissão simultânea de sinal e fornecimento de energia nas faces frontal e traseira do wafer.