Non molto tempo fa, Intel ha raggiunto la tecnologia di alimentazione posteriore su un chip di test a livello di prodotto con il nome in codice “Blue Sky Creek” per soddisfare le esigenze di prestazioni della prossima era del computing. Intel ha presentato i risultati di questa ricerca attraverso due articoli presentati al VLSI Symposium tenutosi a Kyoto, in Giappone, dall’11 al 16 giugno di quest’anno. Maggiori informazioni

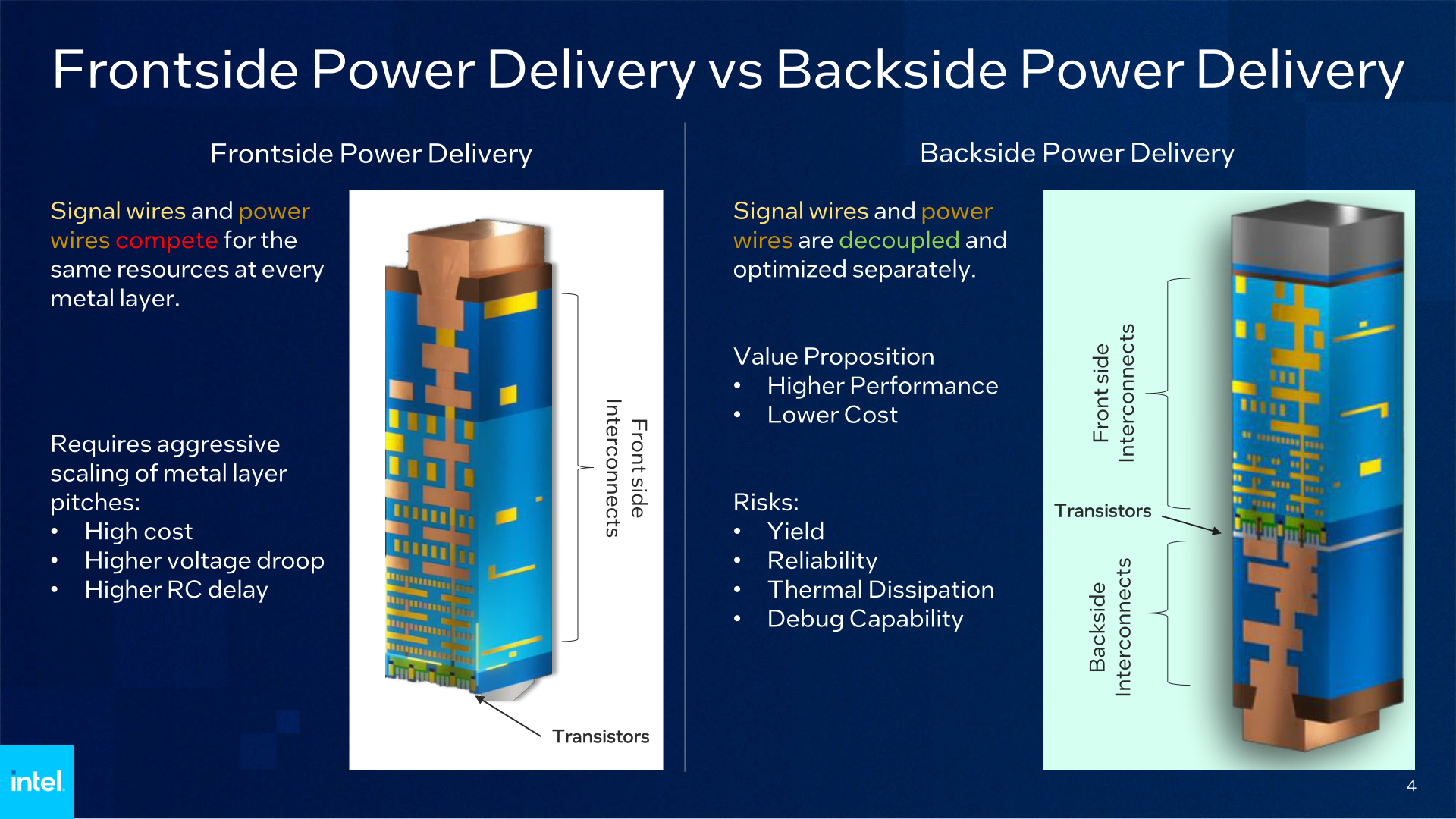

Man mano che i nodi di processo continuano a progredire, la tradizionale tecnologia di alimentazione frontale deve affrontare numerose sfide. Con linee di segnale e di alimentazione situate sul lato anteriore del wafer, devono condividere o addirittura competere per le risorse su ogni livello di metallo. Ciò richiede sforzi per aumentare la spaziatura tra i pin del livello di metallo, portando a costi e complessità più elevati. In risposta, l’industria ha iniziato a esplorare la possibilità di spostare la distribuzione dell’alimentazione sul retro. La tecnologia di alimentazione posteriore separa le linee di segnale e di alimentazione, spostando queste ultime sul retro del wafer, consentendo l’ottimizzazione individuale. Ciò porta a prestazioni più elevate e costi inferiori, anche se presenta anche sfide in termini di resa, affidabilità, dissipazione del calore e debug.

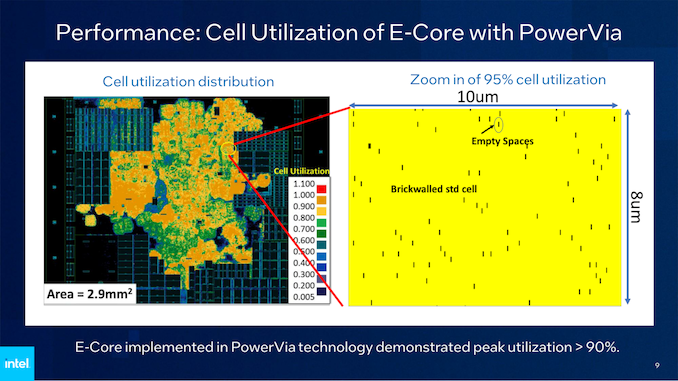

Si riferisce che sia i nodi di processo Intel 20A che Intel 18A adotteranno la tecnologia di alimentazione posteriore PowerVia insieme alla tecnologia gate all-around RibbonFET. Per affrontare queste sfide e accelerare lo sviluppo, Intel ha scelto di sviluppare le tecnologie PowerVia e RibbonFET separatamente, con PowerVia in testa. Attraverso i test, la tecnologia PowerVia migliora significativamente l’efficienza del chip, con tassi di utilizzo superiori al 90% per la maggior parte delle aree di celle standard. Le dimensioni dei transistor sono notevolmente ridotte, la densità unitaria è notevolmente aumentata e PowerVia raggiunge indicatori di resa e affidabilità elevati durante i test, dimostrando il valore atteso di questa tecnologia. I test rivelano anche che PowerVia riduce la tensione della piattaforma del 30% e porta a un aumento di frequenza del 6%.

Inoltre, Intel ha sviluppato una tecnologia di dissipazione del calore per prevenire problemi di surriscaldamento. Il team di debug ha anche ideato nuove tecniche per affrontare vari problemi che sorgono durante il debug di questa nuova struttura di progettazione del transistor. I chip di test PowerVia mostrano caratteristiche di dissipazione del calore favorevoli, in linea con le aspettative per il raggiungimento di una maggiore densità di potenza attraverso la miniaturizzazione logica.

Ben Sell, Vice Presidente dello Sviluppo Tecnologico di Intel, ha dichiarato: “Intel sta attivamente promuovendo il piano ‘Quattro anni, cinque nodi di processo’ e si impegna a integrare un trilione di transistor in un singolo package entro il 2030. PowerVia rappresenta una pietra miliare significativa per entrambi questi obiettivi. Adottando nodi di processo prodotti sperimentalmente e i loro chip di test, Intel ha ridotto il rischio di applicare l’alimentazione posteriore ai nodi di processo avanzati e sta portando la tecnologia di alimentazione posteriore sul mercato.”

Si comprende che in un prossimo terzo articolo che sarà presentato al VLSI Symposium, l’esperto tecnico di Intel Mauro Kobrinsky illustrerà più nel dettaglio i risultati della ricerca di Intel in metodi di implementazione più avanzati per PowerVia, come la trasmissione simultanea del segnale e l’alimentazione su entrambi i lati del wafer.