Belum lama ini, Intel berhasil menerapkan teknologi penyaluran daya dari sisi belakang pada chip uji tingkat produk dengan nama sandi "Blue Sky Creek" untuk memenuhi tuntutan kinerja era komputasi berikutnya. Intel memaparkan hasil penelitian ini melalui dua makalah yang dipresentasikan pada Simposium VLSI yang diselenggarakan di Kyoto, Jepang, pada tanggal 11 hingga 16 Juni tahun ini. Info Lebih Lanjut

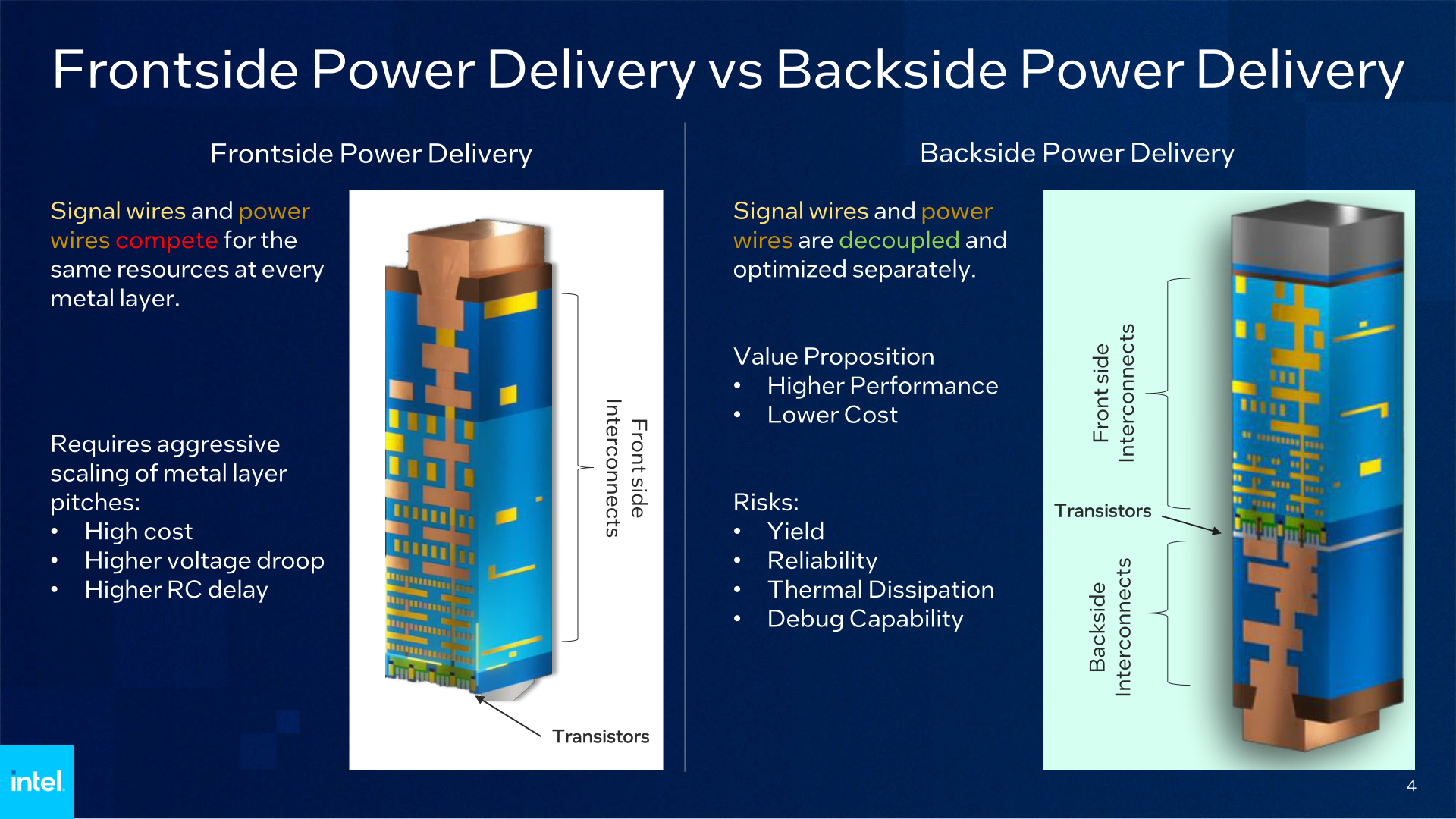

Seiring dengan terus majunya node proses, teknologi penyaluran daya sisi depan tradisional menghadapi berbagai tantangan. Karena jalur sinyal dan daya terletak di sisi depan wafer, keduanya harus berbagi atau bahkan bersaing untuk mendapatkan sumber daya pada setiap lapisan logam. Hal ini mengharuskan adanya upaya untuk memperbesar jarak antar pin pada lapisan logam, yang berujung pada biaya dan kompleksitas yang lebih tinggi. Sebagai tanggapan, industri telah mulai menjajaki kemungkinan untuk memindahkan distribusi daya ke sisi belakang. Teknologi penyaluran daya sisi belakang memisahkan jalur sinyal dan daya, memindahkan yang terakhir ke sisi belakang wafer, sehingga memungkinkan optimalisasi individual. Hal ini menghasilkan kinerja yang lebih tinggi dan biaya yang lebih rendah, meskipun juga menghadirkan tantangan dalam hal hasil, keandalan, pembuangan panas, dan debugging.

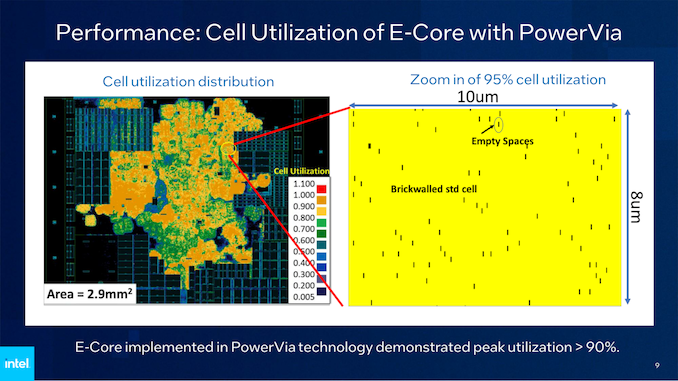

Dilaporkan, baik node proses Intel 20A maupun Intel 18A akan mengadopsi teknologi penyaluran daya sisi belakang PowerVia bersama dengan teknologi gerbang menyeluruh RibbonFET. Untuk mengatasi tantangan ini dan mempercepat pengembangan, Intel memilih untuk mengembangkan teknologi PowerVia dan RibbonFET secara terpisah, dengan PowerVia sebagai yang terdepan. Melalui pengujian, teknologi PowerVia secara signifikan meningkatkan efisiensi chip, dengan tingkat pemanfaatan melebihi 90% untuk sebagian besar area sel standar. Ukuran transistor berkurang secara signifikan, kepadatan unit meningkat pesat, dan PowerVia mencapai indikator hasil dan keandalan yang tinggi selama pengujian, yang menunjukkan nilai yang diharapkan dari teknologi ini. Pengujian juga mengungkapkan bahwa PowerVia mengurangi tegangan platform sebesar 30% dan menghasilkan peningkatan frekuensi sebesar 6%.

Selain itu, Intel telah mengembangkan teknologi pembuangan panas untuk mencegah masalah panas berlebih. Tim debugging juga telah merancang teknik-teknik baru untuk mengatasi berbagai masalah yang muncul selama proses debugging pada struktur desain transistor yang inovatif ini. Chip uji PowerVia menunjukkan karakteristik pembuangan panas yang baik, sesuai dengan harapan untuk mencapai kepadatan daya yang lebih tinggi melalui miniaturisasi logika.

Ben Sell, Wakil Presiden Pengembangan Teknologi di Intel, menyatakan, "Intel secara aktif mengimplementasikan rencana 'Empat Tahun, Lima Node Proses' dan berkomitmen untuk mengintegrasikan satu triliun transistor dalam satu paket pada tahun 2030. PowerVia merupakan tonggak penting bagi kedua tujuan tersebut. Dengan mengadopsi node proses yang diproduksi secara eksperimental beserta chip uji coba mereka, Intel telah mengurangi risiko penerapan teknologi pengiriman daya sisi belakang pada node proses canggih dan membawa teknologi pengiriman daya sisi belakang ke pasar."

Diketahui bahwa dalam makalah ketiga yang akan segera dipresentasikan pada Simposium VLSI, pakar teknis Intel, Mauro Kobrinsky, akan menguraikan pencapaian penelitian Intel terkait metode penerapan yang lebih canggih untuk PowerVia, seperti transmisi sinyal dan penyaluran daya secara bersamaan pada sisi depan dan belakang wafer.