Negli ultimi anni, la tecnologia del livello di ridistribuzione (RDL) ha guadagnato una notevole trazione. È una soluzione di packaging rivoluzionaria che ha trasformato il modo in cui confezioniamo gli IC.

In questo articolo, esploreremo la definizione di RDL, la sua funzione, i vantaggi, il processo, l’applicazione e il confronto con altre tecnologie di packaging IC.

Cos'è la tecnologia del livello di ridistribuzione?

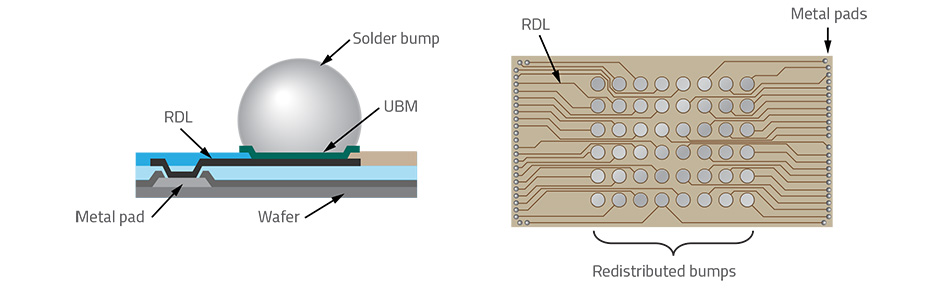

Il livello di ridistribuzione, noto anche come RDL, è uno strato di metallo che viene aggiunto a un circuito integrato o a un microchip per ridistribuire le connessioni elettriche. Questa tecnologia RDL è una soluzione di packaging avanzata per circuiti integrati (IC), che consente l’integrazione di più die in un unico package. È un processo di creazione di uno strato di metallo modellato sulla parte superiore dello strato dielettrico, che ridistribuisce l’ingresso/uscita (I/O) dell’IC in una nuova posizione. La nuova posizione è tipicamente sul bordo del die, che consente all’IC di essere collegato al circuito stampato (PCB) utilizzando la tecnologia di montaggio superficiale standard (SMT). La tecnologia RDL consente al progettista di posizionare il die in modo compatto ed efficiente, riducendo così l’ingombro complessivo del dispositivo.

La tecnologia RDL è fondamentale nello sviluppo di dispositivi elettronici moderni che diventano sempre più compatti e complessi. Consente ai chip di essere più piccoli, più veloci e più efficienti. È solitamente utilizzato nel packaging di dispositivi MEMS, sensori, dispositivi di potenza, memorie, microprocessori e processori grafici.

Funzione del livello di ridistribuzione

Il livello di ridistribuzione (RDL) svolge un ruolo fondamentale nell’estensione e nell’interconnessione del piano XY nella progettazione e produzione di chip.

Ridistribuisci la connessione I/O

I pad I/O (input/output) sono moduli di elaborazione dei pin del chip solitamente distribuiti sul bordo o sulla periferia del chip. Possono elaborare il segnale dei pin del chip e rilasciare il segnale del chip al pin dopo l’elaborazione.

RDL può facilitare la ridistribuzione delle connessioni I/O dal chip al package. L’RDL collega i pad di collegamento sul chip ai lead o alle sfere del package, il che consente un assemblaggio più facile e prestazioni migliori dell’IC.

Questo è naturalmente conveniente per il processo di legame del filo, ma è un po’ impegnativo per i chip flip. Pertanto, RDL è diventato la chiave in questo momento. Deposita uno strato di metallo e uno strato dielettrico corrispondente sulla superficie del chip, formando un filo metallico e riprogettando le porte IO in una nuova area più spaziosa, formando un layout a matrice di superficie.

Instrada segnali e potenza

Inoltre, l’RDL fornisce anche un mezzo per instradare segnali e potenza all’interno dell’IC. L’uso di RDL è diventato sempre più importante man mano che gli IC sono diventati più complessi e richiedono più connessioni I/O. Sono utilizzati in un’ampia gamma di applicazioni, come microprocessori, chip di memoria e sensori.

Vantaggi del livello di ridistribuzione

La tecnologia RDL offre numerosi vantaggi ai progettisti che cercano di creare dispositivi elettronici ad alte prestazioni, compatti ed economici. Alcuni dei vantaggi dell’utilizzo della tecnologia RDL nei package degli IC sono:

Ingombro ridotto

La tecnologia RDL consente l’integrazione di più die in un singolo package, riducendo così l’ingombro complessivo del dispositivo. Ciò consente ai progettisti di creare dispositivi elettronici più piccoli e compatti, essenziale per applicazioni come smartphone, dispositivi indossabili e dispositivi IoT.

Migliori prestazioni elettriche

La tecnologia RDL consente al progettista di posizionare il die in modo compatto ed efficiente, il che riduce la lunghezza degli interconnessioni. Questo, a sua volta, riduce il ritardo del segnale e migliora le prestazioni elettriche del dispositivo. La tecnologia RDL riduce anche la capacità parassita e l’induttanza, migliorando l’integrità del segnale del dispositivo.

Costo ridotto

La tecnologia RDL elimina la necessità di wire bonding e flip-chip bonding, che sono processi costosi e dispendiosi in termini di tempo. La tecnologia RDL riduce anche il numero di componenti necessari per il dispositivo, riducendo ulteriormente il costo del dispositivo. La tecnologia RDL è una soluzione economica per la creazione di circuiti integrati ad alte prestazioni che richiedono un fattore di forma ridotto.

Tipi di tecnologia Redistribution Layer

Esistono due tipi di tecnologia redistribution layer (RDL): fan-in e fan-out. La tecnologia RDL fan-in viene utilizzata per il packaging di un singolo die, mentre la tecnologia RDL fan-out viene utilizzata per il packaging di più die.

Tecnologia Fan-in RDL

La tecnologia fan-in RDL viene utilizzata per il packaging di un singolo die. La tecnologia fan-in RDL è anche nota come wafer-level package (WLP), che è un processo di creazione di un package direttamente sul wafer. La tecnologia fan-in RDL è una soluzione economica per la creazione di package piccoli e sottili.

La tecnologia fan-in RDL è adatta per applicazioni come sensori, dispositivi MEMS, dispositivi RF, microprocessori e dispositivi di memoria.

Tecnologia Fan-out RDL

La tecnologia fan-out RDL viene utilizzata per il packaging di più die. La tecnologia fan-out RDL è anche nota come wafer-level fan-out (WLFO), che è un processo di creazione di un package su un wafer ricostituito. La tecnologia fan-out RDL è una soluzione economica per la creazione di package ad alte prestazioni con un fattore di forma ridotto.

La tecnologia fan-out RDL è adatta per applicazioni come processori grafici, system-on-chip (SoC), dispositivi di memoria, dispositivi di potenza e dispositivi LED.

Processo Redistribution Layer

La tecnologia RDL è un processo complesso che prevede molti passaggi come deposizione dielettrica, deposizione di metallo, patterning e incisione. Di seguito sono riportati i flussi di processo per Fan-in RDL e Fan-out RDL.

Processo Fan-in RDL

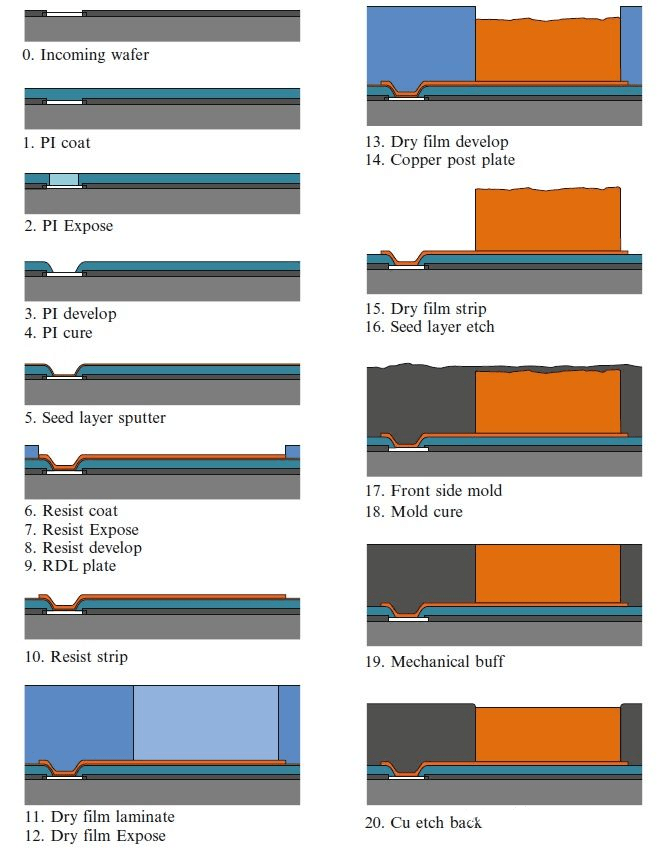

Il processo Fan-in RDL viene utilizzato nella produzione di soluzioni di packaging avanzate come Wafer-Level Chip-Scale Packaging (WLCSP) e System-in-Package (SiP) designs. Consente livelli di integrazione più elevati, fattori di forma ridotti e prestazioni migliorate per i dispositivi semiconduttori. Il processo prevede più passaggi come di seguito:

Il processo inizia con una wafer in entrata, che viene quindi rivestita con PI (Isolante a Fotoresistenza) nella fase 1. Segue l’esposizione del PI nella fase 2, lo sviluppo del PI nella fase 3 e la polimerizzazione del PI nella fase 4.

Nella fase 5, uno strato di seed viene spruzzato sulla wafer, che viene quindi rivestita con la resistenza nella fase 6. La resistenza viene quindi esposta nella fase 7, sviluppata nella fase 8 e l’RDL viene placcato nella fase 9.

Dopo di che, la resistenza viene rimossa nella fase 10 e un film secco viene laminato sulla wafer nella fase 11. Il film secco viene quindi esposto nella fase 12 e sviluppato nella fase 13. Successivamente, i post in rame vengono placcati sulla wafer nella fase 14 e il film secco viene rimosso nella fase 15.

Nella fase 16, lo strato di seed viene inciso e, nella fase 17, viene creato uno stampo sul lato anteriore. Lo stampo viene quindi polimerizzato nella fase 18 e la wafer viene lucidata meccanicamente nella fase 19. Infine, nella fase 20, l’eccesso di rame viene inciso all’indietro, completando il flusso di processo Fan-in RDL.

Processo RDL Fan-out

Simile al processo RDL Fan-in, il processo RDL Fan-out è anche un modo per creare package di chip più piccoli e dalle prestazioni più elevate con più connessioni. Ecco i passaggi di produzione:

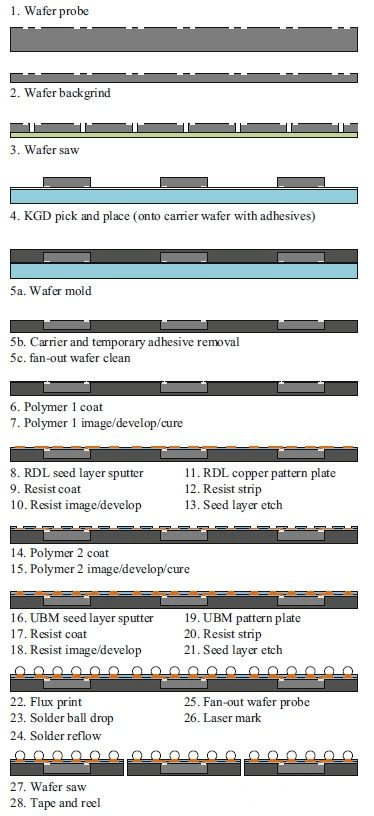

1. Sonda del wafer: questo è il test iniziale del wafer per garantire che soddisfi le specifiche richieste prima di passare alle fasi di lavorazione successive.

2. Rettifica posteriore del wafer: il retro del wafer viene rettificato a uno spessore specificato per ridurre lo spessore del package.

3. Taglio del wafer: il wafer viene tagliato in singoli die.

4. Prelievo e posizionamento KGD (Known Good Die): i die buoni vengono prelevati e trasferiti su un wafer di supporto con adesivo.

5a. Stampaggio del wafer: il wafer con i die attaccati al wafer di supporto viene stampato con un materiale dielettrico per formare una struttura fan-out.

5b. Rimozione del wafer di supporto e dell’adesivo temporaneo: il wafer di supporto viene rimosso dal wafer fan-out e qualsiasi adesivo temporaneo utilizzato durante il processo viene rimosso.

5c. Pulizia del wafer fan-out: il wafer fan-out viene pulito per rimuovere eventuali particelle o impurità residue.

6. Rivestimento polimerico 1: uno strato polimerico viene applicato sulla superficie del wafer fan-out per fungere da strato dielettrico.

7. Immagine/sviluppo/cura del polimero 1: lo strato polimerico viene modellato utilizzando la fotolitografia per creare la forma e le dimensioni desiderate della struttura RDL.

8. Deposizione a sputtering dello strato seme RDL: un sottile strato di rame o altro materiale conduttivo viene depositato sulla parte superiore dello strato polimerico mediante sputtering.

9. Rivestimento resist: uno strato di materiale resist viene applicato sopra lo strato seme.

10. Immagine/sviluppo resist: lo strato resist viene modellato utilizzando la fotolitografia per creare la forma e le dimensioni desiderate della struttura RDL.

11. Placcatura del rame del modello RDL: il rame viene depositato sulle aree esposte dello strato seme mediante elettrodeposizione, creando il modello RDL desiderato.

12. Rimozione resist: il materiale resist rimanente viene rimosso, lasciando solo il modello RDL in rame.

13. Incisione dello strato seme: la porzione non necessaria dello strato seme viene rimossa mediante incisione.

14. Rivestimento polimerico 2: un altro strato polimerico viene applicato sulla parte superiore della struttura RDL per fungere da strato dielettrico.

15. Immagine/sviluppo/cura del polimero 2: lo strato polimerico viene modellato utilizzando la fotolitografia per creare la forma e le dimensioni desiderate della struttura UBM.

16. Deposizione a sputtering dello strato seme UBM: un sottile strato di rame o altro materiale conduttivo viene depositato sulla parte superiore dello strato polimerico mediante sputtering.

17. Rivestimento resist: uno strato di materiale resist viene applicato sopra lo strato seme.

18. Immagine/sviluppo resist: lo strato resist viene modellato utilizzando la fotolitografia per creare la forma e le dimensioni desiderate della struttura UBM.

19. Placcatura del modello UBM: il rame viene depositato sulle aree esposte dello strato seme mediante elettrodeposizione, creando il modello UBM desiderato.

20. Rimozione resist: il materiale resist rimanente viene rimosso, lasciando solo il modello UBM in rame.

21. Incisione dello strato seme: la porzione non necessaria dello strato seme viene rimossa mediante incisione.

22. Stampa del flusso: un materiale di flusso viene applicato sui pad UBM.

23. Gocciolamento delle sfere di saldatura: le sfere di saldatura vengono posizionate sui pad UBM.

24. Riflusso della saldatura: le sfere di saldatura vengono riscaldate per fondere e formare connessioni tra i pad UBM e i lead o i bump esterni.

25. Sonda del wafer fan-out: il circuito integrato confezionato viene testato per garantire che soddisfi le specifiche richieste.

26. Marcatura laser: un identificatore univoco o un codice a barre viene inciso sulla superficie del circuito integrato utilizzando un laser.

27. Taglio del wafer: il wafer fan-out viene tagliato in singoli package.

28. Nastro e bobina: i singoli circuiti integrati confezionati vengono montati su una bobina per una facile manipolazione e spedizione.

Applica RDL al confezionamento avanzato

Nel packaging avanzato come il package a livello di wafer con fan-in (FIWLP) e il package a livello di wafer con fan-out (FOWLP), l’RDL è la tecnologia più critica. È l’ascesa di questa tecnologia che ha permesso agli impianti di packaging di competere con le fonderie di wafer nella tecnologia di packaging fan-out. Attraverso l’RDL, l’IOPad può essere realizzato in diversi tipi di package a livello di wafer in FIWLP o FOWLP. In FIWLP, i bump sono tutti cresciuti sul die e la connessione tra il die e il pad dipende principalmente dalla linea metallica dell’RDL. Dopo il packaging, l’IC è quasi delle stesse dimensioni dell’area del die. In FOWLP, i bump possono crescere all’esterno del die e l’IC dopo il packaging è più grande dell’area del die (1,2 volte).

In particolare, nel packaging avanzato 2.5D, oltre al TSV sul substrato di silicio, l’RDL è anch’esso indispensabile. Prendendo l’InFO di TSMC, un rappresentante del packaging avanzato 2.5D, come esempio, InFO utilizza uno o più die nudi sul carrier, che vengono poi incorporati nel wafer ricostituito del composto di stampaggio. Quindi, gli interconnessioni RDL e gli strati dielettrici vengono fabbricati sul wafer, che è un flusso di processo “chip first”. L’InFO a die singolo fornisce un elevato numero di bump e le linee RDL si estendono dall’area del chip verso l’esterno, formando una topologia “fan-out”.

Quale tecnologia di Redistribution Layer dovrei usare?

Come abbiamo menzionato prima, ci sono due tecnologie RDL: RDL Fan-in e RDL Fan-out. Quindi come scegliere quella giusta per creare dispositivi elettronici ad alte prestazioni, compatti ed economici? Dipende da diversi fattori come il tipo di applicazione, il numero di die e i requisiti di prestazioni.

Applicazione

La tecnologia RDL fan-in è adatta per applicazioni come sensori, dispositivi MEMS e dispositivi RF. La tecnologia RDL fan-out è adatta per applicazioni come processori grafici, system-on-chip (SoC) e dispositivi di memoria.

Numero di Die

La tecnologia RDL fan-in è adatta per il packaging di un singolo die, mentre la tecnologia RDL fan-out è adatta per il packaging di più die.

Requisiti di Prestazione

La tecnologia RDL fan-in è adatta per creare package piccoli e sottili, mentre la tecnologia RDL fan-out è adatta per creare package ad alte prestazioni con un fattore di forma ridotto.

Confronto tra RDL e altre tecnologie di Packaging IC

A causa dei diversi processi, ci sono diverse tecnologie di packaging disponibili per i circuiti integrati. Ulteriori informazioni sulle loro differenze possono essere trovate nella tabella sottostante:

| IC Packaging | Description | Advantages | Disadvantages | Applications |

|---|---|---|---|---|

| Wire Bonding | Connecting the IC to the PCB using wires | Low cost, flexible, proven technology | Limited performance, not suitable for high-frequency and high-power applications | Consumer electronics, automotive, medical devices |

| Flip-Chip Bonding | Chips are bonded face-down to the substrate, Connecting the IC to the PCB using solder bumps | High performance, high-density, low inductance | Expensive, requires precise alignment and underfilling | High-speed data communication, high-power applications, microprocessors |

| Through-Silicon Via (TSV) | Creating vertical interconnects through the silicon substrate | Shorter interconnect lengths, higher performance, smaller form factor | Complex and expensive manufacturing process, thermal and mechanical stress issues | Memory devices, image sensors, 3D ICs |

| Chip-scale package (CSP) | Replacing the lead frame with a substrate | Small form factor, high density, low cost | Limited I/O, susceptibility to mechanical and thermal stress | Mobile devices, wearable technology |

| Integrated Fan-out (InFO) | Integrated package of multiple chips and the soldering point of the pin is outside of the chip | High density, small form factor, low power consumption | Complex manufacturing process, high cost | Mobile devices, IoT, wearable technology |

| High Bandwidth Memory (HBM) | 3D stacking technology | High bandwidth, low power consumption | Expensive, limited scalability | High-performance computing, graphics processing |

| Chip on Wafer on Substrate (CoWoS) | Integrate chip and silicon wafer (substrate) together | High bandwidth, low power consumption, heterogeneous integration | Complex manufacturing process, high cost | High-performance computing, graphics processing |

| Redistribution Layer (RDL) | Creating a patterned metal layer on top of the dielectric layer | High density, fine pitch, low profile | Limited power handling capability, susceptibility to mechanical and thermal stress | Mobile devices, consumer electronics |

| Bump Technology | Depositing small metal bumps on the chip | Low cost, simple manufacturing process, flexible design | Limited performance, not suitable for high-speed and high-power applications | Consumer electronics, automotive, medical devices |

Aziende che Offrono Soluzioni di Tecnologia Redistribution Layer

Ci sono diverse aziende che offrono soluzioni di tecnologia redistribution layer (RDL) come:

ASE Group

ASE Group è un fornitore globale di servizi di produzione di semiconduttori. ASE Group offre un’ampia gamma di soluzioni tecnologiche RDL per varie applicazioni come memoria, microprocessori e processori grafici.

Amkor Technology

Amkor Technology è un fornitore globale di servizi di packaging e test di semiconduttori. Amkor Technology offre un’ampia gamma di soluzioni tecnologiche RDL per varie applicazioni come sensori, dispositivi MEMS e dispositivi di potenza.

TSMC

TSMC è una fonderia globale di semiconduttori che offre un’ampia gamma di soluzioni tecnologiche RDL per varie applicazioni come system-on-chip (SoC), dispositivi di memoria e dispositivi di potenza.

Conclusione

La tecnologia del layer di redistribuzione (RDL) è una soluzione di packaging rivoluzionaria che ha trasformato il modo in cui confezioniamo i circuiti integrati (CI). Permette di realizzare più connessioni su un singolo chip, riducendo così l’ingombro complessivo del dispositivo. Pertanto, viene utilizzata in varie applicazioni come smartphone, dispositivi indossabili e dispositivi IoT. Il futuro della tecnologia RDL nel packaging dei CI è promettente e si prevede che avrà un impatto significativo sull’industria elettronica negli anni a venire.