À mesure que la vitesse de commutation de sortie des circuits intégrés augmente et que la densité des cartes PCB augmente, l’intégrité du signal est devenue l’un des problèmes qui doivent être pris en compte dans la conception de PCB numériques à haute vitesse. Parce que les problèmes d’intégrité du signal peuvent entraîner une sortie de données incorrecte par le système, le circuit ne fonctionne pas correctement ou même complètement Ne fonctionne pas. Alors, comment prendre pleinement en compte le facteur d’intégrité du signal dans le processus de conception de la carte PCB et prendre des mesures de contrôle efficaces ? Veuillez lire cet article plus loin.

Qu'est-ce que l'intégrité du signal PCB ?

L’intégrité du signal du PCB fait référence à la capacité du signal à répondre avec le bon timing et la bonne tension dans le circuit. C’est un état où le signal n’est pas endommagé, et il indique la qualité du signal sur la ligne de signal.

Différents problèmes d'intégrité du signal

Les problèmes d’intégrité du signal peuvent causer ou entraîner directement une distorsion du signal, des erreurs de timing, des données incorrectes, des lignes d’adresse et de contrôle, un dysfonctionnement du système et même des plantages du système. Les principaux problèmes d’intégrité du signal comprennent : le délai, la réflexion, le bruit de commutation synchrone, l’oscillation, le rebond de masse, la diaphonie, etc.

Délai

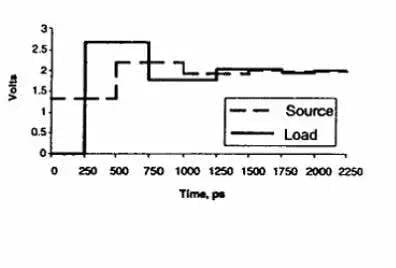

Le délai signifie que le signal est transmis à une vitesse limitée sur les fils de la carte PCB, et que le signal est envoyé de l’extrémité d’émission à l’extrémité de réception, et qu’il y a un délai de transmission entre les deux. Le délai du signal affectera la synchronisation du système, et le délai de transmission dépend principalement de la longueur du fil et de la constante diélectrique du milieu autour du fil. Dans un système numérique à haute vitesse, la longueur de la ligne de transmission du signal est le facteur le plus direct affectant la différence de phase de l’impulsion d’horloge. La différence de phase de l’impulsion d’horloge signifie que les deux signaux d’horloge générés au même moment ne sont pas synchronisés lorsqu’ils arrivent à l’extrémité de réception. La différence de phase de l’impulsion d’horloge réduit la prévisibilité de l’arrivée des fronts de signal. Si la différence de phase de l’impulsion d’horloge est trop importante, un signal erroné sera généré à l’extrémité de réception. Comme le montre la figure ci-dessous, le délai de la ligne de transmission est devenu une partie importante du cycle de l’impulsion d’horloge.

Réflexion

La réflexion est l’écho sur la sous-ligne de transmission. Lorsque le délai de signal est beaucoup plus long que le temps de transition du signal, la ligne de signal doit être considérée comme une ligne de transmission. Lorsque l’impédance caractéristique de la ligne de transmission ne correspond pas à l’impédance de charge, une partie de la puissance du signal (tension ou courant) est transmise sur la ligne et atteint la charge, mais une partie est réfléchie. Si l’impédance de charge est inférieure à l’impédance d’origine, la réflexion est négative. Sinon, la réflexion est positive. Les variations de la géométrie du routage, la terminaison incorrecte de la ligne de transmission, la transmission à travers les connecteurs et les discontinuités dans les plans d’alimentation peuvent provoquer de telles réflexions.

Bruit de commutation simultanée (SSN)

Le bruit de commutation simultané sera généré si de nombreux signaux numériques sur le PCB sont commutés de manière synchrone (tels que le bus de données du CPU, le bus d’adresse, etc.). Ceci est dû au fait qu’il existe une impédance sur la ligne d’alimentation et la masse, et qu’il y aura un rebond de masse sur le plan de masse (ground bounce). L’intensité du SSN et du rebond de masse dépend également des caractéristiques d’E/S du circuit intégré, de l’impédance de la couche d’alimentation et du plan du PCB, ainsi que de la disposition et du routage des dispositifs à haute vitesse sur le PCB.

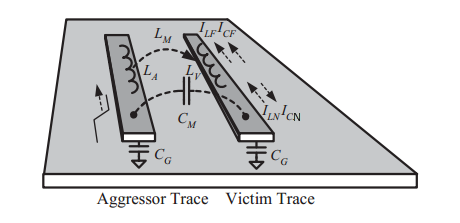

Diaphonie

La diaphonie est le couplage entre deux lignes de signal, et l’inductance mutuelle et la capacitance mutuelle entre les lignes de signal provoquent du bruit sur la ligne. Le couplage capacitif induit un courant couplé tandis que le couplage inductif induit une tension couplée. Le bruit de diaphonie provient du couplage électromagnétique entre les réseaux de signaux, entre les systèmes de signaux et les systèmes de distribution d’énergie, et entre les vias. Le croisement peut provoquer des horloges fausses, des erreurs de données intermittentes, etc., et affecter la qualité de la transmission des signaux adjacents. En fait, nous n’avons pas besoin d’éliminer complètement la diaphonie, il suffit de la maintenir dans la tolérance du système. Les paramètres de la couche de la carte PCB, l’espacement des lignes de signal, les caractéristiques électriques du pilote et du récepteur, et la méthode de terminaison de la ligne de base ont tous un certain impact sur la diaphonie.

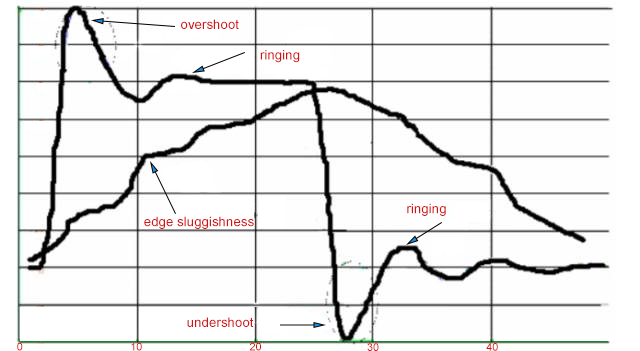

Dépassement et Sous-dépassement

Le dépassement est le premier pic ou la première vallée dépassant la tension définie. Pour les fronts montants, il fait référence à la tension la plus élevée, et pour les fronts descendants, il fait référence à la tension la plus basse. Le sous-dépassement se produit lorsque la vallée ou le pic suivant dépasse la tension définie. Un dépassement excessif peut provoquer le fonctionnement des diodes de protection, entraînant leur défaillance prématurée. Un sous-dépassement excessif peut provoquer des erreurs de données ou d’horloge parasites (mauvaise manipulation).

Sonnerie et Arrondissement

Le phénomène d’oscillation est un dépassement et un sous-dépassement répétés. L’oscillation du signal est causée par l’inductance et la capacité de transition sur la ligne, ce qui correspond à un état sous-amorti. L’oscillation de contour est un état sur-amorti. Les oscillations et les oscillations orbitales, comme les réflexions, sont causées par divers facteurs. L’oscillation peut être réduite avec une terminaison appropriée, mais elle ne peut pas être complètement éliminée.

Bruit de rebond de masse et bruit de retour

Bruit de rebond de masse

Lorsqu’il y a une forte montée de courant dans le circuit, cela provoque un bruit de rebond de masse. Par exemple, si les sorties d’un grand nombre de puces sont activées en même temps, un courant transitoire important circule à travers le plan d’alimentation de la puce et de la carte. Le bruit de l’alimentation est alors induit par l’inductance et la résistance du boîtier de la puce et du plan d’alimentation, ce qui crée des fluctuations de tension et des variations sur le plan de masse réel (0 V). Ce bruit affecte le fonctionnement des autres composants. Une augmentation de la capacité de charge, une diminution de la résistance de charge, une augmentation de l’inductance de masse et une augmentation du nombre de dispositifs de commutation entraîneront tous une augmentation du rebond de masse.

Bruit de retour

Le bruit de retour du plan de masse est généré lorsque les signaux numériques voyagent vers la zone de masse analogique. Cela peut être causé par la division du plan de masse (y compris l’alimentation et la masse), par exemple, le plan de masse est divisé en masse numérique, masse analogique, masse de blindage, etc. De même, les plans d’alimentation peuvent également être divisés en 2,5 V, 3,3 V, 5 V, etc. Par conséquent, dans la conception de PCB multi-tension, nous devons porter une attention particulière au bruit de rebond et au bruit de retour du plan de masse.

Causes des problèmes d'intégrité du signal

Des facteurs tels que les paramètres des composants et des cartes PCB, la disposition des composants sur les cartes PCB et le câblage des lignes de signaux à haute vitesse peuvent causer des problèmes d’intégrité du signal. Pour la disposition des PCB, l’intégrité du signal doit fournir des composants de terminaison, des stratégies de placement et des informations de routage pour la disposition du circuit.

Comment optimiser l'intégrité du signal ?

Le problème d’intégrité du signal n’est pas causé par un seul facteur, mais par plusieurs facteurs dans la conception au niveau de la carte. Par conséquent, nous devons utiliser différentes méthodes pour améliorer l’intégrité du signal en fonction de situations spécifiques.

Analyse des diaphonies

La taille de la diaphonie est inversement proportionnelle à l’espacement des lignes et proportionnelle à la longueur parallèle de la ligne et à la fréquence du signal. La diaphonie variera en fonction de la charge du circuit. Pour la même topologie et la même situation de câblage, plus la charge est importante, plus la diaphonie est importante. Dans les circuits numériques, le changement de front du signal a le plus grand impact sur la diaphonie, et plus les fronts changent rapidement, plus la diaphonie est importante. Compte tenu des caractéristiques ci-dessus de la diaphonie, nous pouvons utiliser les méthodes suivantes pour réduire la diaphonie :

- Choisir un dispositif lent pour réduire le taux de transition du front du signal ;

- Éviter de mélanger différents types de signaux ;

- Réduire les interférences de couplage en réduisant la charge ;

- Minimiser la longueur parallèle entre les lignes de transmission adjacentes ;

- Augmenter la distance entre les conducteurs où un couplage capacitif peut se produire ;

- Une approche plus efficace consiste à isoler les fils avec des fils de masse ;

- Insérer un fil de masse entre les fils de signal adjacents ;

- Minimiser le nombre de boucles et la surface de la boucle ;

- Éviter de partager le même fil pour la boucle de signal ;

- Les couches de signal de deux couches adjacentes doivent éviter le câblage parallèle autant que possible ;

- Les signaux sensibles à la diaphonie doivent être disposés dans la couche interne autant que possible ;

analyse de réflexion

Les réflexions se produisent chaque fois qu’un signal rencontre un changement d’impédance lors de son trajet le long d’une ligne de transmission. La principale façon de résoudre le problème de réflexion est d’effectuer une adaptation d’impédance de terminaison. Il existe généralement deux stratégies pour la terminaison de la ligne de transmission : la terminaison parallèle et la terminaison série.

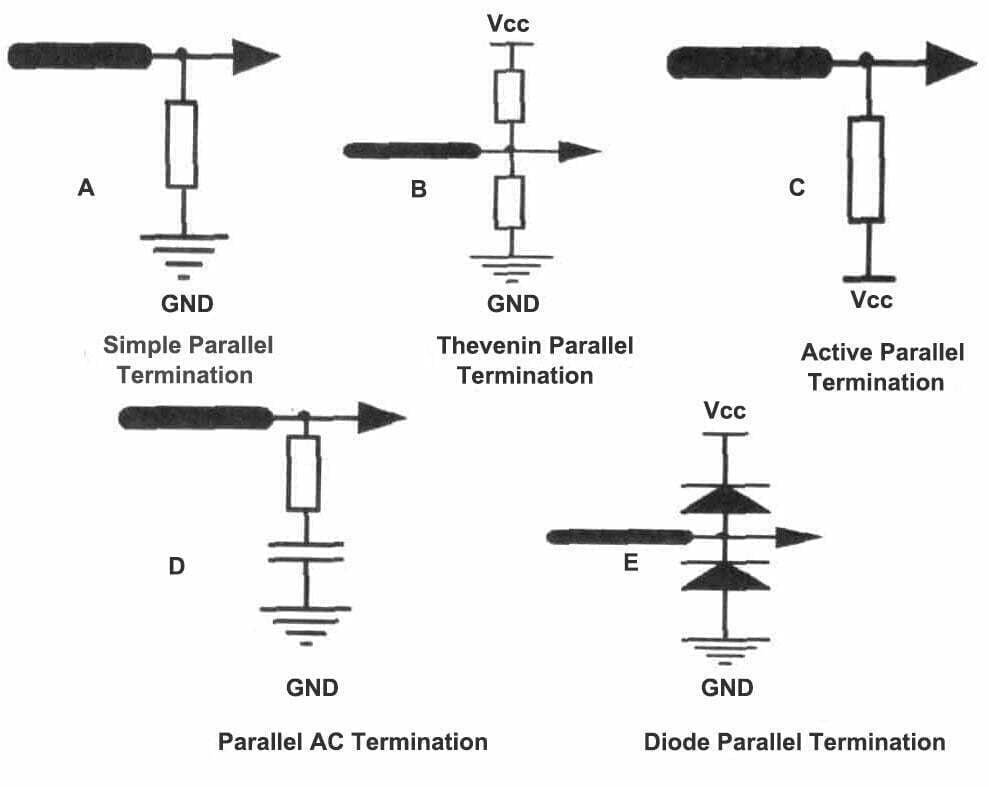

Terminaison parallèle

La terminaison parallèle sert principalement à connecter l’impédance de tirage vers le haut ou vers le bas aussi près que possible de l’extrémité de la charge afin d’obtenir une adaptation d’impédance du terminal. Selon les différents environnements d’application, la terminaison parallèle peut être divisée en plusieurs types, comme indiqué dans la figure ci-dessous.

Terminaison série

La terminaison série est obtenue en insérant en série une résistance dans la ligne de transmission aussi près que possible de la source. La terminaison série consiste à adapter l’impédance de la source de signal, la résistance de la résistance série insérée plus l’impédance de sortie de la source de commande doit être supérieure ou égale à l’impédance de la ligne de transmission. Cette stratégie supprime le signal réfléchi par la charge en rendant le coefficient de réflexion de l’extrémité source nul (l’entrée de l’extrémité de la charge est à haute impédance et n’absorbe pas d’énergie) et le réfléchit ensuite vers l’extrémité de la charge depuis l’extrémité source.

Modélisation de l'analyse de l'intégrité du signal

Une modélisation et une simulation de circuit appropriées constituent la solution d’intégrité du signal la plus courante. Dans la conception de circuits à haute vitesse, l’analyse par simulation montre de plus en plus sa supériorité. Car elle peut fournir aux concepteurs des résultats de conception précis et intuitifs. De cette façon, nous pouvons détecter les problèmes tôt et les corriger à temps. Il existe trois méthodes de modélisation de circuit couramment utilisées : le modèle SPICE, le modèle IBIS et le modèle Verilog-A.

Modèle SPICE

SPICE est un simulateur de circuits analogiques généraliste puissant. Il se compose de deux parties : l’équation du modèle et les paramètres du modèle. Étant donné que l’équation du modèle est fournie, le modèle SPICE peut être très étroitement lié à l’algorithme du simulateur, et de meilleurs résultats d’efficacité et d’analyse peuvent être obtenus.

Modèle IBIS

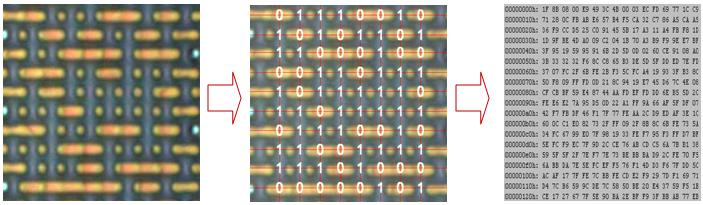

Le modèle IBIS est un modèle spécialement utilisé pour l’analyse de l’intégrité du signal numérique au niveau de la carte PCB et au niveau du système. Il utilise la forme de tableaux I/V et V/T pour décrire les caractéristiques des cellules et des broches d’E/S des circuits intégrés numériques. La précision de l’analyse du modèle IBIS dépend principalement du nombre de points de données et de la précision des données dans les tableaux I/V et V/T. Comparé au modèle SPICE, la charge de calcul du modèle IBIS est très faible.

Conclusion

Avec le développement continu de la microélectronique, l’utilisation de dispositifs à grande vitesse et la conception de systèmes numériques à grande vitesse sont en augmentation. Les débits de données du système, les fréquences d’horloge et les densités de circuit augmentent également. Par conséquent, les exigences de conception pour la carte PCB sont de plus en plus élevées, en particulier la question de l’intégrité du signal. Pour garantir que le PCB possède une bonne intégrité du signal, une variété de facteurs d’influence doivent être pris en compte de manière globale.