SWD y JTAG son interfaces de depuración muy populares para los MCU basados en Cortex-M. Sin embargo, estas dos interfaces son diferentes tanto en su estructura como en sus aplicaciones. En este artículo, presentaremos sus pines, su principio de funcionamiento y sus ventajas e inconvenientes.

Interfaz SWD

SWD, Serial Wire Debug, es un protocolo diseñado por ARM para programar y depurar sus microcontroladores. Se basa en la arquitectura de depuración ARM CoreSight y permite leer y escribir registros de chips a través de paquetes de datos. SWD es un protocolo de dos cables para acceder a las interfaces de depuración ARM. Forma parte de la especificación de arquitectura de interfaz de depuración ARM y sirve como alternativa a JTAG. En los casos en los que el diseño de la placa de circuito impreso es limitado y los recursos de pines son restringidos, SWD es una buena opción. Muchos depuradores del mercado admiten interfaces de depuración SWD, como ST-Link, J-Link, e-Link, GD-Link y otros.

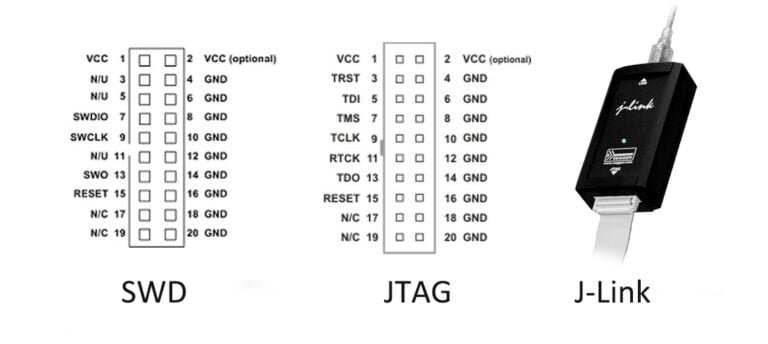

Pines SWD

SWDIO: Entrada/salida de datos por cable serie, pin de entrada y

salida de datos serie SWCLK: Reloj de cable serie, pin de reloj de línea serie

En el caso de SWDIO, se trata de un pin de datos bidireccional (entrada y salida), y la línea debe estar conectada a tierra en la placa de circuito (ARM recomienda 100 K).

¿Cómo funciona SWD?

Los dispositivos externos, como las sondas de depuración, se conectan a SWDIO/SWCLK para acceder directamente al puerto de depuración de cable serie (SW-DP). SW-DP puede acceder a uno o varios puertos de acceso (AP) y, a través de los AP, se puede acceder al resto de los registros del sistema. Un AP importante para las CPU de la serie Cortex M es el AHB-AP, que actúa como maestro en el bus AHB interno. En otras palabras, el AHB-AP puede acceder al mapa de memoria del núcleo interno. Dado que la memoria flash interna, la SRAM, los componentes de depuración y los dispositivos periféricos están todos mapeados en memoria, el AHB-AP puede controlar todo el dispositivo, incluida su programación. Todo el proceso de funcionamiento del SWD es jerárquico, con señales de reloj que se introducen desde el pin SWCLK y señales de datos que se introducen/salen desde el pin SWDIO. Inicialmente, el depurador opera en el SW-DP para determinar los parámetros de los registros AP, lo que permite la manipulación del mapa de memoria Cortex.

Ventajas de SWD

- Reducción del número de señales

- Fiabilidad a altas velocidades

- Probabilidad reducida de fallos

- Compatibilidad con simulaciones JTAG

- Requiere menos pines para su funcionamiento

Interfaz JTAG

JTAG, Joint Test Action Group, se utilizaba originalmente para probar chips. Este grupo inició debates a finales de la década de 1980 y publicó oficialmente documentos que interpretaban las normas IEEE en 1990. (IEEE son las siglas de Institute of Electrical and Electronics Engineers, una organización internacional responsable de publicar normas como WiFi y Bluetooth). El protocolo que propusieron se documentó en la norma IEEE 1149.1 en 1990. Desde entonces, este documento ha sido objeto de revisiones y mejoras, y la norma más reciente en el momento de redactar este artículo es la IEEE 1149.7.

Pines JTAG

- TDI: Entrada de datos de prueba, un pin de entrada serie.

- TDO: Salida de datos de prueba, un pin de salida serie.

- TCK: Reloj de prueba, un pin de reloj.

- TMS: Selección de modo de prueba, un pin de selección de modo (señal de control).

- TRST: Reinicio de prueba, un pin de reinicio.

¿Cómo funciona JTAG?

El principio de JTAG consiste en definir un puerto de acceso de prueba (TAP) dentro del dispositivo. Esto permite probar los nodos internos utilizando herramientas de prueba JTAG especializadas. Las pruebas JTAG permiten conectar varios dispositivos en serie a través de una interfaz JTAG, formando una cadena JTAG para la prueba de dispositivos individuales. Hoy en día, las interfaces JTAG también se utilizan comúnmente para operaciones programables en el sistema (ISP), como la programación de dispositivos FLASH. En términos de estructura de hardware, la interfaz JTAG consta de dos partes: el puerto JTAG y el controlador. Los dispositivos compatibles con la interfaz JTAG pueden ser microprocesadores (MPU), microcontroladores (MCU), PLD, CPLD, FPGA, DSP, ASIC u otros chips que cumplan con las especificaciones IEEE 1149.1. La norma IEEE 1149.1 exige la presencia de una unidad de registro de desplazamiento denominada unidad de exploración de límites (BSU) para cada pin de un chip de circuito integrado digital. Conecta el circuito JTAG con el circuito lógico central, al tiempo que aísla este último de los pines del chip. Todas las unidades de exploración de límites del chip constituyen el registro de exploración de límites (BSR). El circuito del registro de exploración de límites solo está activo durante las pruebas JTAG y no afecta a la funcionalidad del chip durante el funcionamiento normal.

El protocolo JTAG controla la transición de la máquina de estados TAP a través de la señal TMS. Después de encender el sistema, el controlador TAP entra primero en el estado Test-Logic Reset (reinicio de la lógica de prueba) y, a continuación, pasa secuencialmente por los estados Run-Test/Idle (ejecución de prueba/inactivo), Select-DR-Scan (selección de exploración DR), Select-IR-Scan (selección de exploración IR), Capture-IR (captura IR), Shift-IR (desplazamiento IR), Exit1-IR (salida 1 IR) y Update-IR (actualización IR) antes de volver a Run-Test/Idle (ejecución de prueba/inactivo). Durante este proceso, las transiciones de estado son impulsadas por la señal TCK (flanco ascendente), y las señales TMS se utilizan para seleccionar el estado TAP. En el estado Capture-IR, se carga una secuencia lógica específica en el registro de instrucciones; en el estado Shift-IR, se puede desplazar una instrucción específica al registro de instrucciones; y en el estado Update-IR, la instrucción que acaba de introducirse en el registro de instrucciones se utiliza para actualizar el registro de instrucciones. Por último, el sistema vuelve al estado Run-Test/Idle, donde la instrucción surte efecto, completando el acceso a la instrucción y a los registros. Después de volver al estado Run-Test/Idle, en función del contenido del registro de instrucciones, se selecciona el registro de datos necesario y comienza el trabajo en los registros de datos.

Ventajas de JTAG

- JTAG no se limita a los chips ARM, sino que también es compatible con otros chips, como el conocido MSP430.

- JTAG tiene una amplia gama de aplicaciones para programación, depuración y pruebas de producción.

- JTAG es un grupo independiente que evoluciona con el desarrollo del protocolo.

Conclusión

JTAG y SWD son dos importantes interfaces de depuración de sistemas integrados, cada una con sus propias ventajas e inconvenientes. La elección de la interfaz depende de los requisitos del proyecto, la compatibilidad del hardware y las necesidades de rendimiento. En el caso de sistemas complejos, puede ser necesario utilizar JTAG para obtener un mayor control y funcionalidad, mientras que SWD puede ser más adecuado para sistemas con recursos limitados. Tener en cuenta todos estos factores le ayudará a tomar decisiones informadas para un desarrollo y una depuración más eficaces de los sistemas integrados.