IC-Fehleranalyse

Umfassende technische Ressource für Methoden, Werkzeuge und Fallstudien zur Halbleiterfehleranalyse

Was ist IC-Fehleranalyse?

Die Fehleranalyse integrierter Schaltungen (ICs) ist ein systematischer Prozess zur Identifizierung, Eingrenzung und Bestimmung der Ursache von Halbleiterfehlern. Diese wichtige Ingenieurdisziplin kombiniert fortschrittliche Bildgebungsverfahren, elektrische Prüfverfahren und Materialwissenschaften, um Probleme in integrierten Schaltungen verschiedenster Branchen zu lösen.

Eine effektive Fehleranalyse verbessert die Produktzuverlässigkeit, senkt die Fertigungskosten, beschleunigt die Markteinführung und gewährleistet die Einhaltung von Industriestandards. Sie spielt eine entscheidende Rolle in der Qualitätskontrolle, der Zuverlässigkeitstechnik und den Produktverbesserungszyklen.

Hauptziele der IC-Fehleranalyse

- Identifizieren Sie die Hauptursachen von IC-Ausfällen durch systematische Untersuchung

- Ermitteln Sie, ob die Fehler auf Konstruktion, Fertigung oder Anwendung zurückzuführen sind.

- Entwickeln Sie Korrekturmaßnahmen, um zukünftige Ausfälle zu verhindern.

- Zuverlässigkeit und Leistungsfähigkeit integrierter Schaltungen validieren

- Unterstützung für Fehlerberichterstattung und Zuverlässigkeitsdatenanalyse

Technische Leitfäden und Methoden

Diagnose-Flussdiagramm

Systematischer Ansatz von der Identifizierung der Fehlersymptome bis zur Ermittlung der Grundursache

Kein Strom-/Ausgangsausfallpfad

- 1. Überprüfung auf ESD-Schäden mittels SEM/EDS-Analyse

- 2. Lötstellen mit 3D-Röntgeninspektion prüfen

- 3. Prüfung auf Gate-Oxid-Durchschlag mittels EMMI

- 4. Durchführung von Durchgangsprüfungen mit OBIRCH

- 5. Analysieren Sie die Paketintegrität mit C-SAM.

Fehlerpfad für intermittierende Störungen

- 1. BGA-Mikrorisse mittels C-SAM ausschließen

- 2. Überprüfung auf thermische Belastung mittels Infrarotbildgebung

- 3. Prüfung auf designbedingte Latch-up-Probleme mittels Schaltungssimulation

- 4. Überprüfung der Integrität des Stromverteilungsnetzes

EMMI-Bedienungsanleitung

Schrittweiser Arbeitsablauf für die Emissionsmikroskopie-Analyse

Gerätevorbereitung

Schalten Sie das Gerät im Fehlerzustand ein und stellen Sie eine ausreichende Kühlung sicher.

Dunkelkammer-Einrichtung

Positionieren Sie das Gerät unter dem EMMI-Mikroskop und stellen Sie die korrekte Ausrichtung sicher.

Kamerakonfiguration

Stellen Sie die geeignete Belichtungszeit (typischerweise 10–60 Sekunden) und die Empfindlichkeit ein.

Bildaufnahme

Nehmen Sie mehrere Bilder mit unterschiedlichen Belichtungszeiten auf, um optimale Ergebnisse zu erzielen.

Analyse & Überlagerung

Emissionspunkte mit dem Konstruktionsplan überlagern, um fehlerhafte Strukturen zu identifizieren

Tipp zur Fehlerbehebung

Wenn keine Hotspots auftreten, überprüfen Sie, ob sich der Chip in einem reproduzierbaren Fehlerzustand befindet und ob der Fehlermechanismus Photonenemissionen erzeugt (bei offenen Stromkreisen ist dies typischerweise nicht der Fall).

Häufige Fallstricke bei der Fehleranalyse

ESD-Schaden übersehen

Die Gefahr von Schäden durch elektrostatische Entladung beim Umgang mit Chips, insbesondere von CMOS-Chips, darf nicht ausreichend berücksichtigt werden. Überprüfen Sie daher stets die Funktionsfähigkeit des Armbands und die Erdungsprotokolle.

Unzureichende Leistungsreduzierung

Durch den Betrieb mit über 80 % Auslastung kann es zu Widerstandsdurchbrennen kommen. Um die Zuverlässigkeit unter verschiedenen Bedingungen zu gewährleisten, wird eine Leistungsreduzierung von 50 % empfohlen.

Reproduktion eines fehlerhaften Fehlers

Die Analyse von Geräten unter Bedingungen, die das Ausfallszenario im praktischen Einsatz nicht genau nachbilden, führt zu einer falschen Ermittlung der Ursache.

Übersehen von Verpackungsproblemen

Die Fokussierung beschränkt sich ausschließlich auf Probleme auf Chipebene, während gehäusebezogene Fehler wie Delamination, Bleikorrosion oder Lötstellenermüdung außer Acht gelassen werden.

Unzureichende Dokumentation

Die mangelnde Dokumentation der einzelnen Analyseschritte erschwert die Reproduktion der Ergebnisse und die Durchführung von Trendanalysen über mehrere Fehler hinweg.

Werkzeugkalibrierungsprobleme

Die Verwendung nicht kalibrierter Geräte führt zu ungenauen Messungen und falschen Schlussfolgerungen bei der Fehleranalyse.

Branchen-Fallstudien

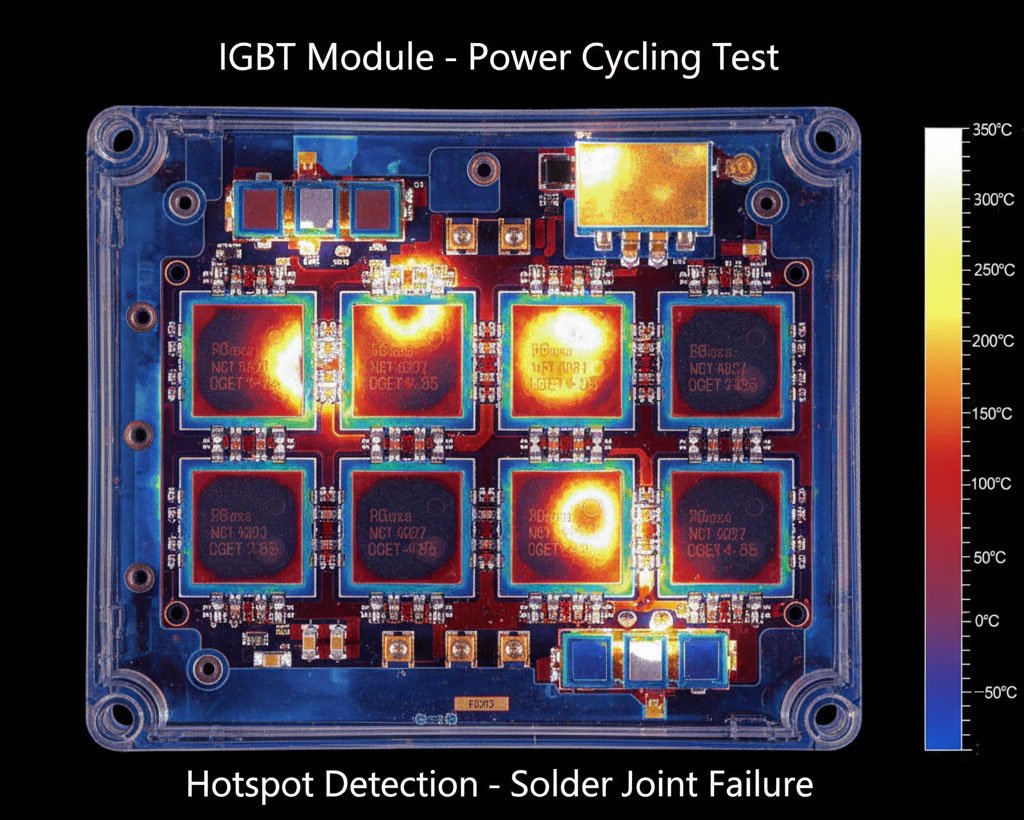

IGBT-Modulausfall in Elektrofahrzeugen

Symptom

Plötzlicher Stromausfall während des Ladevorgangs, ohne dass äußerlich sichtbare Schäden am Antriebsstrang des Elektrofahrzeugs erkennbar sind.

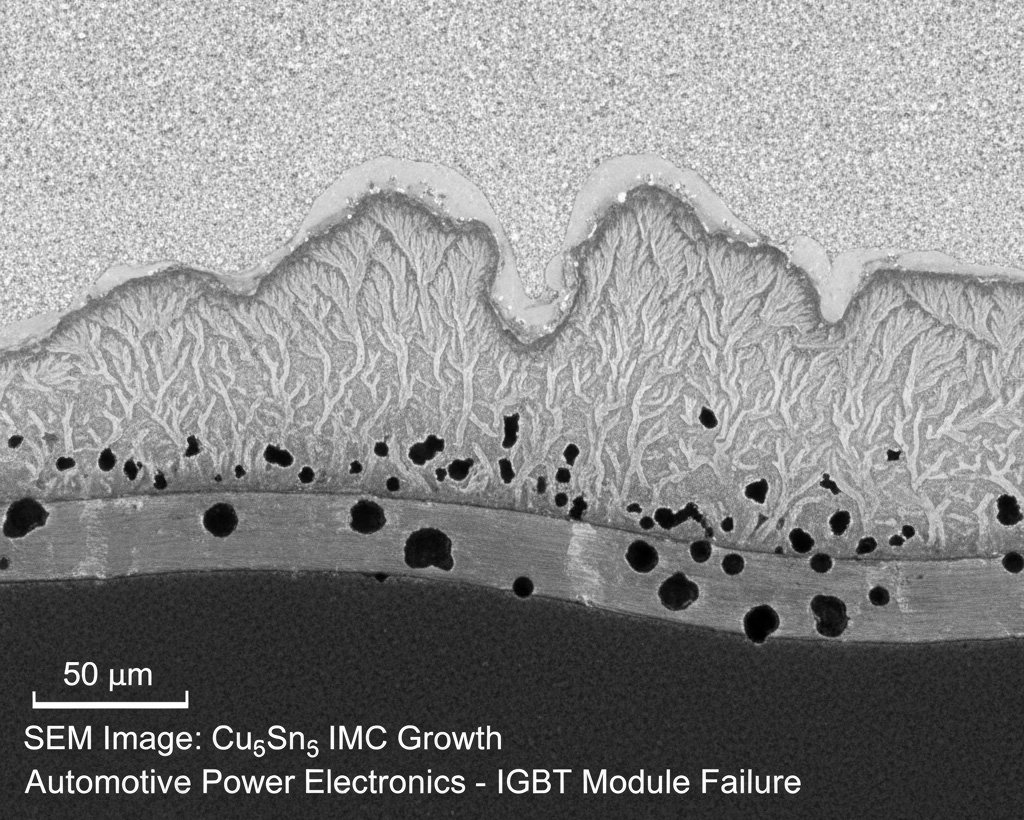

Analyseprozess

- Die Wärmebildgebung zeigte Hotspots im IGBT-Modul während des Ein- und Ausschaltens.

- Die SEM/EDS-Analyse identifizierte übermäßiges IMC-Wachstum (Cu₆Sn₅) in den Lötstellen.

- Die Querschnittsuntersuchung zeigte die Bildung von Kirkendall-Poren an der Löt-Substrat-Grenzfläche.

- Die FEA-Simulation brachte den Fehler mit einem unzureichenden Lötreflow-Profil in Zusammenhang.

Lösung & Ergebnis

Das Reflow-Profil wurde angepasst, um eine ordnungsgemäße Benetzung zu gewährleisten, und es wurden vernickelte Pads hinzugefügt, um das Wachstum intermetallischer Verbindungen zu kontrollieren.

Ergebnis: Die Ausfallrate im Feld wurde jährlich um 0,58 % gesenkt, wodurch 2 Millionen Dollar an Garantiekosten eingespart wurden.

Relevante Standards

Ergebnisse der Wärmebildanalyse

SEM-Bild von IMC-Wachstum

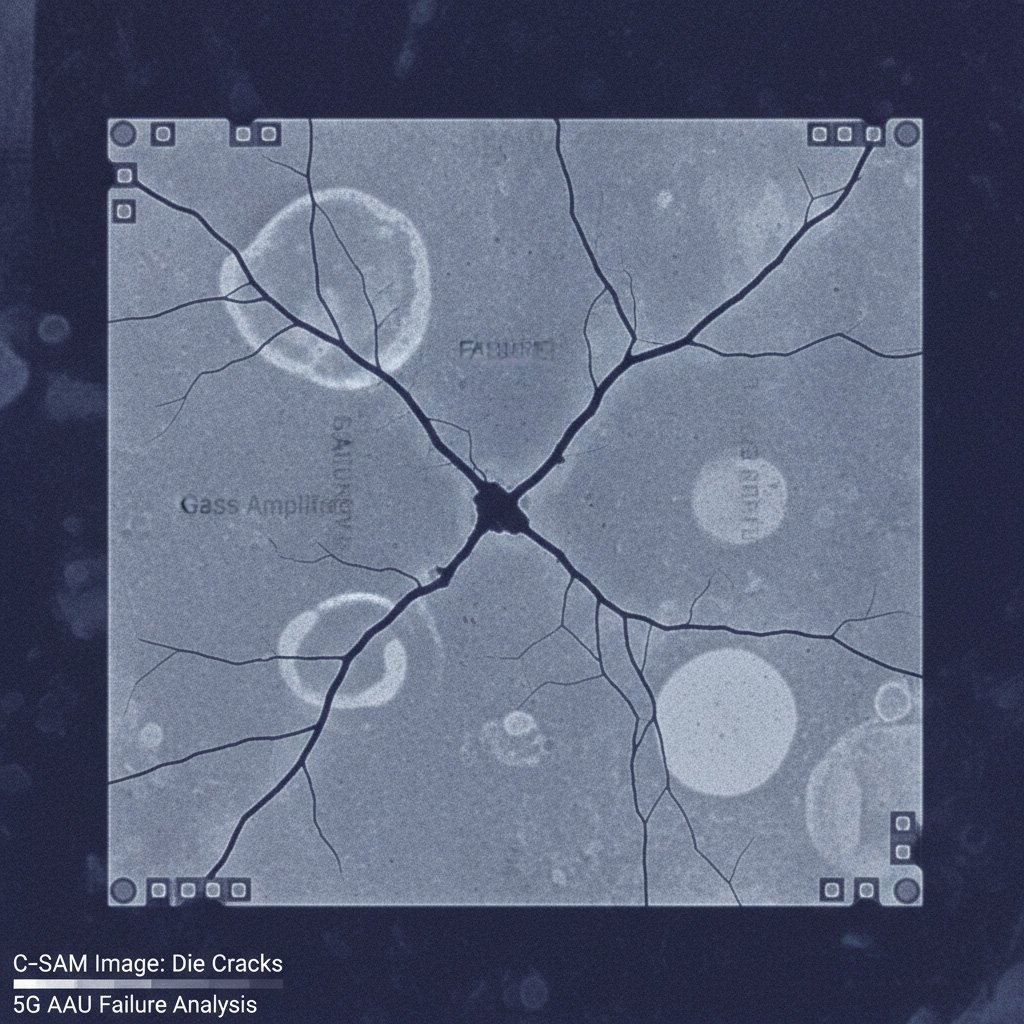

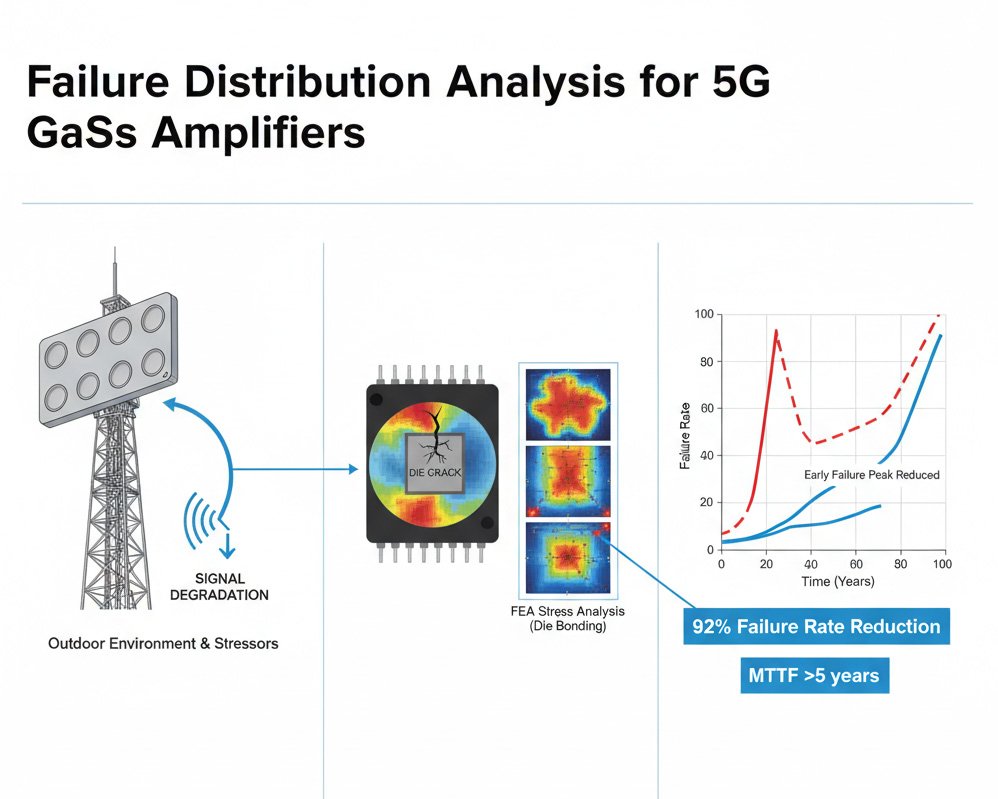

GaAs-Verstärkerausfall in 5G-AAUs

Symptom

Feldausfälle von 5G Active Antenna Units (AAUs) innerhalb von 6 Monaten nach der Inbetriebnahme, die zu einer Verschlechterung des Signals führen.

Analyseprozess

- C-SAM-Inspektion deckte Chiprisse in GaAs-Leistungsverstärkern auf.

- Bei einer Verpackungsprüfung wurden ungewöhnliche Auswerferspuren auf der Rückseite der Matrize festgestellt.

- Die Zuverlässigkeitsdatenanalyse zeigte, dass die Ausfallverteilung dem frühen Ausfallmodus entsprach.

- Die Finite-Elemente-Analyse bestätigte die mechanische Beanspruchung während des Chip-Bondings.

Lösung & Ergebnis

Modifizierte blaue Die-Bonding-Folie zur Reduzierung der mechanischen Spannung und Implementierung einer 100%igen Nachbond-Inspektion mittels automatisierter optischer Inspektion.

Ergebnis: Die Ausfallrate wurde um 92 % gesenkt, wodurch die mittlere Zeit zwischen Ausfällen auf über 5 Jahre verlängert wurde.

Relevante Standards

C-SAM-Bild von Die-Rissen

Fehlerverteilungsanalyse

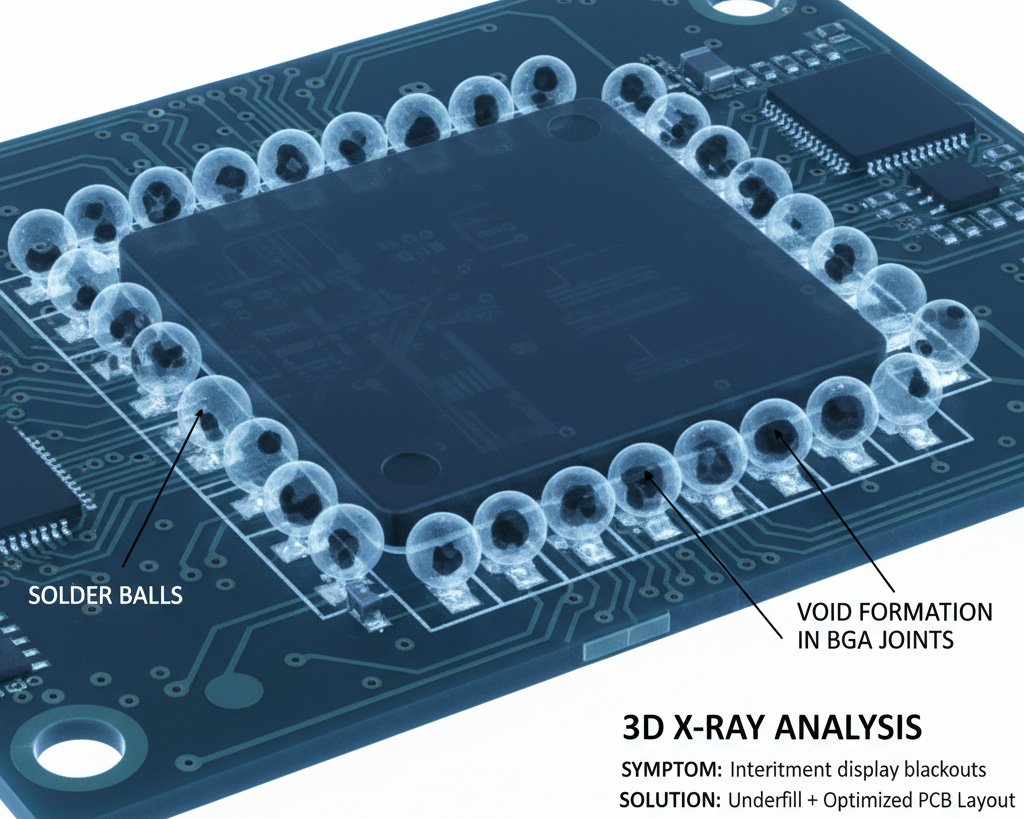

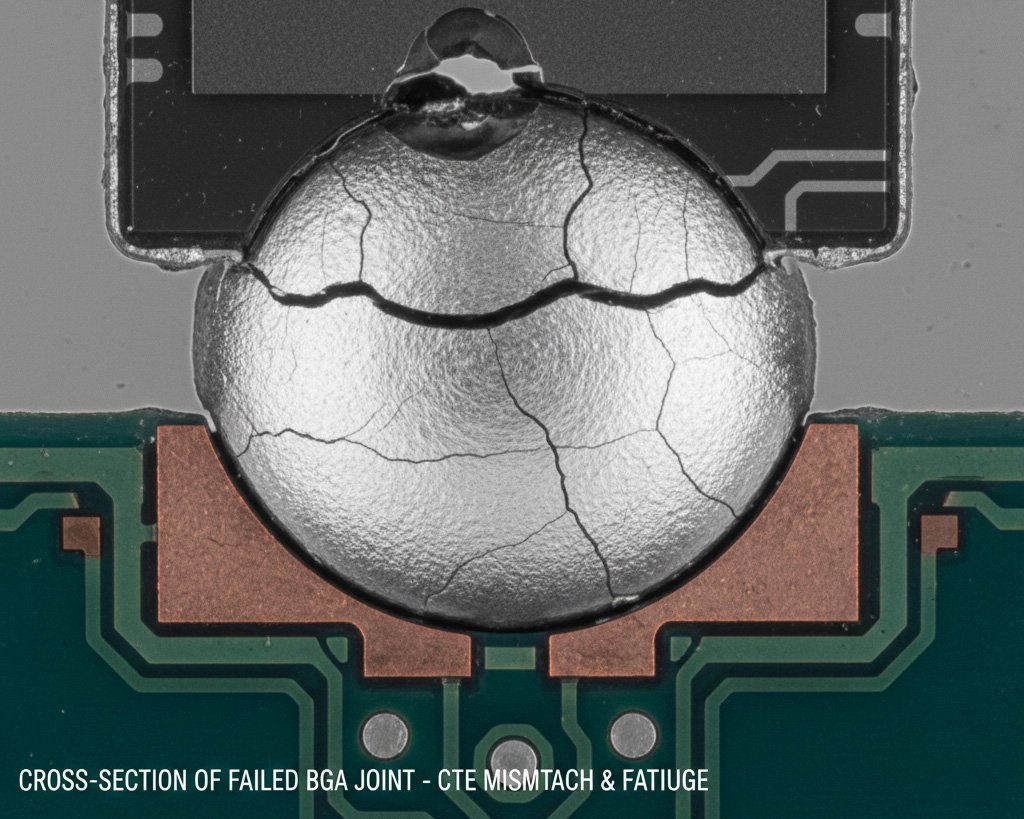

BGA-Fehler bei Smartphones

Symptom

Zeitweise auftretende Displayausfälle und nicht reagierender Touchscreen bei High-End-Smartphones nach 6-8 Monaten Nutzung.

Analyseprozess

- Durch thermische Zyklen (-40 °C bis 85 °C) konnte der Fehler unter Laborbedingungen reproduziert werden.

- SAM (Rasterakustische Mikroskopie) zeigte Ermüdungserscheinungen der Lötstellen.

- Querschnittsuntersuchungen bestätigten die Diskrepanz der Wärmeausdehnungskoeffizienten (CTE).

- Mittels 3D-Röntgenanalyse wurde die Hohlraumbildung in 18 % der BGA-Verbindungen quantifiziert.

Lösung & Ergebnis

Implementierte Underfill mit höherer Glasübergangstemperatur (Tg) und optimierte das PCB-Layout zur Reduzierung thermischer Gradienten.

Ergebnis: Die Rücklaufquote im Feld sank um 76 %, und nach 18 Monaten Nutzung wurden keine Ausfälle mehr gemeldet.

Relevante Standards

3D-Röntgenbild von Hohlräumen im BGA

Querschnitt der defekten Verbindung

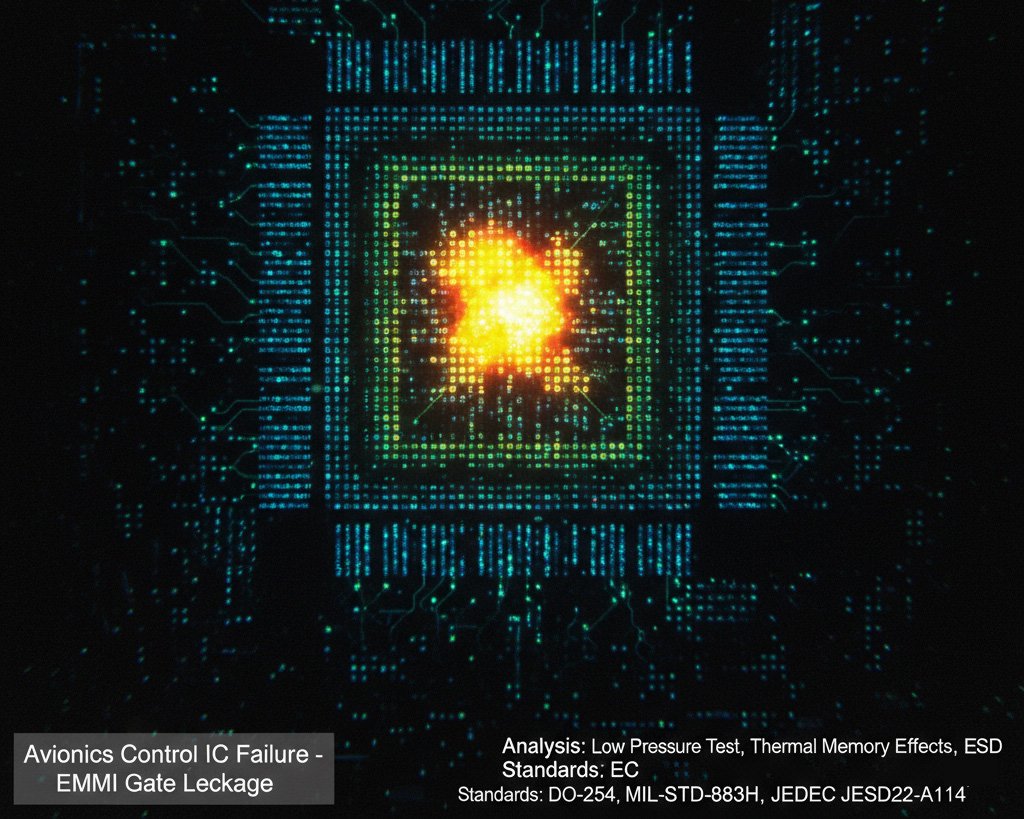

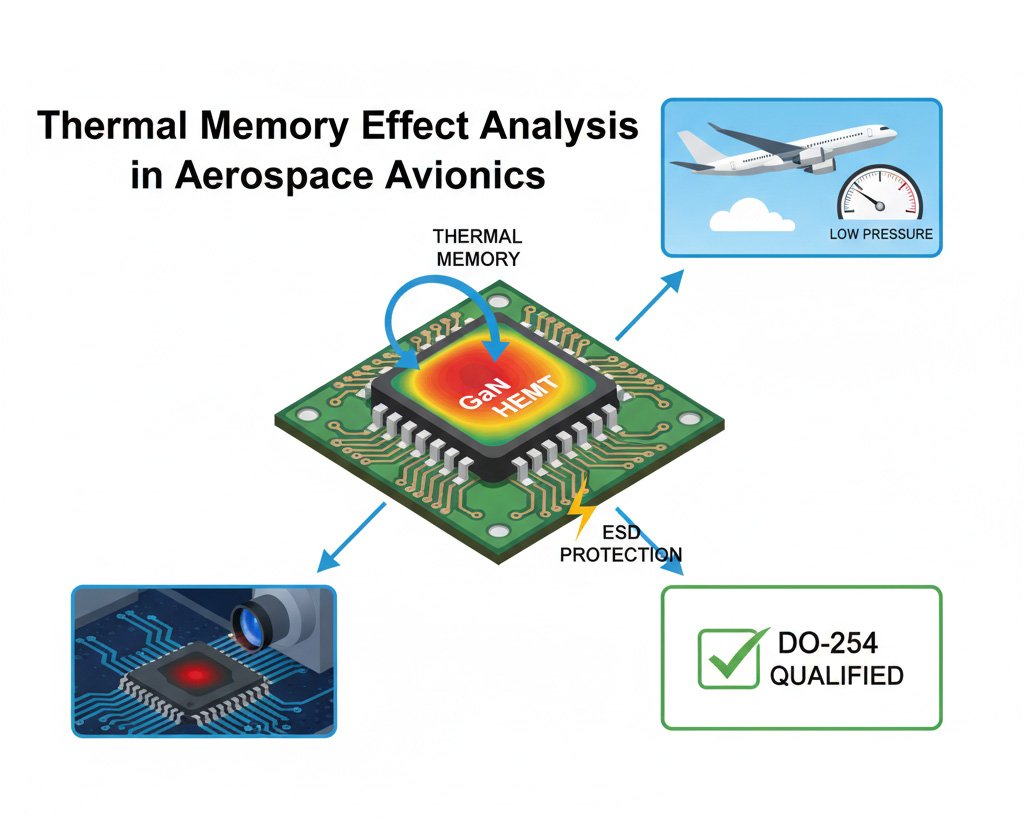

Ausfall des Avionik-Steuer-ICs

Symptom

Zufällige Systemneustarts in Avionik-Steuermodulen während des Höhenflugs, ohne erkennbares Muster.

Analyseprozess

- Umwelttests reproduzierten das Versagen unter Niedrigdruckbedingungen (große Höhe).

- EMMI hat einen intermittierenden Gate-Leckstrom im Power-Management-IC festgestellt.

- Mithilfe der IC-CAP-Modellierung wurden nicht modellierte thermische Speichereffekte in GaN-HEMTs identifiziert.

- ESD-Tests ergaben unzureichenden Schutz in der Eingangsschaltung.

Lösung & Ergebnis

Aktualisiertes ASM-HEMT-Modell mit Berücksichtigung von thermischen Memory-Effekten und verbesserter ESD-Schutzschaltung.

Ergebnis: Vollständige Eliminierung von Neustarts während des Fluges, erfolgreiche Qualifizierung gemäß DO-254-Standards.

Relevante Standards

EMMI-Bild der Gate-Leckage

Analyse des thermischen Memory-Effekts

Werkzeuge und Ausrüstung

| Werkzeug | Kernanwendungsfall | Auflösungsgrenze | Am besten geeignet für | Einschränkung |

|---|---|---|---|---|

| EMMI | Hotspot-Lokalisierung (Lecks, Ausfälle) | ~1 μm | CMOS/FinFETs | Kein Signal bei offenen Stromkreisen |

| C-SAM | Delaminierungs-/Hohlraumerkennung | 50 nm | Flip-Chip, BGA | Erfordert Flüssigkeitskupplung |

| 3D-Röntgen-CT | TSV/gestapelte Die-Inspektion | 100 nm | 3D-ICs | Hohe Kosten für hohe Auflösung |

| Lock-in-Thermografie | Thermische Kartierung im Sub-°C-Bereich | 0,1 °C | Leistungs-ICs (IGBTs) | Langsame Scanzeit |

| SEM/EDS | Materialcharakterisierung, Defektabbildung | 1-5 nm | Physikalische Analyse auf Chipebene | Erfordert leitfähige Beschichtung für Isolatoren |

| FIB-SEM | Querschnittsanalyse, Schaltungsbearbeitung | 5 nm | 3D-ICs, fortschrittliche Gehäuse | Destruktiv, zeitaufwändig |

Leitfaden zur Werkzeug-Technik-Zuordnung

Die Auswahl der richtigen Werkzeuge für spezifische Fehlerszenarien gewährleistet eine effiziente und genaue Ursachenanalyse:

ESD-Schadensanalyse

- Beginnen Sie mit EMMI, um Leckagestellen zu lokalisieren.

- Anschließend FIB-SEM zur nanometergenauen Abbildung der Schäden

- Verwenden Sie EDS, um die Kontamination an den Fehlerstellen zu überprüfen.

- Überprüfung durch elektrische Prüfung (IV-Kennlinienanalyse)

3D IC TSV Risse

- 3D-Röntgen-Computertomographie für zerstörungsfreie Prüfungen einsetzen

- Validierung mittels FIB-Querschnittsanalyse an kritischen Stellen

- Führen Sie SEM-Aufnahmen durch, um die Rissmorphologie zu charakterisieren.

- Finite-Elemente-Analyse anwenden, um die Spannungsursprünge zu bestimmen

thermisch bedingte Ausfälle

- Beginnen Sie mit der Lock-in-Thermografie zur thermischen Kartierung.

- Verwenden Sie C-SAM, um auf Delamination aufgrund von thermischer Belastung zu prüfen.

- Führen Sie Querschnittsuntersuchungen durch, um die Integrität der Lötverbindung zu prüfen.

- Validierung durch Temperaturwechseltests

Zeitweise Ausfälle

- Verwenden Sie eine Klimakammer, um die Ausfallbedingungen zu reproduzieren.

- OBIRCH für die dynamische Strompfadanalyse anwenden

- Setzen Sie bei Stresstests Wärmebildkameras ein.

- Bei Verdacht auf mechanische Belastung sollte dies durch Vibrationsprüfung überprüft werden.

Neue Werkzeuge und Technologien

KI-gestützte EMV

Maschinelle Lernalgorithmen, die automatisch zwischen normalen und abnormalen Photonenemissionsmustern unterscheiden und so die Analysezeit um bis zu 70 % reduzieren.

Quantenpunktmarkierung

Fluoreszierende Nanomarker, die Defektbereiche in Halbleitern hervorheben und so eine frühere Erkennung potenzieller Fehlerstellen ermöglichen.

Prädiktive FA-Plattformen

Integrierte Systeme, die Fertigungsdaten, Ausfallberichte aus dem Feld und KI kombinieren, um potenzielle Ausfallmechanismen vorherzusagen, bevor sie auftreten.

Normen und Konformität

JEDEC-Standards

JESD22-A121: ESD-Prüfung

Definiert Verfahren für die Prüfung der elektrostatischen Entladung von Modellen des menschlichen Körpers (HBM), Maschinenmodellen (MM) und geladenen Bauelementen (CDM).

JESD47: Stresstestmethoden für integrierte Schaltungen

Umfassender Standard, der verschiedene Belastungstests abdeckt, darunter Temperaturwechseltests, Spannungs-Temperatur-Tests, Elektromigrationstests und zeitabhängige dielektrische Durchschlagstests.

JESD22-A104: Temperaturzyklen

Spezifischer Standard für Temperaturwechseltests zur Bewertung der Bauteilzuverlässigkeit unter thermischer Belastung.

Branchenspezifische Standards

AEC-Q100: Automobil-ICs

Qualifikationsspezifikation für integrierte Schaltkreise, die in Automobilanwendungen eingesetzt werden, mit strengen Zuverlässigkeitsanforderungen.

DO-254: Luft- und Raumfahrt-Avionik

Leitfaden zur Qualitätssicherung im Design von luftgestützter elektronischer Hardware, einschließlich integrierter Schaltungen, die in flugkritischen Systemen verwendet werden.

Telcordia GR-468: Telekommunikation

Anforderungen an die Zuverlässigkeitssicherung von Halbleiterbauelementen, die in Telekommunikationsgeräten verwendet werden.

Zuverlässigkeitsdatenanalyse

Eine effektive Fehleranalyse erfordert die statistische Auswertung von Zuverlässigkeitsdaten, um die Ausfallverteilungen zu verstehen und die Produktlebensdauer vorherzusagen:

Ausfallverteilungen

- Logarithmische Normalverteilung: Häufig bei Halbleiterausfällen

- Weibull-Verteilung: Nützlich zur Analyse von frühen, zufälligen und verschleißbedingten Ausfällen

- Exponentialverteilung: Geeignet für Bereiche mit konstanter Ausfallrate

Wichtige Kennzahlen

- MTBF (Mittlere Zeit zwischen Ausfällen)

- Ausfallrate (λ) - typischerweise ausgedrückt in FITs (Ausfälle in der Zeit: 1 FIT = 1 Ausfall pro 10^9 Gerätestunden)

- Umrechnungsfaktoren für beschleunigte Lebensdauertests (ALT)

Beispiel für eine Ausfallratenanalyse

Zukunftstrends in der IC-Fehleranalyse

Fortschrittliche Prozessknoten (2 nm/1 nm)

Analyseherausforderungen auf atomarer Ebene, wobei Quanteneffekte zu bedeutenden Faktoren bei Ausfallmechanismen werden.

Wichtigste Herausforderungen

- • Quantentunnel-Effekte

- • Defekte der Stromversorgung auf der Rückseite

- • Kontaminationserkennung auf atomarer Ebene

Neue Lösungen

- • Kryogenes TEM zur Untersuchung auf atomarer Ebene

- • KI-gesteuerte Nanosondierungstechniken

- • Fortschrittliche Atomsonden-Tomographie

3D-IC & Heterogene Integration

Komplexe Ausfallmechanismen in gestapelten Chiparchitekturen erfordern neue zerstörungsfreie Analyseverfahren.

Wichtigste Herausforderungen

- • TSV-Cracking (Through-Silicon Via)

- • Unterfüllungsablösung in gestapelten Düsen

- • Probleme mit dem Wärmemanagement

Neue Lösungen

- • Fortschrittliche 3D-Röntgen-Computertomographie mit höherer Auflösung

- • Multimodale Bildgebungsverfahren

- • Testbarkeit im Design von 3D-ICs

KI und maschinelles Lernen

Automatisierte Fehlererkennung und -klassifizierung zur Bewältigung der zunehmenden Komplexität von integrierten Schaltungen.

Wichtigste Anwendungsbereiche

- • Automatisierte Fehlerklassifizierung in REM-Bildern

- • Vorhersage von Fehlern anhand von Fertigungsdaten

- • Anomalieerkennung in Wafer-Testdaten

Vorteile

- • 50-70% Reduzierung der Analysezeit

- • Verbesserte Genauigkeit bei der Ermittlung der Ursachen

- • Frühzeitige Ausfallvorhersage vor dem Feldeinsatz