Il y a peu, Intel a mis au point une technologie d'alimentation électrique arrière sur une puce de test au niveau produit, baptisée « Blue Sky Creek », afin de répondre aux exigences de performance de la prochaine génération d'ordinateurs. Intel a présenté les résultats de cette recherche dans deux articles publiés lors du symposium VLSI qui s'est tenu à Kyoto, au Japon, du 11 au 16 juin dernier. Plus d'informations

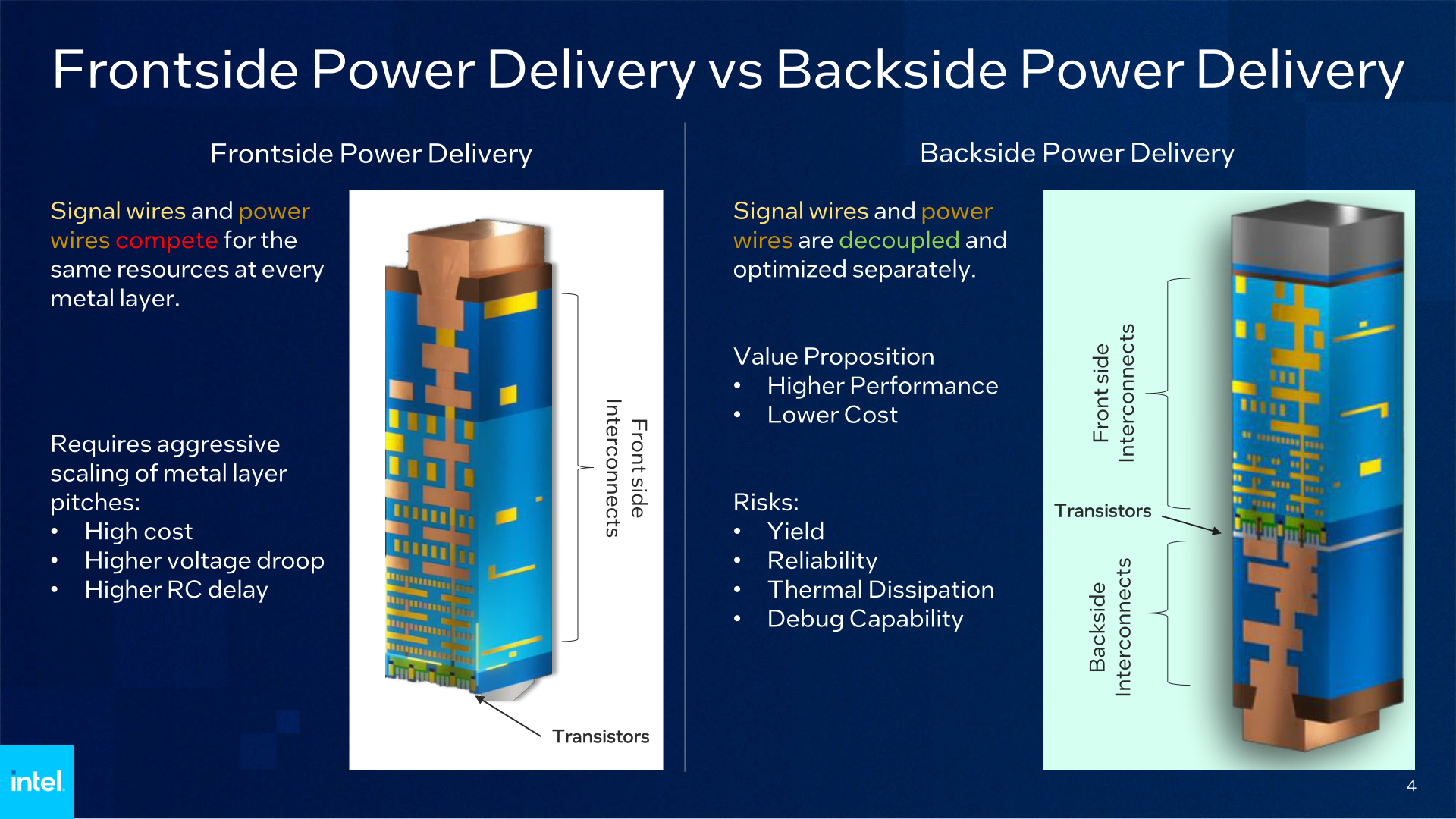

À mesure que les nœuds de processus continuent de progresser, la technologie traditionnelle d'alimentation électrique sur la face avant est confrontée à de nombreux défis. Les lignes de signal et d'alimentation étant situées sur la face avant de la plaquette, elles doivent partager, voire se disputer, les ressources de chaque couche métallique. Cela nécessite des efforts pour augmenter l'espacement entre les broches des couches métalliques, ce qui entraîne une augmentation des coûts et de la complexité. En réponse à cela, l'industrie a commencé à explorer la possibilité de déplacer la distribution d'énergie vers la face arrière. La technologie d'alimentation électrique arrière sépare les lignes de signal et d'alimentation, déplaçant ces dernières vers l'arrière de la plaquette, ce qui permet une optimisation individuelle. Cela se traduit par des performances plus élevées et des coûts réduits, mais pose également des défis en termes de rendement, de fiabilité, de dissipation thermique et de débogage.

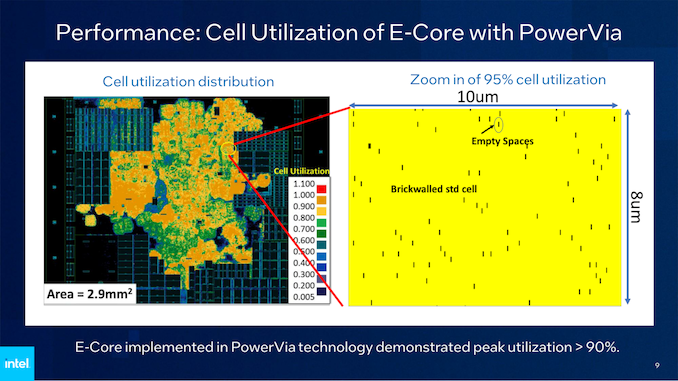

Selon certaines informations, les nœuds de processus Intel 20A et Intel 18A adopteront tous deux la technologie d'alimentation arrière PowerVia ainsi que la technologie de grille omnidirectionnelle RibbonFET. Pour relever ces défis et accélérer le développement, Intel a choisi de développer les technologies PowerVia et RibbonFET séparément, PowerVia étant la technologie phare. Les tests ont montré que la technologie PowerVia améliore considérablement l'efficacité des puces, avec des taux d'utilisation supérieurs à 90 % pour la plupart des zones de cellules standard. La taille des transistors est considérablement réduite, la densité unitaire est fortement augmentée et PowerVia atteint des indicateurs de rendement et de fiabilité élevés lors des tests, démontrant ainsi la valeur attendue de cette technologie. Les tests révèlent également que PowerVia réduit la tension de la plate-forme de 30 % et apporte un gain de fréquence de 6 %.

De plus, Intel a développé une technologie de dissipation thermique afin d'éviter les problèmes de surchauffe. L'équipe de débogage a également mis au point de nouvelles techniques pour résoudre divers problèmes qui surviennent lors du débogage de cette nouvelle structure de conception de transistor. Les puces de test PowerVia présentent des caractéristiques de dissipation thermique favorables, conformément aux attentes en matière d'augmentation de la densité de puissance grâce à la miniaturisation logique.

Ben Sell, vice-président du développement technologique chez Intel, a déclaré : « Intel poursuit activement son plan « Quatre ans, cinq nœuds de processus » et s'engage à intégrer un trillion de transistors dans un seul boîtier d'ici 2030. PowerVia représente une étape importante pour ces deux objectifs. En adoptant des nœuds de processus produits à titre expérimental et leurs puces de test, Intel a réduit le risque lié à l'application de l'alimentation électrique par la face arrière aux nœuds de processus avancés et commercialise désormais la technologie d'alimentation électrique par la face arrière. »

Il est entendu que dans un troisième article qui sera présenté prochainement au symposium VLSI, Mauro Kobrinsky, expert technique chez Intel, détaillera les résultats des recherches menées par Intel sur des méthodes de déploiement plus avancées pour PowerVia, telles que la transmission simultanée de signaux et l'alimentation électrique à la fois sur la face avant et arrière de la plaquette.