Nos últimos anos, a tecnologia de camada de redistribuição (RDL) ganhou força significativa. É uma solução revolucionária de embalagem que transformou a forma como embalamos os circuitos integrados.

Neste artigo, exploraremos a definição de RDL, sua função, benefícios, processo, aplicação e comparação com outras tecnologias de embalagem de ICs.

O que é a tecnologia de camada de redistribuição?

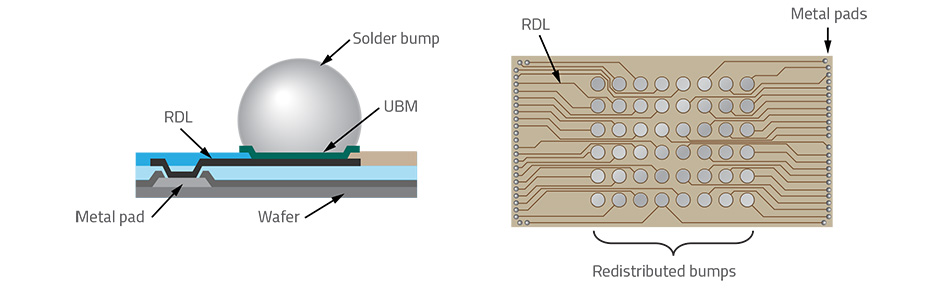

A camada de redistribuição, também conhecida como RDL, é uma camada de metal adicionada a um circuito integrado ou microchip para redistribuir as conexões elétricas. Essa tecnologia RDL é uma solução avançada de embalagem para circuitos integrados (ICs), que permite a integração de vários chips em um único pacote. É um processo de criação de uma camada metálica padronizada sobre a camada dielétrica, que redistribui a entrada/saída (I/O) do IC para um novo local. O novo local é normalmente na borda do die, o que permite que o IC seja conectado à placa de circuito impresso (PCB) usando a tecnologia de montagem em superfície padrão (SMT). A tecnologia RDL permite que o projetista coloque o die de maneira compacta e eficiente, reduzindo assim o espaço total ocupado pelo dispositivo.

A tecnologia RDL é crucial no desenvolvimento de dispositivos eletrônicos modernos, que estão se tornando cada vez mais compactos e complexos. Ela permite que os chips sejam menores, mais rápidos e mais eficientes. É normalmente utilizada na embalagem de dispositivos MEMS, sensores, dispositivos de energia, memória, microprocessadores e processadores gráficos.

Função da camada de redistribuição

A camada de redistribuição (RDL) desempenha um papel fundamental na extensão e interconexão do plano XY no projeto e fabricação de chips.

Redistribuir a conexão de E/S

Os pads de E/S (entrada/saída) são módulos de processamento de pinos de chip geralmente distribuídos na borda ou periferia do chip. Eles podem processar o sinal dos pinos do chip e enviar o sinal do chip para o pino após o processamento.

O RDL pode facilitar a redistribuição das conexões de E/S do chip para o pacote. O RDL conecta os pads de ligação no chip aos condutores ou esferas do pacote, o que permite uma montagem mais fácil e um melhor desempenho do IC.

Isso é naturalmente conveniente para o processo de fio de ligação, mas é um pouco desafiador para flip chips. Portanto, o RDL tornou-se a chave para este momento. Ele deposita uma camada de metal e uma camada dielétrica correspondente na superfície do chip, formando um fio de metal e redesenhando as portas IO para uma área nova e mais espaçosa, formando um layout de matriz de superfície.

Sinais de rota e energia

Além disso, o RDL também fornece um meio para rotear sinais e energia dentro do IC. O uso de RDLs tornou-se cada vez mais importante à medida que os ICs se tornaram mais complexos e exigiram mais conexões de E/S. Eles são usados em uma ampla gama de aplicações, como microprocessadores, chips de memória e sensores.

Benefícios da camada de redistribuição

A tecnologia RDL oferece vários benefícios para designers que buscam criar dispositivos eletrônicos de alto desempenho, compactos e econômicos. Alguns dos benefícios do uso da tecnologia RDL em pacotes de ICs são:

Pegada ecológica reduzida

A tecnologia RDL permite a integração de vários chips em um único pacote, reduzindo assim o espaço total ocupado pelo dispositivo. Isso permite que os projetistas criem dispositivos eletrônicos menores e mais compactos, o que é essencial para aplicações como smartphones, wearables e dispositivos IoT.

Desempenho elétrico aprimorado

A tecnologia RDL permite ao projetista posicionar o chip de maneira compacta e eficiente, o que reduz o comprimento das interconexões. Isso, por sua vez, reduz o atraso do sinal e melhora o desempenho elétrico do dispositivo. A tecnologia RDL também reduz a capacitância e a indutância parasíticas, o que melhora a integridade do sinal do dispositivo.

Custo reduzido

A tecnologia RDL elimina a necessidade de ligação por fio e ligação flip-chip, que são processos caros e demorados. A tecnologia RDL também reduz o número de componentes necessários para o dispositivo, o que reduz ainda mais o custo do dispositivo. A tecnologia RDL é uma solução econômica para a criação de ICs de alto desempenho que exigem um formato pequeno.

Tipos de tecnologia de camada de redistribuição

Existem dois tipos de tecnologia de camada de redistribuição (RDL): fan-in e fan-out. A tecnologia RDL fan-in é utilizada para encapsular um único chip, enquanto a tecnologia RDL fan-out é utilizada para encapsular vários chips.

Tecnologia Fan-in RDL

A tecnologia RDL fan-in é utilizada para encapsular um único chip. A tecnologia RDL fan-in também é conhecida como encapsulamento ao nível da pastilha (WLP), que é um processo de criação de um encapsulamento diretamente na pastilha. A tecnologia RDL fan-in é uma solução económica para a criação de encapsulamentos pequenos e finos.

A tecnologia fan-in RDL é adequada para aplicações como sensores, dispositivos MEMS, dispositivos RF, microprocessadores e dispositivos de memória.

Tecnologia Fan-out RDL

A tecnologia RDL fan-out é utilizada para encapsular múltiplos chips. A tecnologia RDL fan-out também é conhecida como wafer-level fan-out (WLFO), que é um processo de criação de um encapsulamento em um wafer reconstituído. A tecnologia RDL fan-out é uma solução econômica para a criação de encapsulamentos de alto desempenho com um formato pequeno.

A tecnologia RDL fan-out é adequada para aplicações como processadores gráficos, sistema em chip (SoC), dispositivos de memória, dispositivos de energia e dispositivos LED.

Processo da camada de redistribuição

A tecnologia RDL é um processo complexo que envolve várias etapas, como deposição dielétrica, deposição metálica, padronização e gravação. Abaixo está o fluxo do processo para Fan-in RDL e Fan-out RDL.

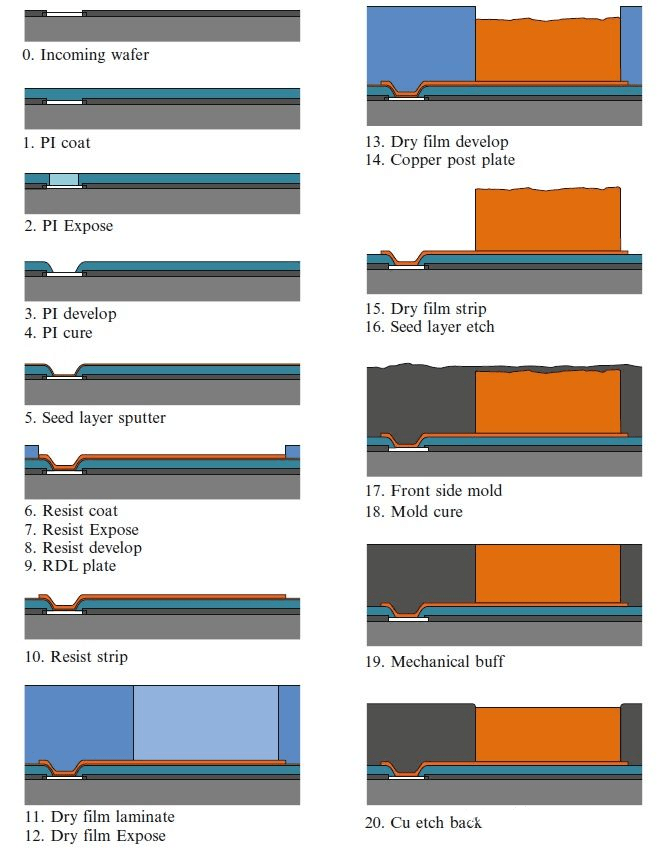

Processo Fan-in RDL

O processo Fan-in RDL é utilizado na produção de soluções avançadas de embalagem, tais como Wafer-Level Chip-Scale Packaging (WLCSP) e System-in-Package (SiP). Permite níveis mais elevados de integração, fatores de forma reduzidos e melhor desempenho para dispositivos semicondutores. O processo envolve várias etapas, conforme descrito abaixo:

O processo começa com uma pastilha recebida, que é então revestida com PI (isolante fotorresistente) na etapa 1. Em seguida, ocorre a exposição do PI na etapa 2, o desenvolvimento do PI na etapa 3 e a cura do PI na etapa 4.

Na etapa 5, uma camada de semente é pulverizada sobre o wafer, que é então revestido com resistência na etapa 6. A resistência é então exposta na etapa 7, revelada na etapa 8 e o RDL é revestido na etapa 9.

Depois disso, o resistente é removido na etapa 10 e um filme seco é laminado sobre o wafer na etapa 11. O filme seco é então exposto na etapa 12 e revelado na etapa 13. Em seguida, os postes de cobre são revestidos sobre o wafer na etapa 14 e o filme seco é removido na etapa 15.

Na etapa 16, a camada de semente é gravada e, na etapa 17, um molde frontal é criado. O molde é então curado na etapa 18 e o wafer é polido mecanicamente na etapa 19. Finalmente, na etapa 20, o excesso de cobre é gravado de volta, completando o fluxo do processo Fan-in RDL.

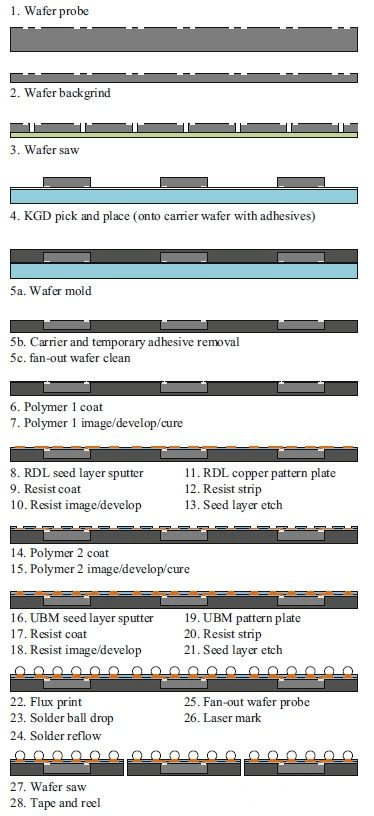

Processo RDL Fan-out

Semelhante ao processo Fan-in RDL, o processo Fan-out RDL também é uma forma de criar pacotes de chips menores e com melhor desempenho, com mais conexões. Aqui estão as etapas de fabricação:

1. Sonda de wafer: Este é o teste inicial do wafer para garantir que ele atenda às especificações exigidas antes de passar para as etapas de processamento subsequentes.

2. Retificação posterior do wafer: A parte posterior do wafer é retificada até atingir uma espessura específica para reduzir a espessura da embalagem.

3. Serra de wafer: O wafer é cortado em dies individuais.

4. KGD (Known Good Die) pick and place: Os chips bons são recolhidos e transferidos para um wafer transportador com adesivo.

5a. Molde do wafer: O wafer com os chips fixados ao wafer transportador é moldado com um material dielétrico para formar uma estrutura fan-out.

5b. Remoção do transportador e do adesivo temporário: O wafer transportador é removido do wafer fan-out, e qualquer adesivo temporário usado durante o processo também é removido.

5c. Limpeza da wafer fan-out: A wafer fan-out é limpa para remover quaisquer partículas ou impurezas remanescentes.

6. Camada de polímero 1: Uma camada de polímero é aplicada à superfície da wafer fan-out para atuar como uma camada dielétrica.

7. Imagem/revelação/cura do polímero 1: A camada de polímero é padronizada usando fotolitografia para criar a forma e o tamanho desejados da estrutura RDL.

8. Pulverização da camada de semente RDL: Uma fina camada de cobre ou outro material condutor é depositada sobre a camada de polímero usando pulverização.

9. Camada de resistência: Uma camada de material resistente é aplicada sobre a camada de semente.

10. Imagem/revelação do resistente: A camada resistente é padronizada usando fotolitografia para criar a forma e o tamanho desejados da estrutura RDL.

11. Placa de padrão de cobre RDL: O cobre é depositado sobre as áreas expostas da camada de semente usando galvanoplastia, criando o padrão RDL desejado.

12. Remoção do resistente: O material resistente restante é removido, deixando apenas o padrão RDL de cobre.

13. Gravação da camada de semente: A parte desnecessária da camada de semente é removida usando gravação.

14. Revestimento de polímero 2: outra camada de polímero é aplicada sobre a estrutura RDL para atuar como uma camada dielétrica.

15. Imagem/revelação/cura do polímero 2: A camada de polímero é padronizada usando fotolitografia para criar a forma e o tamanho desejados da estrutura UBM.

16. Pulverização da camada de semente UBM: Uma fina camada de cobre ou outro material condutor é depositada sobre a camada de polímero usando pulverização.

17. Camada de resistência: Uma camada de material resistente é aplicada sobre a camada de semente.

18. Imagem/revelação do resistente: A camada resistente é padronizada usando fotolitografia para criar a forma e o tamanho desejados da estrutura UBM.

19. Placa de padrão UBM: O cobre é depositado sobre as áreas expostas da camada de semente usando galvanoplastia, criando o padrão UBM desejado.

20. Remoção do resistente: O material resistente restante é removido, deixando apenas o padrão UBM de cobre.

21. Gravação da camada de semente: A parte desnecessária da camada de semente é removida por meio de gravação.

22. Impressão de fluxo: Um material de fluxo é aplicado às almofadas UBM.

23. Colocação de esferas de solda: As esferas de solda são colocadas nas almofadas UBM.

24. Refluxo de solda: As esferas de solda são aquecidas para derreter e formar conexões entre as almofadas UBM e os condutores externos ou saliências.

25. Sonda de wafer fan-out: O IC embalado é testado para garantir que atende às especificações exigidas.

26. Marcação a laser: Um identificador único ou código de barras é gravado na superfície do IC usando um laser.

27. Serra de wafer: O wafer fan-out é cortado em pacotes individuais.

28. Fita e bobina: Os ICs embalados individualmente são montados em uma bobina para facilitar o manuseio e o transporte.

Aplicar RDL à embalagem avançada

Em embalagens avançadas, como pacotes de nível de wafer fan-in (FIWLP) e pacotes de nível de wafer fan-out (FOWLP), o RDL é a tecnologia mais crítica. Foi o surgimento dessa tecnologia que permitiu que as fábricas de embalagens competissem com as fundições de wafer na tecnologia de embalagem fan-out. Por meio do RDL, o IOPad pode ser transformado em diferentes tipos de pacotes de nível de wafer em FIWLP ou FOWLP. No FIWLP, os bumps são todos crescidos no die, e a conexão entre o die e o pad depende principalmente da linha metálica do RDL. Após a embalagem, o IC tem quase o mesmo tamanho que a área do die. No FOWLP, os bumps podem crescer fora do die, e o IC após a embalagem é maior que a área do die (1,2 vezes).

Em particular, na embalagem avançada 2.5D, além do TSV no substrato de silício, o RDL também é indispensável. Tomando como exemplo o InFO da TSMC, um representante da embalagem avançada 2.5D, o InFO usa um ou mais chips nus no transportador, que são então incorporados na wafer reconstituída do composto de moldagem. Em seguida, as interconexões RDL e as camadas dielétricas são fabricadas na wafer, que é um fluxo de processo "chip first". O InFO de matriz única fornece altas contagens de saliências, e as linhas RDL se estendem da área do chip para fora, formando uma topologia "fan-out".

Qual tecnologia de camada de redistribuição devo usar?

Como mencionamos anteriormente, existem duas tecnologias RDL: Fan-in RDL e Fan-out RDL. Então, como escolher a tecnologia certa para criar dispositivos eletrônicos de alto desempenho, compactos e econômicos? Isso depende de vários fatores, como o tipo de aplicação, o número de dies e os requisitos de desempenho.

Aplicação

A tecnologia RDL fan-in é adequada para aplicações como sensores, dispositivos MEMS e dispositivos RF. A tecnologia RDL fan-out é adequada para aplicações como processadores gráficos, sistemas em chip (SoC) e dispositivos de memória.

Número de matrizes

A tecnologia RDL fan-in é adequada para o encapsulamento de um único die, enquanto a tecnologia RDL fan-out é adequada para o encapsulamento de múltiplos dies.

Requisitos de desempenho

A tecnologia RDL fan-in é adequada para a criação de pacotes pequenos e finos, enquanto a tecnologia RDL fan-out é adequada para a criação de pacotes de alto desempenho com um formato pequeno.

Comparação da RDL com outras tecnologias de embalagem de circuitos integrados

Devido aos diferentes processos, existem várias tecnologias de embalagem disponíveis para circuitos integrados. Mais informações sobre as diferenças entre elas podem ser encontradas na tabela abaixo:

| IC Packaging | Description | Advantages | Disadvantages | Applications |

|---|---|---|---|---|

| Wire Bonding | Connecting the IC to the PCB using wires | Low cost, flexible, proven technology | Limited performance, not suitable for high-frequency and high-power applications | Consumer electronics, automotive, medical devices |

| Flip-Chip Bonding | Chips are bonded face-down to the substrate, Connecting the IC to the PCB using solder bumps | High performance, high-density, low inductance | Expensive, requires precise alignment and underfilling | High-speed data communication, high-power applications, microprocessors |

| Through-Silicon Via (TSV) | Creating vertical interconnects through the silicon substrate | Shorter interconnect lengths, higher performance, smaller form factor | Complex and expensive manufacturing process, thermal and mechanical stress issues | Memory devices, image sensors, 3D ICs |

| Chip-scale package (CSP) | Replacing the lead frame with a substrate | Small form factor, high density, low cost | Limited I/O, susceptibility to mechanical and thermal stress | Mobile devices, wearable technology |

| Integrated Fan-out (InFO) | Integrated package of multiple chips and the soldering point of the pin is outside of the chip | High density, small form factor, low power consumption | Complex manufacturing process, high cost | Mobile devices, IoT, wearable technology |

| High Bandwidth Memory (HBM) | 3D stacking technology | High bandwidth, low power consumption | Expensive, limited scalability | High-performance computing, graphics processing |

| Chip on Wafer on Substrate (CoWoS) | Integrate chip and silicon wafer (substrate) together | High bandwidth, low power consumption, heterogeneous integration | Complex manufacturing process, high cost | High-performance computing, graphics processing |

| Redistribution Layer (RDL) | Creating a patterned metal layer on top of the dielectric layer | High density, fine pitch, low profile | Limited power handling capability, susceptibility to mechanical and thermal stress | Mobile devices, consumer electronics |

| Bump Technology | Depositing small metal bumps on the chip | Low cost, simple manufacturing process, flexible design | Limited performance, not suitable for high-speed and high-power applications | Consumer electronics, automotive, medical devices |

Empresas que oferecem soluções tecnológicas de camada de redistribuição

Existem várias empresas que oferecem soluções tecnológicas de camada de redistribuição (RDL), tais como:

Grupo ASE

O ASE Group é um fornecedor global de serviços de fabricação de semicondutores. O ASE Group oferece uma ampla gama de soluções de tecnologia RDL para várias aplicações, como memória, microprocessadores e processadores gráficos.

Amkor Technology

A Amkor Technology é um fornecedor global de serviços de embalagem e teste de semicondutores. A Amkor Technology oferece uma ampla gama de soluções de tecnologia RDL para várias aplicações, tais como sensores, dispositivos MEMS e dispositivos de energia.

Taiwan Semiconductor Manufacturing Company

A TSMC é uma fundição global de semicondutores que oferece uma ampla gama de soluções de tecnologia RDL para várias aplicações, tais como sistemas em chip (SoC), dispositivos de memória e dispositivos de alimentação.

Conclusão

A tecnologia de camada de redistribuição (RDL) é uma solução revolucionária de embalagem que transformou a forma como embalamos circuitos integrados (ICs). Ela permite que mais conexões sejam feitas em um único chip, reduzindo assim o espaço total ocupado pelo dispositivo. Por isso, é utilizada em várias aplicações, como smartphones, dispositivos vestíveis e dispositivos IoT. O futuro da tecnologia RDL em embalagens de ICs é promissor, e espera-se que tenha um impacto significativo na indústria eletrônica nos próximos anos.