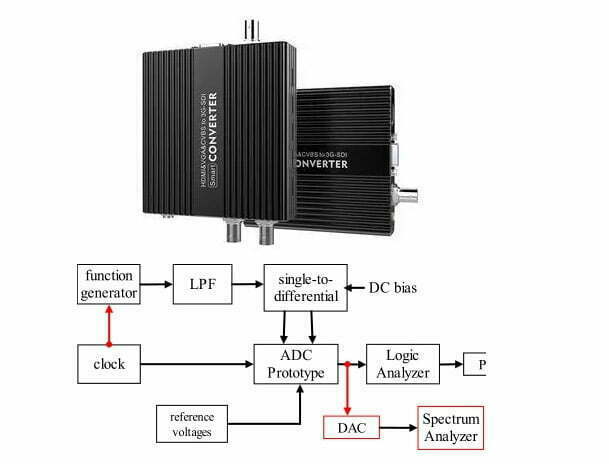

Entre los instrumentos inteligentes, los convertidores ADC y DAC desempeñan un papel fundamental. Sabemos que los microprocesadores que se utilizan actualmente solo pueden procesar señales digitales discretas. No hay forma de introducir una señal analógica continua del mundo físico en un microprocesador sin un ADC. Además, sin un DAC, no hay forma de emitir una señal analógica desde un microprocesador. (Haga clic aquí para obtener más información sobre las señales digitales y analógicas).

Convertidor analógico-digital (ADC)

Definición de ADC

En el sistema de instrumentación, a menudo es necesario convertir las cantidades analógicas detectadas que cambian continuamente, como la temperatura, la presión, el caudal, la velocidad, la intensidad luminosa, etc., en cantidades digitales discretas antes de introducirlas en el ordenador para su procesamiento. Estas cantidades analógicas se convierten en señales eléctricas (normalmente señales de tensión) mediante sensores y, tras ser amplificadas por amplificadores, deben someterse a un determinado procesamiento para convertirse en cantidades digitales. Un dispositivo que convierte analógico a digital se denomina normalmente convertidor analógico-digital (ADC), o A/D para abreviar.

Principio de funcionamiento del ADC

En circunstancias normales, la conversión A/D suele pasar por cuatro procesos: muestreo, retención, cuantificación y codificación.

Muestreo y retención

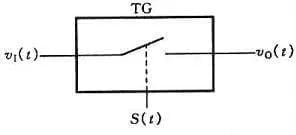

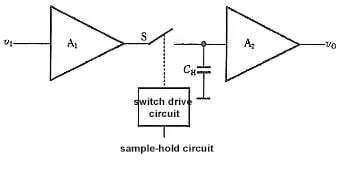

El muestreo consiste en convertir una cantidad analógica que cambia continuamente con el tiempo en una cantidad analógica discreta en el tiempo. El diagrama esquemático del proceso de muestreo se muestra en la figura 1. La figura (a) muestra la estructura de un circuito de muestreo, en el que la puerta de transmisión se controla mediante la señal de muestreo S(t). Durante el ancho de pulso τ de S(t), la puerta de transmisión se activa, la señal de salida vO(t) es la señal de entrada v1 y, durante (Ts-τ), la puerta de transmisión se cierra y la señal de salida vO(t)=0. Las formas de onda de la señal en el circuito se muestran en la figura (b).

Del análisis se desprende que cuanto mayor es la frecuencia de la señal de muestreo S(t), más fielmente reproduce la señal obtenida la señal de entrada tras pasar por el filtro de paso bajo. Pero el problema es que aumenta la cantidad de datos. Para garantizar una frecuencia de muestreo adecuada, debe satisfacerse el teorema del muestreo.

Teorema de muestreo: supongamos que la frecuencia de la señal de muestreo S(t) es fs y que la frecuencia del componente de frecuencia más alta de la señal analógica de entrada v1(t) es fimax, entonces fs y fimax deben satisfacer la siguiente relación: fs≥2fimax, y en ingeniería se suele tomar fs> (3~5) fimax.

Se necesita un cierto tiempo para convertir la señal analógica obtenida por el circuito de muestreo en una señal digital cada vez. Para proporcionar un valor estable para el proceso posterior de cuantificación y codificación, la señal analógica obtenida cada vez debe ser retenida durante un periodo de tiempo por el circuito de retención.

El proceso de muestreo y retención se completa a menudo de forma simultánea a través del circuito de muestreo y retención. El diagrama esquemático y la forma de onda de salida del circuito de muestreo y retención se muestran en la figura 2.

El circuito está compuesto por el amplificador de entrada A1, el amplificador de salida A2, el condensador de retención CH y el circuito de accionamiento del interruptor. A1 debe tener una alta impedancia de entrada en el circuito para reducir la influencia en la fuente de la señal de entrada. Para dificultar la descarga de la carga almacenada en CH durante la fase de retención, A2 también debe tener una alta impedancia de entrada, así como una baja impedancia de salida, lo que puede mejorar la capacidad de carga del circuito. Por lo general, también se requiere que AV1·AV2=1 en el circuito.

Ahora, junto con la figura 2, analicemos el principio de funcionamiento del circuito de muestreo y retención. En t=t0, el interruptor S está cerrado y el condensador se carga rápidamente. Dado que AV1 · AV2=1, v0=vI, el periodo de muestreo es durante el intervalo de tiempo de t0~t1. En el momento t=t1, S se desconecta. Si la impedancia de entrada de A2 es infinita y S es un interruptor ideal, se puede considerar que el condensador CH no tiene circuito de descarga y que el voltaje en ambos extremos permanece constante en v0. La sección plana de t1 a t2 en la figura 11.8.2(b) es la etapa de retención.

El circuito de muestreo y retención puede producirse mediante diversos tipos de circuitos integrados monolíticos. Por ejemplo, existen los AD585 y AD684 para tecnología bipolar; y los AD1154 y SHC76 para tecnología mixta.

Cuantización y codificación

Las señales digitales no solo son discretas en el tiempo, sino también discontinuas en amplitud. El tamaño de cualquier cantidad digital solo puede ser un múltiplo entero de una unidad de cantidad mínima especificada. Para convertir la señal analógica en una cantidad digital, en el proceso de conversión A/D, el voltaje de salida del circuito de muestreo y retención también debe normalizarse al nivel discreto correspondiente de una manera aproximada. Este proceso de conversión se denomina valor numérico. Cuantificación, denominada cuantificación. El valor cuantificado finalmente debe representarse mediante un código a través del proceso de codificación. El código obtenido tras la codificación es la cantidad digital emitida por el convertidor A/D.

La unidad de cantidad más pequeña tomada en el proceso de cuantificación se denomina unidad de cuantificación, representada por △. Es la cantidad analógica correspondiente a cuando el bit más bajo de la señal digital es 1, es decir, 1LSB.

En el proceso de cuantificación, dado que el voltaje de muestreo no es necesariamente divisible por △, es inevitable que se produzca un error antes y después de la cuantificación. Este error se denomina error de cuantificación y se representa con ε. El error de cuantificación es un error de principio, que no se puede eliminar. Cuantos más bits tenga el convertidor A/D, menor será la diferencia entre los niveles discretos y menor será el error de cuantificación.

A menudo se utilizan dos métodos de cuantificación aproximada en el proceso de cuantificación: la cuantificación por redondeo y la cuantificación por redondeo.

solo redondeando el método de cuantificación

Tomando como ejemplo el convertidor A/D de 3 bits, supongamos que la señal de entrada v1 oscila entre 0 y 8 V. Al utilizar el método de cuantificación por redondeo, tomamos △=1 V y descartamos la parte que no alcanza la unidad de cuantificación. Si el valor está entre 0 y 8 V, el voltaje analógico entre 1 V se considera 0△, representado por el número binario 000, y el voltaje analógico entre 1 V y 2 V se considera 1△, representado por el número binario 001… El error máximo de este método de cuantificación es △.

método de cuantificación por redondeo

Si se adopta el método de cuantificación por redondeo, se utiliza la unidad de cuantificación △=8 V/15, y la parte inferior a la mitad de la unidad de cuantificación se descartará durante el proceso de cuantificación, mientras que la parte igual o superior a la mitad de la unidad de cuantificación se tratará como una unidad de cuantificación. Trata el voltaje analógico entre 0 y 8 V/15 como 0△, representado por el binario 000, y el voltaje analógico entre 8 V/15 y 24 V/15 se considera como 1△, representado por el número binario 001, que significa «esperar».

Comparación

El error de cuantificación máximo │εmax│=1LSB en el método de cuantificación anterior con solo redondeo, y el método de cuantificación │εmax│=1LSB/2 en el método de cuantificación posterior con redondeo y redondeo, el error de cuantificación del último es menor que el del primero, por lo que es el convertidor A/D más utilizado.

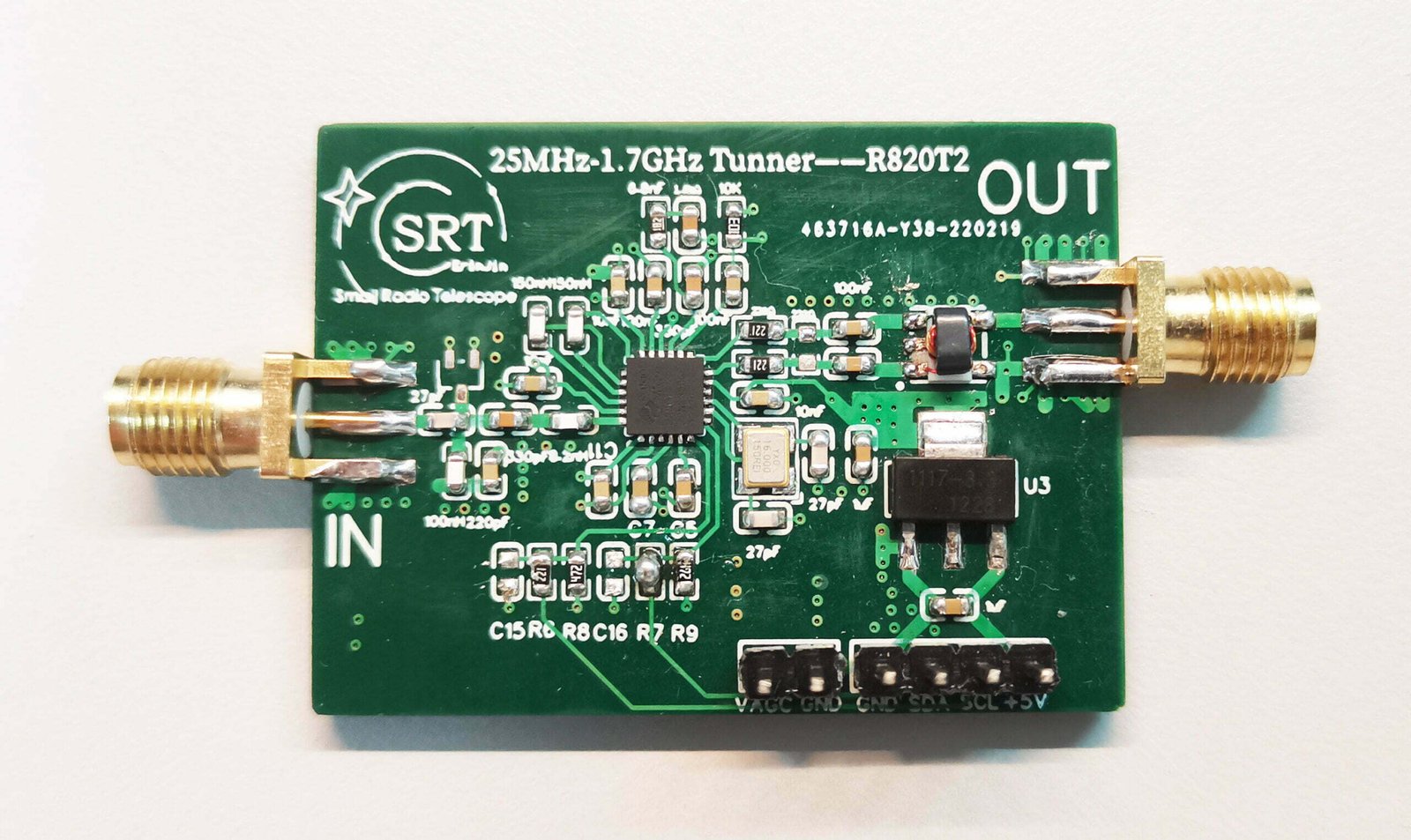

Con el rápido desarrollo de los circuitos integrados, surgen continuamente nuevas ideas de diseño y técnicas de fabricación para los convertidores A/D. Se diseñan convertidores A/D con diferentes estructuras y prestaciones para satisfacer diversas necesidades de detección y control.

Tipos de ADC

Integración de ADC

principio de conversión

El principio de conversión de la integración del ADC se basa en integrar el voltaje y comparar el voltaje integrado con otro voltaje para controlar el recuento, y la salida del recuento es la salida del ADC. El objeto de la integración se basa en el voltaje de referencia o en el voltaje de referencia y el voltaje de entrada.

Ventajas y desventajas

Ventajas:

- El ADC integral tiene una alta resolución y el número de dígitos puede ser de 12 o incluso superior.

- La linealidad es muy buena. Básicamente, la entrada se compara con un voltaje de referencia integrado para determinar la salida, por lo que la linealidad dependerá de la precisión del comparador.

- La topología de realización del circuito es sencilla y se utilizan relativamente pocos componentes para realizar estos dispositivos, por lo que el circuito es relativamente simple y el coste de producción es bajo.

Inconveniente:

- La principal desventaja es la lentitud de la velocidad de conversión. En los ADC de N bits, la salida puede tardar hasta 2 N ciclos de reloj en convertir un solo punto de muestra.

Aplicaciones

Se utiliza principalmente en aplicaciones y dispositivos con sensores, como voltímetros y amperímetros, en los que la precisión es más importante que la velocidad. En otras palabras, la velocidad de muestreo del ADC integral es relativamente baja, pero la precisión es muy alta.

clasificación

Existen diferentes tipos de ADC integrales, y los más comunes son los integrales de pendiente simple y doble. Añadir una «pendiente» aumenta la precisión a costa del tiempo de conversión.

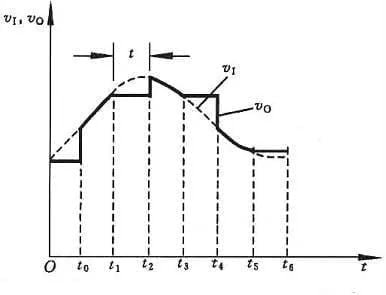

ADC integral de pendiente única

El comparador compara el voltaje de entrada con el valor del voltaje de referencia integrado (tenga en cuenta que lo haremos negativo, ya que está conectado a la entrada inversora del amplificador operacional). Cuente simultáneamente el número de ciclos de reloj. Cuando la salida del integrador es igual, el comparador emite un «0» lógico, lo que activa un reinicio del contador y del integrador, y el latch mantiene la salida digital.

VINVREFVrefVrefVin

Este es el tiempo de conversión. Sé por qué este ADC integral es lento. Veamos el peor de los casos, suponiendo que el voltaje de entrada es , suponiendo que es un ADC de 20 bits, entonces

VIN=VREFTCLK=1ustc=220us=1048576us

ADC integral de pendiente única

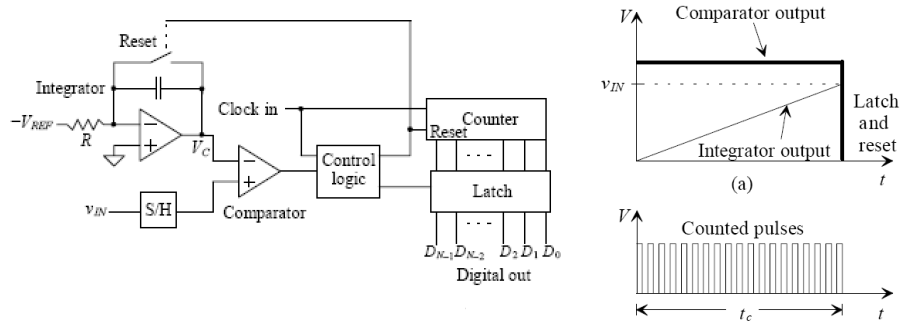

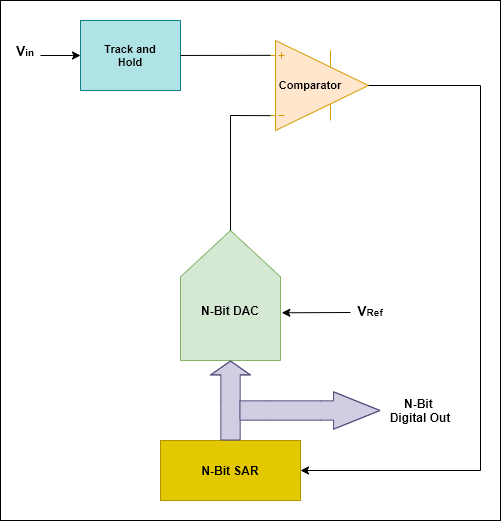

Un ADC de doble pendiente se diferencia de un ADC de pendiente única en que ahora se realiza la comparación con tierra y se integran dos sumas de voltajes. Inicialmente, la entrada negativa se conecta al integrador, que aumenta hasta que el contador se desborda. Dado que la integración en la entrada inversora cambia a un valor negativo, la salida del integrador siempre será positiva y mayor que cero, por lo que el contador seguirá funcionando hasta que se desborde, lo que lleva 2N ciclos de reloj (=T1).

VCVREFVINVC

En el momento T2, será igual a la suma de y, y

VC=VC1+VC2=0

Pero:

VIN/VREF=T2/T1

Por lo tanto, según el principio de conversión ADC, el ADC de doble pendiente es más lento que el ADC de pendiente única, ya que la integración se realiza dos veces, el error relacionado con la pendiente del integrador se cancela, lo que mejora la precisión en principio.

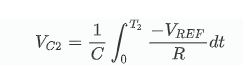

Sigma-Delta Σ-Δ ADC

A partir de la entrada, el amplificador diferencial produce una salida que es la diferencia entre Vin y la salida del DAC de 1 bit. La salida de un DAC de 1 bit puede ser uno de dos valores: OR . En esta topología, se puede considerar que un integrador toma una media móvil del valor anterior y el valor de entrada actual.

–Vref+Vref

Por lo tanto, suponiendo que el segmento positivo del comparador se fija inicialmente en un valor pequeño por encima de 0 V, el comparador se invierte. Su valor será alto o 1. Entonces, la salida del DAC será . En la siguiente iteración, este valor se restará del valor actual de . Dado que el valor anterior era 0 V, la salida del integrador será ahora – Vref. En este punto, la salida del comparador será 0 y la salida del DAC será.

+VrefVin-Vref

En la siguiente muestra , la salida del integrador será 0 debido al valor anterior, y el amplificador diferencial restará , sumándose así a . La salida del comparador será 1.

-Vref-Vref+VrefVin

Este proceso continúa de forma iterativa, por lo que, para una entrada de 0 V, la salida del comparador será una secuencia constante de 101010… Recuerde que la lógica 1 significa , la lógica 0 significa , por lo que si se muestrean y promedian N muestras, es fácil ver que el valor medio es 0 V. El bloque de procesamiento después del comparador simplemente emitirá esto como un valor único 0000…, suponiendo un valor de referencia de ( ~ ) o 2 x.

+Vref-Vref-Vref+VrefVref

Ahora, suponiendo 1 V, este es un ADC de 5 V. es ±2,5 V. Siguiendo los mismos pasos que antes de forma iterativa, la salida será: 1011101… La salida es 1,07 V.

Vin±Vref

En resumen:

Un ADC sigma-delta sobremuestrea la señal que se está procesando (véase Cómo funciona el muestreo analógico-digital para este concepto) y filtra con un filtro de paso bajo la señal que se va a procesar. Por lo general, el número de bits convertidos utilizando el ADC Flash después del filtro es inferior al número de bits requerido. La señal resultante, junto con los errores de los niveles discretos FLASH, se retroalimenta y se resta de la entrada y se envía al filtro. Esta retroalimentación negativa amortigua el ruido para que no aparezca en la frecuencia de señal deseada. Un filtro digital después del ADC (que utiliza un filtro de decimación) reduce la frecuencia de muestreo, filtra las señales de ruido no deseadas y aumenta la resolución de salida (de ahí el nombre de modulación sigma-delta, también conocida como modulación delta-sigma).

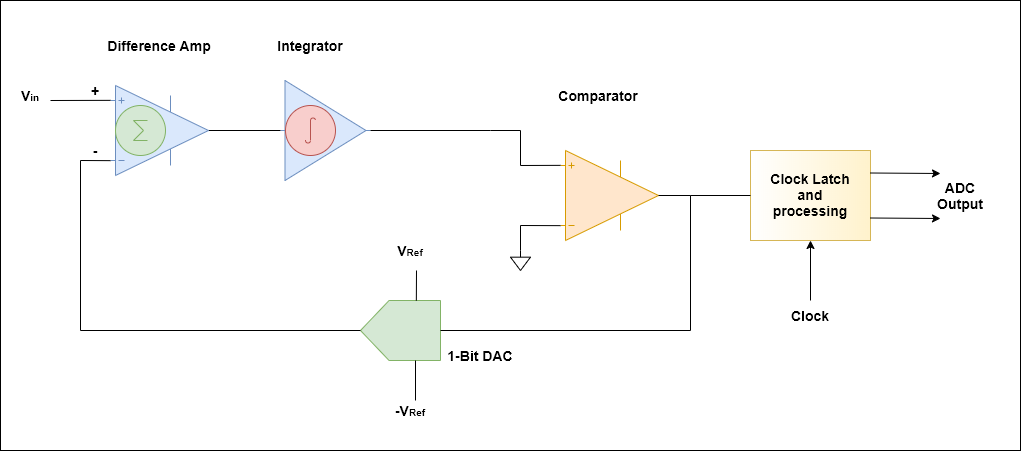

ADC flash (tipo de comparación directa)

El principio del ADC FLASH puede ser el más fácil de entender. La siguiente figura es un diagrama esquemático de un ADC de dos bits, que consta de muchos comparadores, cada uno de los cuales cuenta con un voltaje de referencia que es un bit más alto que el valor de referencia anterior. Por lo tanto, para un ADC de 8 bits, se necesitan 256 comparadores de este tipo. Para 10 bits, se necesitan 1024.

El LASH ADC (tipo de comparación directa) es rápido. Convierte directamente la entrada sin muestreo ni procesamiento posterior pesado. El problema es que requiere muchos comparadores, y muchos comparadores ocupan mucho espacio de silicio en el chip. Por lo tanto, utilice los Fash ADC solo cuando necesite velocidades extremadamente altas que no se pueden alcanzar con otras implementaciones de ADC.

La dicotomía encarnada en el hardware

En aplicaciones prácticas, existe otra variante que se utiliza con mayor frecuencia, el ADC semi-FLASH. Utiliza un proceso de dos pasos para reducir el número de convertidores necesarios en la cadena de conversión real:

En primer lugar, la señal de entrada se compara con el conjunto de niveles que se encuentran exactamente en la mitad . Si es inferior, el bit más significativo, MSB, se establece en 0 y la entrada se envía a una cadena de comparadores con el voltaje de referencia establecido para convertir el resto de los bits.

Si la señal de entrada está por encima, se establece el MSB en 1 y se resta de la señal de entrada. La cadena de comparadores se utiliza de nuevo para obtener los bits restantes. Así pues, en esencia, el ADC FLASH de medio paso sacrifica una comparación adicional para ahorrar la mitad del comparador. Este tipo de razonamiento también puede seguir deduciéndose y ampliándose, como el ADC FLASH de 4 puntos, etc.

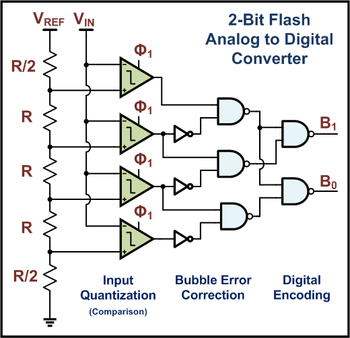

El registro de aproximación sucesiva (SAR)

El registro de aproximación sucesiva (SAR) es una parte integral del ADC de aproximación sucesiva. Funciona utilizando un comparador para reducir gradualmente el área que contiene el voltaje de entrada. Para ello, el convertidor contrasta el voltaje de entrada con la salida de un convertidor digital-analógico, que normalmente indica el centro del rango de voltaje elegido. Con cada paso del proceso, la estimación se almacena en el SAR.

Por ejemplo, supongamos que el voltaje de entrada es de 6,3 V y el rango inicial es de 0 a 16 V.

- En el primer paso, se introducen 6,3 V para compararlos con 8 V (el punto medio del rango de 0 a 16 V). El comparador informa de un voltaje de entrada inferior a 8 V, por lo que el SAR se actualiza para reducir el rango a 0-8 V.

- En el segundo paso, el voltaje de entrada se compara con 4 V (el punto medio de 0-8 V), el comparador informa de que el voltaje de entrada es superior a 4 V, por lo que el SAR se actualiza para reflejar que el voltaje de entrada está en el rango de 4-8 V.

- En el tercer paso, el voltaje de entrada se compara con 6 V (la mitad de 4 V a 8 V); el comparador informa de un voltaje de entrada superior a 6 voltios, y el rango de búsqueda pasa a ser de 6 a 8 voltios.

Continúe con estos pasos hasta alcanzar la solución deseada. Su topología es la siguiente:

Para entenderlo mejor, mira la siguiente animación:

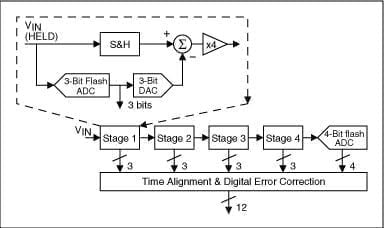

ADC en pipeline

Un ADC en pipeline (también conocido como cuantificador de subrutina) utiliza dos o más pipelines. En primer lugar, realiza una conversión aproximada. En el segundo paso, se utiliza un convertidor digital-analógico (DAC) para determinar la diferencia en la señal de entrada. A continuación, esta diferencia se convierte en valores más precisos y los resultados se combinan en un paso final. Esto puede considerarse una mejora con respecto a los ADC de aproximación sucesiva, en los que la señal de referencia de retroalimentación consiste en transiciones intermedias en todo el rango de bits (por ejemplo, 4 bits), en lugar de solo el siguiente bit más significativo. Al combinar las ventajas del método de aproximación sucesiva y el ADC flash, este tipo tiene las ventajas de alta velocidad, alta resolución y tamaño de molde pequeño.

En este esquema, la entrada analógica VIN se muestrea primero y se mantiene estable mediante un muestreador y mantenedor (S&H), mientras que el ADC flash en la primera etapa la cuantifica a tres bits. A continuación, la salida de 3 bits se envía a un DAC de 3 bits (con una precisión de 12 bits) y la salida analógica se resta de la entrada. Este «resto» se amplía por un factor de 4 y se envía a la siguiente etapa (etapa 2). Este resto añadido continúa a través de las etapas inferiores del canal, proporcionando 3 bits por etapa, hasta que llega al ADC flash de 4 bits, que resolverá los 4 bits LSB finales. Dado que los bits de cada etapa se determinan en diferentes momentos, todos los bits correspondientes a la misma muestra se alinean en el tiempo con el registro de desplazamiento antes de enviarse a la lógica de corrección de errores digital. Tenga en cuenta que cuando una canalización ha terminado de procesar las muestras de entrada, determinar el bit de adquisición para esta canalización y pasar el residuo a la siguiente canalización, puede comenzar a procesar la siguiente muestra recibida del soporte de muestras integrado en cada canalización. Esta canalización es la razón del alto rendimiento, que es también el concepto de canalización.

Otros

Además de los distintos ADC comunes mencionados anteriormente, también existen ADC basados en el principio de equilibrio de carga, ADC de tiempo compartido, ADC FM, ADC de estiramiento de tiempo, ADC de codificación incremental, ADC Wilkinson, etc.

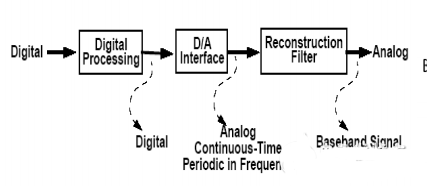

Convertidor digital-analógico (DAC)

Definición de DAC

La cantidad digital procesada por el sistema digital a veces debe convertirse en una cantidad analógica para su uso práctico. Esta conversión se denomina «conversión de digital a analógico». El circuito que realiza la conversión de digital a analógico se denomina convertidor de digital a analógico o DAC (Digital to Analog Converter) para abreviar.

Parámetros DAC

Resolución

La resolución en DAC se define como el número de todos los niveles analógicos de salida posibles bajo diferentes valores de código digital de entrada. Una resolución de N bits significa que el DAC puede generar 2 N −1 niveles analógicos diferentes. Generalmente, se refiere al número de dígitos del código digital de entrada.

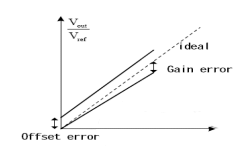

Errores de compensación y ganancia

El desplazamiento se define como el valor de la señal analógica de salida real cuando se introduce un valor de código 0, y el error de ganancia se define como la diferencia entre el valor de salida ideal a escala completa y el valor de salida real después de deducir el desplazamiento, como se muestra en la figura.

Precisión

La precisión en el DAC se divide en precisión absoluta y precisión relativa. La precisión absoluta se define como la diferencia entre la salida ideal y la salida real, incluyendo diversos errores de compensación y no lineales. La precisión relativa se define como el error no lineal integral máximo. La precisión se expresa como una relación de escala completa, expresada en dígitos efectivos. Por ejemplo, una precisión de 8 bits significa que el error del DAC es inferior a 1/8 2 de la salida a escala completa del DAC. Tenga en cuenta que el concepto de precisión no está relacionado con la resolución. Un DAC con una resolución de 12 bits puede tener solo una precisión de 10 bits, y un DAC con una resolución de 10 bits puede tener una precisión de 12 bits. La precisión por encima de la resolución significa que la respuesta de transmisión del DAC se puede controlar con mayor precisión.

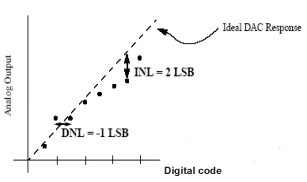

INL: No linealidad integral

Cuando se eliminan los errores de compensación y ganancia, el error de linealidad integral se define como la desviación de la característica de transferencia de salida real con respecto a la característica de transferencia ideal (una línea recta), tal y como se muestra en la imagen.

DNL: No linealidad diferencial

En un DAC ideal con un mínimo de 1 LSB por cambio de salida analógica, el error de linealidad diferencial se define como la desviación de 1 LSB por cambio mínimo de salida analógica (excluyendo el error de ganancia y el offset). El DNL que definimos es para cada valor de código de entrada digital y, a veces, se utiliza el DNL más grande para definir el DNL de todo el DAC. Un DAC ideal tendría un error de linealidad diferencial cero para cada entrada digital, mientras que un DAC con un DNL máximo de 0,5 LSB tendría un cambio de salida mínimo entre 0,5 LSB y 1,5 LSB por salida. Los errores de linealidad integral y diferencial del DAC se muestran en la figura.

Energía de fluctuación (área de impulso de fallo)

El área máxima bajo la fluctuación que aparece en la salida después de que cambia la señal de entrada.

Tiempo de asentamiento

El tiempo de estabilización se encuentra dentro de un rango de error específico del valor final y es el tiempo necesario para que la salida experimente una conversión a escala completa.

Monotonía Un DAC monótono es aquel en el que el nivel analógico de salida siempre aumenta a medida que aumenta el valor del código digital de entrada. Si el DNL máximo se controla dentro de 0,5 LSB, entonces la monotonía del DAC se puede garantizar de forma natural.

Rango dinámico libre de espurios (SFDR) SFDR es el rango dinámico libre de espurios, es decir, el rango dinámico sin ruido ni armónicos. Tanto el ruido como los armónicos se denominan señales espurias.

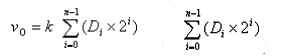

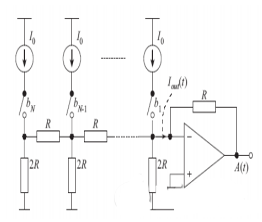

Principio del DAC

Convierta cada código binario de entrada en una cantidad analógica correspondiente según su peso y, a continuación, sume las cantidades analógicas que representan cada bit. La cantidad analógica total obtenida es proporcional a la cantidad digital, lo que permite realizar la conversión de cantidad digital a cantidad analógica. Conversión analógica.

Es el valor decimal convertido en un número binario mediante la expansión del peso de los bits.

Composición y características del DAC

El DAC se compone principalmente de registros digitales, interruptores electrónicos analógicos, red de peso de bits, amplificador operacional sumador y fuente de tensión de referencia (o fuente de corriente constante). Utiliza los dígitos de las cantidades digitales almacenadas en el registro digital para controlar los interruptores electrónicos analógicos de los dígitos correspondientes, de modo que el dígito con un valor de 1 genere un valor de corriente proporcional a su peso en la red de pesos de dígitos, y luego el amplificador operacional controla cada valor de corriente sumado y convertido a un valor de voltaje.

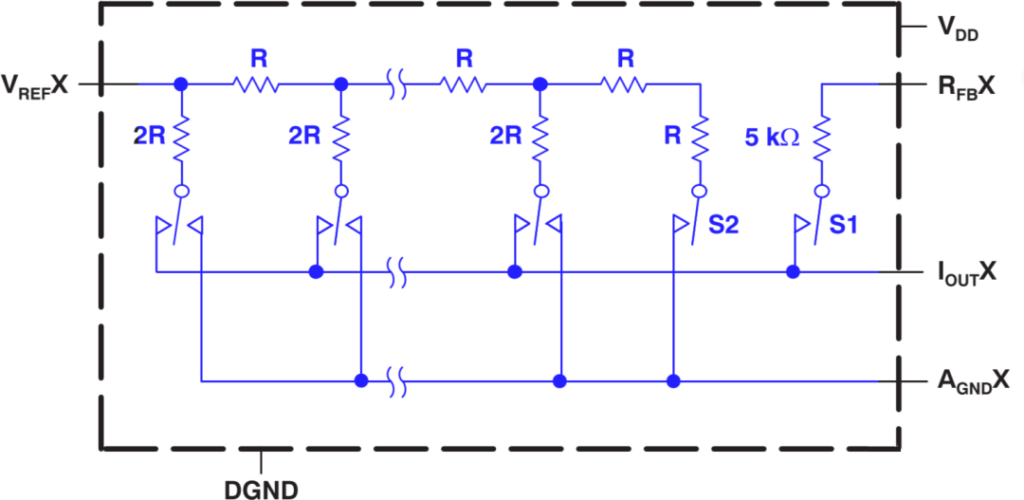

Las redes de peso de bits variables permiten el montaje de múltiples tipos de DAC, incluyendo el DAC de red de resistencia ponderada, el DAC de red de resistencia en forma de T invertida R-2R y el DAC de red de tipo corriente de valor único, etc. La precisión de la conversión producida por el DAC de red de resistencias ponderadas depende de la precisión de la tensión de referencia VREF, así como de la calidad de los interruptores electrónicos analógicos, los amplificadores operacionales y los valores de las resistencias ponderadas. Su desventaja es que los valores de resistencia de cada resistencia ponderada son diferentes y, cuando hay muchos dígitos, los valores de resistencia varían mucho, lo que dificulta enormemente garantizar la precisión, especialmente para la producción de circuitos integrados. Por lo tanto, en el DAC integrado, este circuito rara vez se utiliza solo.

Principales indicadores técnicos del CAD

Precisión y velocidad de conversión del DAC: La precisión de conversión se describe generalmente mediante la resolución y el error de conversión en el DAC.

Resolución

Por lo general, el número de bits del DAC se utiliza para medir la resolución, ya que cuanto mayor es el número de bits, mayor es el número de valores (2n) del voltaje de salida vO y mayor es la capacidad de reflejar los cambios sutiles del voltaje de salida.

Además, la resolución también se puede definir por la relación entre el voltaje de salida mínimo 1 LSB que el DAC puede distinguir y el voltaje de salida máximo FSR. Es decir:

resolución = 1 LSB/FSR = k/k(2n-1) = 1/(2n-1)

Cuanto menor sea el valor, mayor será la resolución.

Error de conversión

El error de conversión es la desviación máxima entre el voltaje analógico de salida real y el valor ideal. Se expresa comúnmente como un porcentaje o varios LSB de la relación entre esta desviación máxima y el FSR. De hecho, es un indicador global de los tres errores.

Velocidad de conversión

La velocidad de conversión viene determinada generalmente por el tiempo de estabilización. Desde el momento en que la entrada cambia de todos los 0 a todos los 1, hasta que el voltaje de salida se estabiliza dentro del rango de FSR±½ LSB (o el rango especificado por FSR±x%FSR), este periodo se denomina tiempo de estabilización, que es la respuesta máxima del DAC Time, por lo que se utiliza para medir la velocidad de conversión.

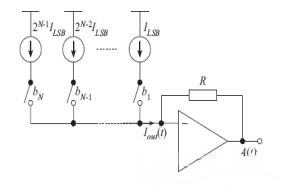

Tipos de DAC

Tipo de resistencia

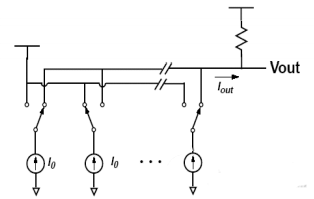

La estructura se muestra en la figura 1. Lo que muestra la figura 1 es un convertidor de tipo red escalonada R-2R. Su ventaja es que puede alcanzar una linealidad muy buena. Dado que todas las fuentes de corriente son equivalentes, podemos utilizar tecnología adicional especial para reducir el error entre ellas, y su estructura es mucho más simple que la del divisor de resistencia. La desventaja es que la resistencia siempre es no lineal y también contiene capacitancia parásita relacionada con la señal, por lo que es difícil lograr una adaptación completa. Al mismo tiempo, la velocidad está limitada por el búfer de salida y no puede ser muy alta.

Tipo capacitivo

La estructura se muestra en la figura 2. La capacitancia de orden más alto CN es 1 2N− veces mayor que la capacitancia de orden más bajo C1. La ventaja es que el consumo de energía es pequeño y la precisión de adaptación es mayor que la de la resistencia. Los principales factores limitantes son el desajuste de los condensadores, la resistencia en estado activo de los interruptores, los grandes retrasos RC y el impacto del ancho de banda limitado del amplificador en la velocidad del DAC. Una desventaja importante de los DAC de distribución de carga es que los condensadores en los procesos CMOS ocupan mucho espacio en el chip para su implementación. Por último, dado que la capacitancia en el proceso CMOS es de naturaleza no lineal, se suprimirá la linealidad del DAC en su conjunto. Adecuado para alta precisión de banda media y ancha.

Tipo actual

La estructura se muestra en la figura 3. La ventaja es que, cuando la precisión es inferior a 10 bits, el área puede ser muy pequeña y la velocidad no está limitada por el ancho de banda del amplificador y el gran retardo RC. Puede alcanzar una velocidad muy alta. Dado que toda la corriente fluye directamente al terminal de salida, el consumo de energía es muy eficiente y fácil de implementar. Las desventajas son la sensibilidad al desajuste de los dispositivos y la impedancia de salida limitada de la fuente de corriente. Adecuado para requisitos de banda ancha de alta velocidad.

También es posible no utilizar un amplificador operacional para la salida y utilizar directamente la resistencia de carga para convertir la corriente en una salida de tensión, como se muestra en la figura 4. Esta forma permite que la velocidad del DAC no esté limitada por el ancho de banda del amplificador operacional.

Multiplicación tipo

Algunos de los convertidores DA utilizan una tensión de referencia constante, y otros añaden una señal de CA a la entrada de tensión de referencia. Estos últimos se denominan convertidores DA de tipo multiplicador, ya que pueden obtener el resultado de multiplicar la entrada digital y la entrada de tensión de referencia. En general, un convertidor DA multiplicador no solo puede realizar multiplicaciones, sino que también se puede utilizar como atenuador para atenuar digitalmente una señal de entrada y como modulador para modular una señal de entrada.

Convertidor DA único

A diferencia del sistema de conversión que acabamos de mencionar, un convertidor DA utiliza un método especial para transformar valores digitales en una modulación de ancho de pulso o modulación de frecuencia, que luego se suaviza con un filtro digital para producir una salida de voltaje de uso común (también conocida como modo de flujo de bits) para audio, etc.

Conclusión

Los convertidores ADC y DAC son dos componentes esenciales de cualquier sistema digital. Ayudan a convertir señales analógicas en señales digitales y viceversa. El ADC (convertidor analógico-digital) toma una señal analógica y la convierte en una señal digital, mientras que el DAC (convertidor digital-analógico) toma una señal digital y la convierte en una señal analógica. Ambos componentes son importantes para una amplia gama de aplicaciones, desde el procesamiento de audio y vídeo hasta la transmisión de datos. En este artículo, hemos analizado cómo funcionan estos convertidores y su importancia en diferentes aplicaciones. También hemos explorado los diferentes tipos de convertidores, los diferentes tipos de señales que pueden convertir y las ventajas y desventajas de cada tipo.