Panoramica di MSP430F169

Il Microcontrollore MSP430F169 è uno dei della famiglia MSP430 di Texas Instruments. Comprende più dispositivi che presentano set distinti di periferiche progettate per diverse applicazioni. L’architettura di questi microcontrollori, insieme a cinque modalità a basso consumo, è stata ottimizzata per ottimizzare la durata estesa della batteria per applicazioni di misurazione portatili. Inoltre, l’oscillatore controllato digitalmente (DCO) consente tempi di riattivazione rapidi di meno di 6 µs dalle modalità a basso consumo alla modalità attiva.

Questi microcontrollori trovano tipiche applicazioni in sistemi di sensori, applicazioni di controllo industriale, misuratori portatili e altri domini simili.

Caratteristiche

- Basso consumo energetico;

- Cinque modalità di risparmio energetico;

- DMA interno a tre canali;

- Programmazione seriale integrata;

- Protezione del codice programmabile tramite fusibile di sicurezza;

- Con rilevatore di sottotensione e bootloader;

- Monitoraggio della tensione di alimentazione con rilevamento del livello programmabile.

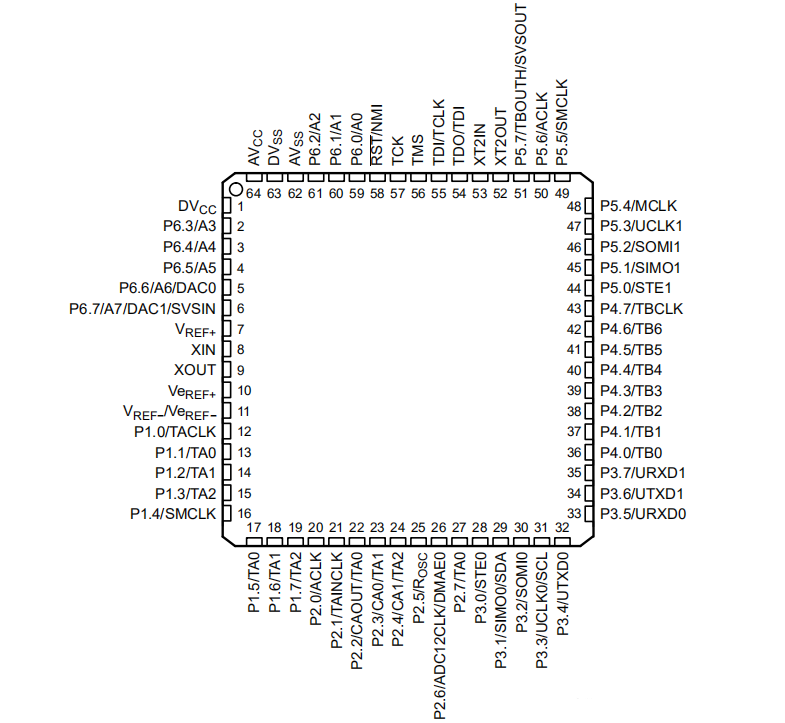

Configurazione dei pin

L’MSP430F169 è effettivamente disponibile sia in versioni a 64 pin che a 100 pin, con diverse configurazioni dei pin per ciascuna.

Per la versione a 64 pin, alcuni pin chiave includono:

| Pin Types | Pin Name | Description |

|---|---|---|

| Power Supply Pins | VCC | Positive supply voltage input |

| GND | Ground | |

| RST/NMI | Reset input and non-maskable interrupt | |

| TEST | Test mode input/output | |

| AVSS/AVCC | Ground and voltage reference for ADC | |

| DVSS/DVCC | Ground and voltage reference for digital circuitry | |

| Input/Output Pins | P1.x-P8.x | General-purpose I/O pins |

| Communication Pins | UCA0CLK | USART module A0 clock input/output |

| UCA0STE | USART module A0 STE input/output | |

| UCA0TXD | USART module A0 transmit data output | |

| UCA0RXD | USART module A0 receive data input | |

| UCB0CLK | SPI module B0 clock input/output | |

| UCB0STE | SPI module B0 STE input/output | |

| UCB0SIMO | SPI module B0 transmit data output | |

| UCB0SOMI | SPI module B0 receive data input | |

| UCB0SDA | I2C module B0 data input/output | |

| UCB0SCL | I2C module B0 clock input/output | |

| Timers and Counters | TA0CCR0-TA0CCR6 | Timer A0 capture/compare register 0-6 |

| Timer A0 control register | ||

| TB0CCR0-TB0CCR2 | Timer B0 capture/compare register 0-2 | |

| Timer B0 control register | ||

| Analog Pins | ADC12CLK | ADC12 clock input |

| ADC12MEM0-ADC12MEM15 | ADC12 memory register 0-15 | |

| AVREF+ | Positive reference voltage input for ADC | |

| AVREF- | Negative reference voltage input for ADC | |

| JTAG Pins | TCLK | Test clock input/output |

| TDI | Test data input | |

| TDO | Test data output | |

| Special Function Pins | ACLK | 32.768 kHz crystal oscillator input |

| SMCLK | System master clock output | |

| RTCCLK | Real-time clock input/output |

Specifiche

| Specification | Value |

|---|---|

| CPU | 16-bit RISC |

| Frequency | 8 MHz |

| Flash memory | 16 KB |

| RAM | 2 KB |

| Standby power | 1.1 µA |

| Active power | 330 µA at 1 MHz, 2.2 V |

| Wake-up time | in less than 6 µs |

| Instruction cycle time | 125 ns |

| Supply voltage | 1.8 V to 3.6 V |

| A/D converter | 12-bit |

| Timer/Counter | 2 * 16-bit |

| Operating Temp | -40 to 85 ℃ |

| DMA | 3 |

| I2C | 1 |

| SPI | 2 |

| Peripherals | timers, serial ports, I2C |

| Package | 64-pin QFP or 64-pin QFN |

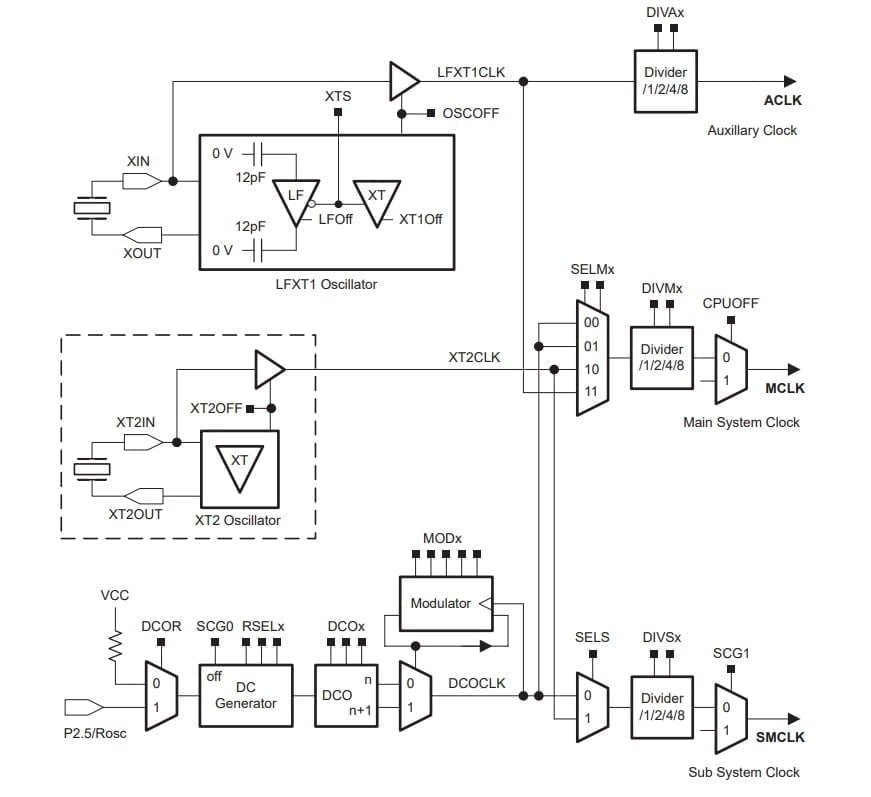

Sistema di clock di MSP430F169

Il sistema di clock è molto importante per il microcomputer a chip singolo. Il motivo per cui il microcomputer a chip singolo MSP430F169 ha un consumo energetico così basso è perché ha un potente sistema di clock!

Tre sorgenti di segnale di clock

1. Bassa frequenza LFXT1CLK (32,768 KHz)

È possibile utilizzare un oscillatore a cristallo standard, un oscillatore o una sorgente di clock esterna per inserire 4 MHz ~ 32 MHz. XT1CLK può essere utilizzato come clock di riferimento per il modulo FLL interno.

L’oscillatore a cristallo a bassa frequenza (32,768 KHz) è direttamente collegato al microcomputer a chip singolo tramite i pin XIN e XOUT e non sono necessari altri dispositivi esterni (è presente una capacità di carico di 12 pF all’interno). In questo momento, l’oscillatore LFXT1 funziona in modalità a bassa frequenza (XTS=0).

Se la MCU è collegata a un oscillatore o risonatore bulk ad alta velocità, 0SCOFF=0 può far funzionare l’oscillatore LFXT1 in modalità ad alta frequenza (XTS=1). In questo momento, l’oscillatore o il risonatore a cristallo ad alta velocità è collegato tramite i pin XIN e XOUT ed è richiesto un condensatore esterno. La dimensione del condensatore è selezionata in base alle caratteristiche dell’oscillatore o del risonatore a cristallo.

Se il segnale LFXT1CLK non viene utilizzato come segnale SMCLK o MCIK, il software può impostare OSCOFF=1 per disabilitare il funzionamento di LFXT1, riducendo così il consumo energetico del microcontrollore.

BCSCTL1:

XTS(BIT6)——Selezione della modalità alta/bassa velocità LFXT1. 0: LFXT1 funziona in modalità oscillatore a cristallo a bassa velocità (predefinito); 1: LFXT1 funziona in modalità oscillatore a cristallo ad alta velocità.

2. Alta frequenza XT2CLK (8 MHz)

È possibile utilizzare un oscillatore a cristallo standard, un oscillatore o una sorgente di clock esterna per inserire 4 MHz ~ 32 MHz.

L’oscillatore XT2 genera il segnale di clock XT2CLK e le sue caratteristiche operative sono simili a quelle dell’oscillatore LFXT1 quando funziona in modalità ad alta frequenza. Se XT2CLK non viene utilizzato come segnale di clock MCLK e SMCLK, l’oscillatore XT2 può essere disabilitato con il bit di controllo XT2OFF.

BCSCTL1:

XT2OFF (BIT7) – Controllo dell’oscillatore a cristallo XT2 ad alta velocità. 0: Oscillatore a cristallo XT2 ad alta velocità acceso; 1: Oscillatore a cristallo XT2 ad alta velocità spento.

3. Oscillatore interno DCOCLK (1 MHz)

Stabilizzato dal modulo FLL.

Quando l’oscillatore fallisce, DCO verrà automaticamente selezionato come sorgente di clock per MCLK.

La frequenza dell’oscillatore DCO può essere regolata dal software impostando i bit DCOx. MODx e RSEL.x. Quando il segnale DCOCLK non viene utilizzato come segnale di clock SMCLK e MCLK, il generatore DC può essere disabilitato con il bit di controllo SCGO.

Dopo il segnale PUC, DCOCLK viene automaticamente selezionato come segnale di clock MCLK e la sorgente di clock di MCLK può essere ulteriormente impostata su LFXT1 o XT2 come richiesto. La sequenza di configurazione è la seguente:

- Impostare OSCOFF=1;

- Impostare OFIFG=0;

- Ritardare e attendere almeno 50ps;

- Controllare nuovamente OFIFG, se OFIFG=1, ripetere i passaggi (3) e (4) fino a quando OFIFG=0.

DCOCTL:

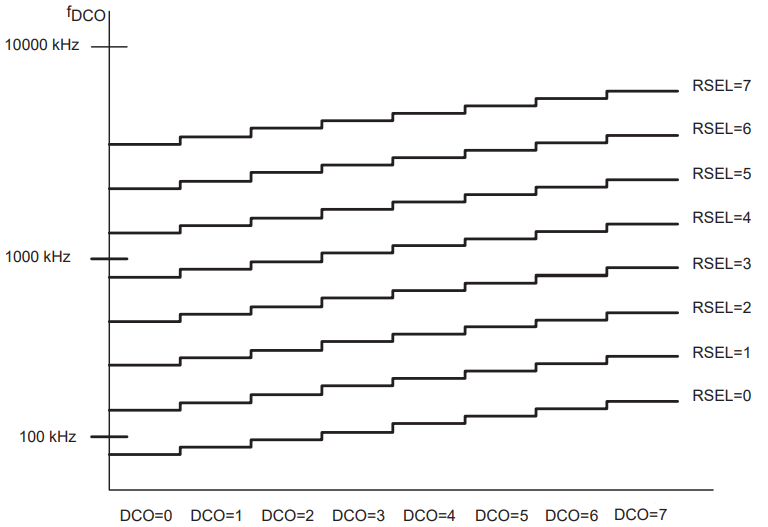

DCOx (BIT7, BIT6, BIT5)——Selezione della frequenza DCO, è possibile selezionare 8 tipi di frequenze e la frequenza DCOCLK può essere regolata a intervalli. La selezione della frequenza si basa sulla banda di frequenza selezionata da RSELx. La relazione tra DCOx, RSELx e il clock interno è la seguente:

MODx (BIT4, BIT3, BIT2, BIT1, BIT0) – Impostazione del modulatore DAC. Il controllo commuta le due frequenze selezionate da DCOx e DCOx+1 per regolare con precisione la frequenza di uscita del DCO. Se la costante DCOx è 7, significa che è stata selezionata la frequenza più alta. A questo punto, MODx non è valido e non può essere utilizzato per la regolazione della frequenza.

BCSCTL1:

RSELx (BIT2, BIT1, BIT0) – la selezione della banda di frequenza dell’oscillatore DCO, questi 3 bit controllano una resistenza interna per determinare la frequenza nominale. 0: Seleziona la frequenza nominale più bassa… 7: Seleziona la frequenza nominale più alta.

BCSCTL2:

DCOR(BIT0)——Seleziona la resistenza dell’oscillatore DCO. 0: resistenza interna; 1: resistenza esterna.

Tre sorgenti di clock

1. Clock ausiliario ACLK

ACLK si ottiene dopo che LFXT1CLK è diviso per 1, 2, 4 e 8. Può essere utilizzato come segnale di clock per ciascun modulo periferico ed è generalmente utilizzato per periferiche a bassa velocità.

BCSCTL1:

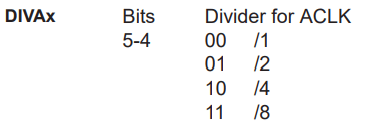

DIVAx (BIT5, BIT4)——Selezione della divisione della frequenza ACLK, la relazione di selezione della divisione della frequenza è la seguente:

Definizione macro: DIVA_0 (divisione della frequenza 1/nessuna divisione della frequenza), DIVA_1 (divisione della frequenza 2), DIVA_2 (divisione della frequenza 4), DIVA_3 (divisione della frequenza 8)

2. Clock principale di sistema MCLK

MCLK può essere ottenuto da LFXT1CLK, XT2CLK e DCOCLK dopo la divisione della frequenza per 1, 2, 4 e 8. È spesso utilizzato per il funzionamento della CPU, l’esecuzione del programma e altri moduli che utilizzano clock ad alta velocità.

BCSCTL2:

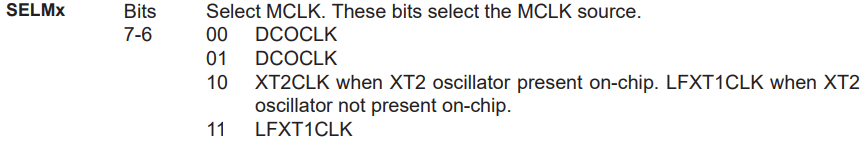

SELMx (BIT7, BIT6) – seleziona la sorgente di clock MCLK, la relazione di selezione del clock è la seguente:

Definizione macro: SELM_0 (DCOCLK predefinito), SELM_1 (DCOCLK), SELM_2 (XT2CLK), SELM_3 (LFXT1CLK)

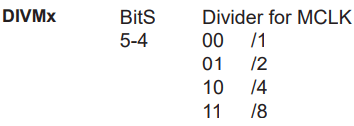

DIVMx (BIT5, BIT4) – Selezione della divisione della frequenza MCLK, la relazione di selezione della divisione della frequenza è la seguente:

Definizione macro: DIVM_0 (divisione della frequenza 1/nessuna divisione della frequenza), DIVM_1 (divisione della frequenza 2), DIVM_2 (divisione della frequenza 4), DIVM_3 (divisione della frequenza 8)

3. Clock del sottosistema SMCLK

SMCLK può essere ottenuto dividendo XT2CLK e DCOCLK per 1, 2, 4 e 8 ed è spesso utilizzato in moduli periferici ad alta velocità.

BCSCTL2:

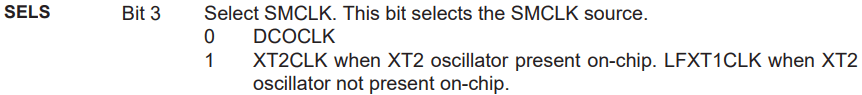

SELSx (BIT3) – seleziona la sorgente di clock MCLK, la relazione di selezione del clock è la seguente:

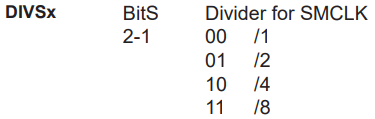

DIVSx (BIT2, BIT1) – Selezione della divisione della frequenza SMCLK, la relazione di selezione della divisione della frequenza è la seguente:

Definizione macro: DIVS_0 (divisione di frequenza 1/nessuna divisione di frequenza), DIVS_1 (divisione di frequenza 2), DIVS_2 (divisione di frequenza 4), DIVS_3 (divisione di frequenza 8)