A medida que aumenta la velocidad de conmutación de salida de los circuitos integrados y la densidad de las placas PCB, la integridad de la señal se ha convertido en uno de los aspectos que deben tenerse en cuenta en el diseño de PCB digitales de alta velocidad. Los problemas de integridad de la señal pueden provocar que el sistema genere datos incorrectos, que el circuito no funcione correctamente o incluso que deje de funcionar por completo. Entonces, ¿cómo se puede tener plenamente en cuenta el factor de la integridad de la señal en el proceso de diseño de placas PCB y adoptar medidas de control eficaces? Siga leyendo este artículo para obtener más información.

¿Qué es la integridad de la señal PCB?

La integridad de la señal del PCB se refiere a la capacidad de la señal para responder con la sincronización y el voltaje correctos en el circuito. Es un estado en el que la señal no se daña e indica la calidad de la señal en la línea de señal.

Diferentes problemas de integridad de la señal

Los problemas de integridad de la señal pueden causar o provocar directamente distorsión de la señal, errores de sincronización, datos incorrectos, líneas de dirección y control, mal funcionamiento del sistema e incluso fallos del sistema. Los principales problemas de integridad de la señal incluyen: retardo, reflexión, ruido de conmutación síncrona, oscilación, rebote de tierra, diafonía, etc.

Retraso

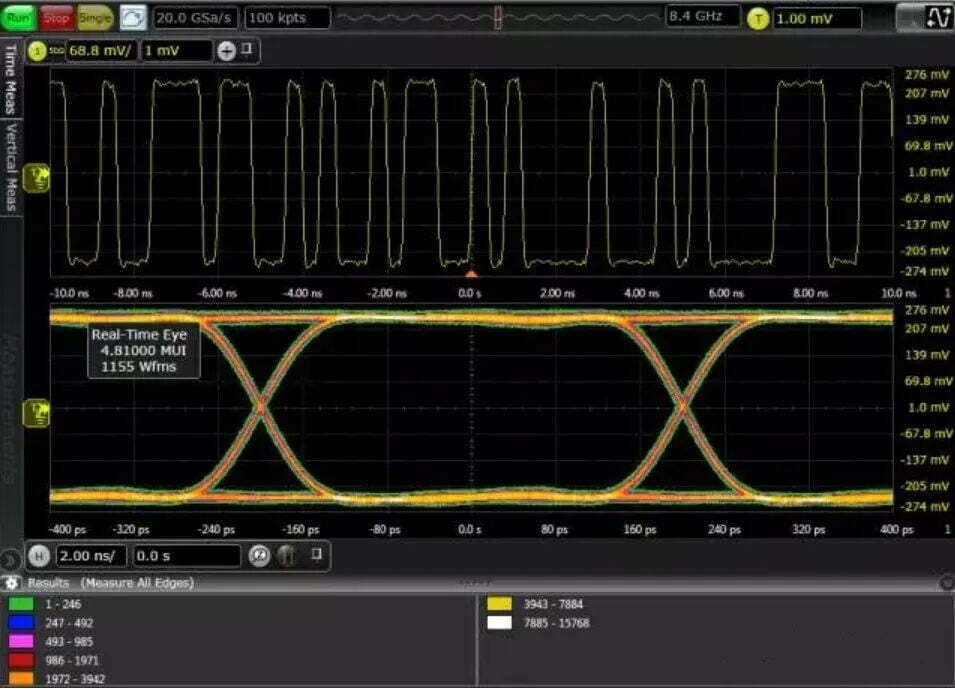

El retraso significa que la señal se transmite a una velocidad limitada por los cables de la placa PCB, y la señal se envía desde el extremo emisor al extremo receptor, y hay un retraso de transmisión entre ellos. El retraso de la señal afectará a la sincronización del sistema, y el retraso de transmisión depende principalmente de la longitud del cable y de la constante dieléctrica del medio que rodea al cable. En un sistema digital de alta velocidad, la longitud de la línea de transmisión de la señal es el factor más directo que afecta a la diferencia de fase del pulso de reloj. La diferencia de fase del pulso de reloj significa que las dos señales de reloj generadas al mismo tiempo no están sincronizadas cuando llegan al extremo receptor. La diferencia de fase del pulso de reloj reduce la previsibilidad de la llegada del flanco de la señal. Si la diferencia de fase del pulso de reloj es demasiado grande, se generará una señal errónea en el extremo receptor. Como se muestra en la figura siguiente, el retraso de la línea de transmisión se ha convertido en una parte importante del ciclo del pulso de reloj.

Reflexión

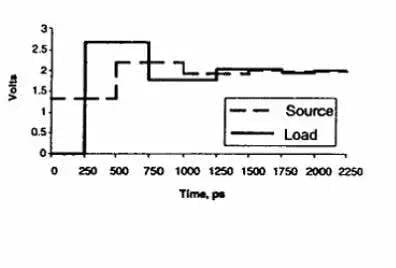

La reflexión es el eco en la línea de subtransmisión. Cuando el tiempo de retardo de la señal es mucho mayor que el tiempo de transición de la señal, la línea de señal debe considerarse como una línea de transmisión. Cuando la impedancia característica de la línea de transmisión no coincide con la impedancia de carga, parte de la potencia de la señal (voltaje o corriente) se transmite por la línea y llega a la carga, pero otra parte se refleja. Si la impedancia de carga es menor que la impedancia original, la reflexión es negativa. De lo contrario, la reflexión es positiva. Las variaciones en la geometría del enrutamiento, la terminación inadecuada de la línea de transmisión, la transmisión a través de conectores y las discontinuidades en los planos de alimentación pueden causar tales reflexiones.

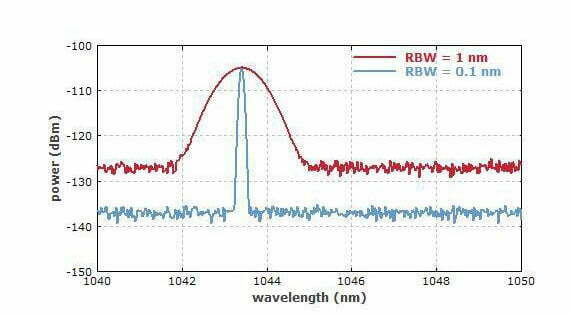

Ruido de conmutación simultánea (SSN)

Se generará ruido de conmutación simultánea si muchas señales digitales de la PCB se conmutan de forma sincronizada (como el bus de datos de la CPU, el bus de direcciones, etc.). Esto se debe a que hay impedancia en la línea de alimentación y en la tierra, y habrá ruido de rebote en el plano de tierra (rebote de tierra). La intensidad del SSN y del rebote de tierra también depende de las características de E/S del circuito integrado, la impedancia de la capa de alimentación y la capa plana de la PCB, y la disposición y el enrutamiento de los dispositivos de alta velocidad en la PCB.

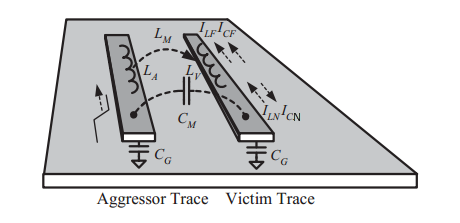

Interferencia

La diafonía es el acoplamiento entre dos líneas de señal, y la inductancia mutua y la capacitancia mutua entre las líneas de señal provocan ruido en la línea. El acoplamiento capacitivo induce una corriente acoplada, mientras que el acoplamiento inductivo induce un voltaje acoplado. El ruido de diafonía se origina en el acoplamiento electromagnético entre redes de señales, entre sistemas de señales y sistemas de distribución de energía, y entre vías. El entrelazamiento puede provocar relojes falsos, errores de datos intermitentes, etc., y afectar a la calidad de transmisión de las señales adyacentes. De hecho, no es necesario eliminar completamente la diafonía, basta con mantenerla dentro de la tolerancia del sistema. Los parámetros de la capa de la placa PCB, el espaciado de las líneas de señal, las características eléctricas del controlador y el receptor, y el método de terminación de la línea base tienen un cierto impacto en la diafonía.

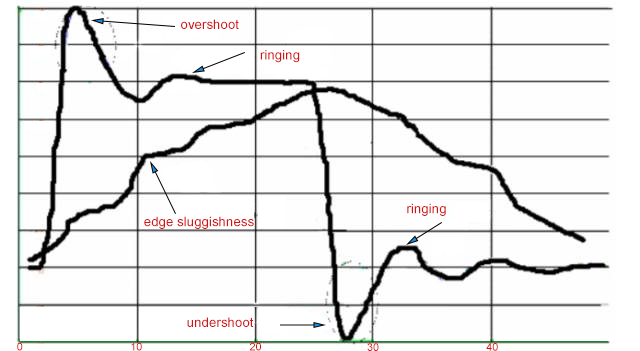

Sobreexposición y subexposición

El sobreimpulso es el primer pico o valle que supera el voltaje establecido. Para los flancos ascendentes, se refiere al voltaje más alto, y para los flancos descendentes, se refiere al voltaje más bajo. El subimpulso es cuando el siguiente valle o pico supera el voltaje establecido. Un sobreimpulso excesivo puede hacer que los diodos de protección funcionen, lo que provoca su fallo prematuro. Un subimpulso excesivo puede provocar errores espurios de reloj o datos (manejo incorrecto).

Timbre y redondeo

El fenómeno de oscilación se repite en forma de sobreoscilación y suboscilación. La oscilación de la señal es la oscilación causada por la inductancia y la capacitancia de transición en la línea, que pertenece al estado subamortiguado. La oscilación envolvente es un estado sobreamortiguado. Las oscilaciones y las oscilaciones orbitales, al igual que los reflejos, son causadas por una variedad de factores. La oscilación se puede reducir con una terminación adecuada, pero no se puede eliminar por completo.

Ruido de rebote en tierra y ruido de retorno

Ruido de rebote en el suelo

Cuando se produce una gran sobrecarga de corriente en el circuito, se genera ruido de rebote en el plano de tierra. Por ejemplo, si se activan al mismo tiempo las salidas de un gran número de chips, se producirá una gran corriente transitoria que fluirá a través del plano de alimentación del chip y la placa. A continuación, el ruido de la fuente de alimentación es inducido por la inductancia y la resistencia del paquete del chip y el plano de alimentación, lo que crea fluctuaciones y variaciones de voltaje en el plano de tierra real (O V). Este ruido afecta al funcionamiento de otros componentes. Un aumento de la capacitancia de carga, una disminución de la resistencia de carga, un aumento de la inductancia de tierra y un aumento del número de dispositivos de conmutación provocarán un aumento del rebote de tierra.

Ruido de retorno

El ruido de retorno del plano de tierra se genera cuando las señales digitales viajan al área de tierra analógica. Esto puede deberse a la división del plano de tierra (incluida la alimentación y la tierra), por ejemplo, el plano de tierra se divide en tierra digital, tierra analógica, tierra de blindaje, etc. Del mismo modo, los planos de alimentación también pueden dividirse en 2,5 V, 3,3 V, 5 V, etc. Por lo tanto, en el diseño de PCB multivoltaje, debemos prestar especial atención al ruido de rebote y al ruido de retorno del plano de tierra.

Causas de los problemas de integridad de la señal

Factores como los parámetros de los componentes y las placas PCB, la disposición de los componentes en las placas PCB y el cableado de las líneas de señal de alta velocidad provocarán problemas de integridad de la señal. Para el diseño de PCB, la integridad de la señal debe proporcionar Para el diseño de circuitos, la integridad de la señal requiere componentes de terminación, estrategias de colocación e información de enrutamiento.

¿Cómo optimizar la integridad de la señal?

El problema de la integridad de la señal no se debe a un único factor, sino a múltiples factores relacionados con el diseño de la placa. Por lo tanto, debemos utilizar diferentes métodos para mejorar la integridad de la señal en función de cada situación específica.

Análisis de diafonía

El tamaño de la diafonía es inversamente proporcional al espaciado entre líneas y proporcional a la longitud paralela de la línea y la frecuencia de la señal. La diafonía variará con la carga del circuito. Para la misma topología y situación de cableado, cuanto mayor sea la carga, mayor será la diafonía. En los circuitos digitales, el cambio de flanco de la señal tiene el mayor impacto en la diafonía, y cuanto más rápido sea el cambio de flanco, mayor será la diafonía. Teniendo en cuenta las características anteriores de la diafonía, podemos utilizar los siguientes métodos para reducirla:

- Elegir un dispositivo lento para reducir la velocidad de transición del flanco de la señal.

- Evitar mezclar diferentes tipos de señales.

- Reducir la interferencia de acoplamiento reduciendo la carga.

- Minimizar la longitud paralela entre líneas de transmisión adyacentes.

- Aumentar la distancia entre los conductores donde pueda producirse un acoplamiento capacitivo.

- Un enfoque más eficaz consiste en aislar los cables con cables de tierra.

- Insertar un cable de tierra entre los cables de señal adyacentes.

- Minimizar el número de bucles y el área de los bucles.

- Evitar compartir el mismo cable para el bucle de señal.

- Las capas de señal de dos capas adyacentes deben evitar el cableado paralelo en la medida de lo posible.

- Las señales sensibles a la diafonía deben disponerse en la capa interna en la medida de lo posible.

análisis de reflexión

Las reflexiones se producen cada vez que una señal encuentra un cambio de impedancia mientras se desplaza por una línea de transmisión. La principal forma de resolver el problema de las reflexiones es realizar una adaptación de la impedancia de terminación. Normalmente hay dos estrategias para la terminación de la línea de transmisión: terminación en paralelo y terminación en serie.

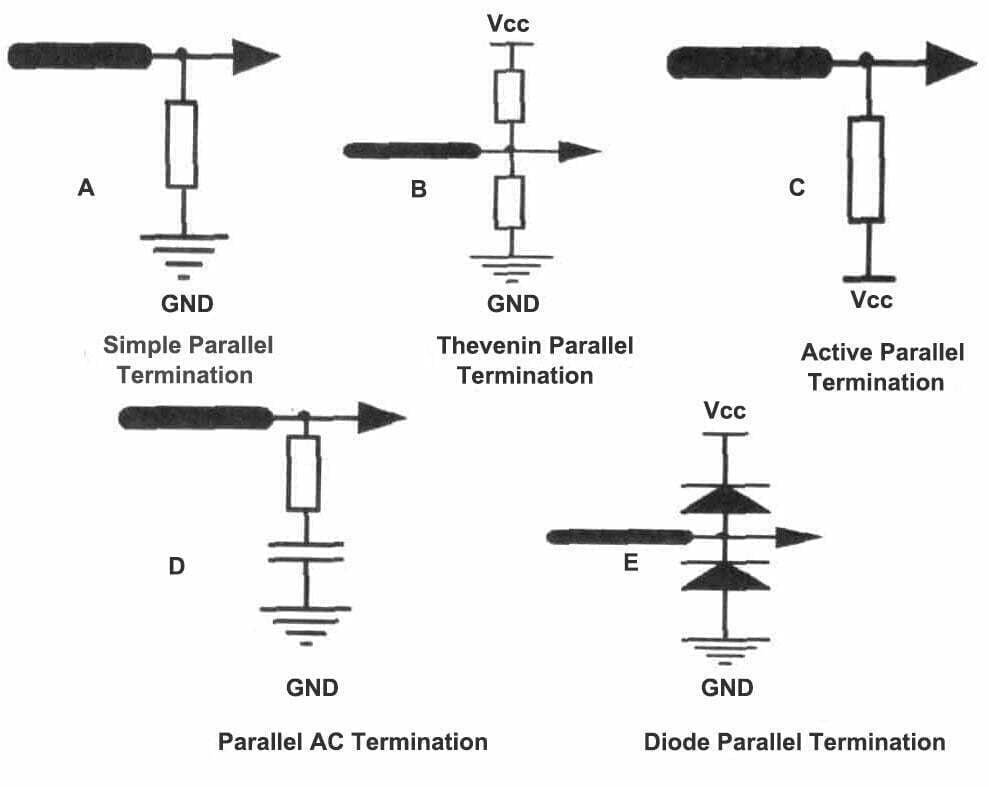

Terminación paralela

La terminación paralela sirve principalmente para conectar la impedancia pull-up o pull-down lo más cerca posible del extremo de carga para lograr la adaptación de impedancia del terminal. Según los diferentes entornos de aplicación, la terminación paralela se puede dividir en varios tipos, como se muestra en la siguiente figura.

Terminación en serie

La terminación en serie se consigue insertando en serie una resistencia en la línea de transmisión lo más cerca posible de la fuente. La terminación en serie tiene como objetivo igualar la impedancia de la fuente de señal, por lo que la resistencia de la resistencia en serie insertada más la impedancia de salida de la fuente de impulsión debe ser mayor o igual que la impedancia de la línea de transmisión. Esta estrategia suprime la señal reflejada desde la carga haciendo que el coeficiente de reflexión del extremo de la fuente sea cero (la entrada del extremo de la carga es de alta impedancia y no absorbe energía) y luego se refleja de vuelta al extremo de la carga desde el extremo de la fuente.

Modelado del análisis de la integridad de la señal

El modelado y la simulación adecuados de circuitos es la solución más común para la integridad de la señal. En el diseño de circuitos de alta velocidad, el análisis de simulación está demostrando cada vez más su superioridad, ya que puede proporcionar a los diseñadores resultados precisos e intuitivos. De esta manera, podemos detectar problemas de forma temprana y corregirlos a tiempo. Existen tres métodos de modelado de circuitos que se utilizan habitualmente: el modelo SPICE, el modelo IBIS y el modelo Verilog-A.

Modelo SPICE

SPICE es un potente simulador de circuitos analógicos de uso general. Consta de dos partes: ecuación del modelo y parámetros del modelo. Dado que se proporciona la ecuación del modelo, el modelo SPICE puede conectarse muy estrechamente con el algoritmo del simulador, lo que permite obtener una mayor eficiencia en el análisis y mejores resultados.

Modelo IBIS

El modelo IBIS es un modelo que se utiliza especialmente para el análisis de la integridad de la señal digital a nivel de placa PCB y a nivel de sistema. Utiliza tablas I/V y V/T para describir las características de las celdas y pines de E/S de los circuitos integrados digitales. La precisión del análisis del modelo IBIS depende principalmente del número de puntos de datos y de la precisión de los datos de las tablas I/V y V/T. En comparación con el modelo SPICE, la carga de cálculo del modelo IBIS es muy pequeña.

Conclusión

Con el continuo desarrollo de la tecnología microelectrónica, el uso de dispositivos de alta velocidad y el diseño de sistemas digitales de alta velocidad están aumentando. Las velocidades de datos del sistema, las frecuencias de reloj y las densidades de los circuitos también están aumentando. Por lo tanto, los requisitos de diseño de las placas PCB son cada vez más exigentes, especialmente en lo que respecta a la integridad de la señal. Para garantizar que la PCB tenga una buena integridad de señal, se deben tener en cuenta de forma integral diversos factores que influyen en ella.