Analisi dei guasti dei circuiti integrati

Risorsa tecnica completa su metodologie, strumenti e casi di studio per l'analisi dei guasti nei semiconduttori.

Che cos'è l'analisi dei guasti dei circuiti integrati?

L'analisi dei guasti dei circuiti integrati (IC) è un processo sistematico utilizzato per identificare, isolare e determinare la causa principale dei guasti dei dispositivi a semiconduttore. Questa disciplina ingegneristica fondamentale combina tecniche di imaging avanzate, test elettrici e scienza dei materiali per risolvere i problemi nei circuiti integrati in diversi settori industriali.

Un'efficace analisi dei guasti migliora l'affidabilità del prodotto, riduce i costi di produzione, accelera il time-to-market e garantisce la conformità agli standard di settore. Svolge un ruolo fondamentale nel controllo qualità, nell'ingegneria dell'affidabilità e nei cicli di miglioramento del prodotto.

Obiettivi chiave dell'analisi dei guasti dei circuiti integrati

- Identificare le cause profonde dei guasti dei circuiti integrati attraverso un'indagine sistematica.

- Determinare se i guasti derivano dalla progettazione, dalla produzione o dall'applicazione.

- Sviluppare azioni correttive per prevenire futuri guasti

- Convalidare l'affidabilità e le prestazioni dei circuiti integrati

- Supporto alla segnalazione dei guasti e all'analisi dei dati di affidabilità.

Guide tecniche e metodologie

Diagramma di flusso diagnostico

Approccio sistematico che va dal sintomo del guasto all'identificazione della causa principale.

Nessun percorso di guasto di alimentazione/uscita

- 1. Verificare la presenza di danni da scariche elettrostatiche (ESD) mediante analisi SEM/EDS.

- 2. Verificare le saldature mediante ispezione a raggi X 3D

- 3. Test per la rottura dell'ossido di gate utilizzando EMMI

- 4 Eseguire test di continuità con OBIRCH

- 5 Analizzare l'integrità del pacchetto con C-SAM

Percorso di guasto dei malfunzionamenti intermittenti

- 1. Escludere le microfratture BGA utilizzando C-SAM

- 2. Verificare la presenza di stress termico mediante termografia a infrarossi.

- 3. Test per la rilevazione di latch-up legati alla progettazione tramite simulazione di circuiti

- 4. Verificare l'integrità della rete di distribuzione dell'energia elettrica.

Guida operativa EMMI

Procedura dettagliata per l'analisi mediante microscopia a emissione di elettroni.

Preparazione del dispositivo

Accendere il dispositivo nello stato che riproduce il guasto e assicurarsi che sia ben raffreddato.

Allestimento della camera oscura

Posizionare il dispositivo sotto il microscopio EMMI, assicurandosi che sia correttamente allineato.

Configurazione della fotocamera

Impostare il tempo di esposizione appropriato (in genere da 10 a 60 secondi) e la sensibilità

Acquisizione di immagini

Per ottenere risultati ottimali, scatta più foto con tempi di esposizione diversi.

Analisi e sovrapposizione

Sovrapporre i punti di emissione al progetto per identificare le strutture difettose

Suggerimento per la risoluzione dei problemi

Se non compaiono punti caldi, verificare che il chip si trovi in uno stato che riproduce il guasto e controllare se il meccanismo di guasto produce emissioni di fotoni (i circuiti aperti in genere non le producono).

Errori comuni nell'analisi dei guasti

Trascurare i danni da scariche elettrostatiche

Non tenere conto dei danni da scarica elettrostatica durante la manipolazione, soprattutto nei chip CMOS. Verificare sempre la funzionalità del cinturino da polso e i protocolli di messa a terra.

Riduzione di potenza inadeguata

Bruciatura delle resistenze dovuta al funzionamento con un carico di potenza superiore all'80%. La procedura consigliata è una riduzione del 50% per garantire l'affidabilità in condizioni variabili.

Riproduzione errata del guasto

Analizzare i dispositivi in condizioni che non riproducono fedelmente lo scenario di guasto sul campo, portando a un'errata identificazione della causa principale.

Trascurare i problemi di imballaggio

Concentrandosi esclusivamente sui problemi a livello del chip, si trascurano i guasti legati al package, come la delaminazione, la corrosione dei terminali o la fatica delle saldature.

Documentazione insufficiente

La mancata documentazione accurata di ogni fase dell'analisi rende difficile replicare i risultati o eseguire analisi di tendenza su più guasti.

Problemi di calibrazione degli strumenti

L'utilizzo di apparecchiature non correttamente calibrate porta a misurazioni imprecise e a conclusioni errate nell'analisi dei guasti.

Casi di studio del settore

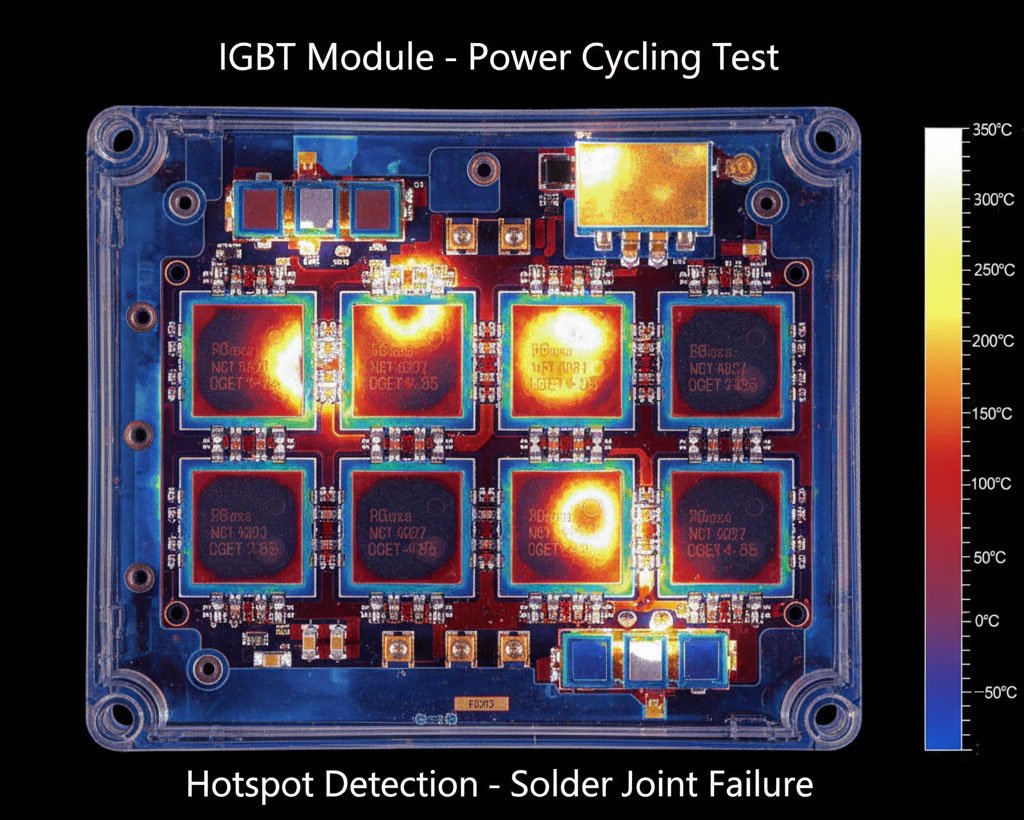

Guasto del modulo IGBT nei veicoli elettrici

Sintomo

Interruzione improvvisa di alimentazione durante la ricarica, senza danni esterni visibili al sistema di propulsione del veicolo elettrico.

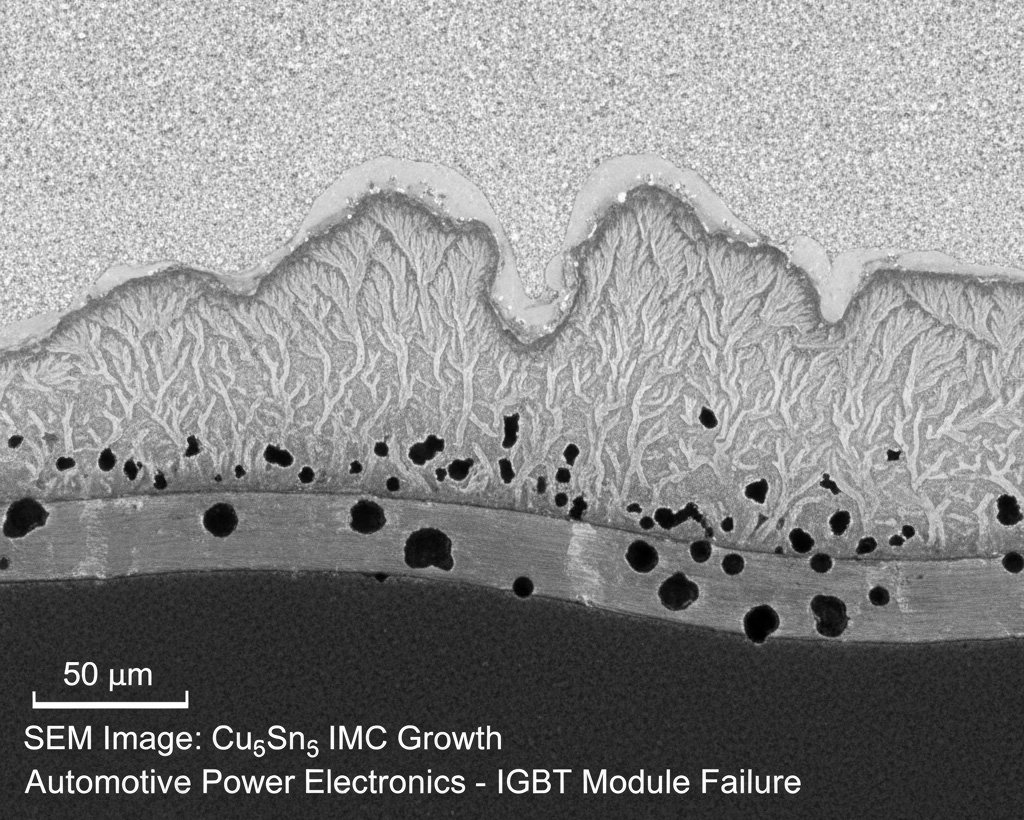

Analisi consentita

- L'imaging termico ha rivelato punti caldi nel modulo IGBT durante il ciclo di accensione/spegnimento.

- L'analisi SEM/EDS ha rilevato una crescita eccessiva di composti intermetallici (Cu₆Sn₅) nelle giunzioni di saldatura.

- L'analisi in sezione trasversale ha evidenziato la formazione di vuoti di Kirkendall all'interfaccia tra la saldatura e il substrato.

- La simulazione FEA ha collegato il guasto a un profilo di rifusione della saldatura insufficiente.

Soluzione e risultato

Profilo di rifusione regolato per garantire una bagnatura adeguata e aggiunta di cuscinetti nichelati per controllare la crescita degli intermetalli.

Risultato: il tasso di guasti sul campo si è ridotto dello 0,58% all'anno, con un risparmio di 2 milioni di dollari sui costi di garanzia.

Norme pertinenti

Risultati della termografia

Immagine SEM della crescita dell'IMC

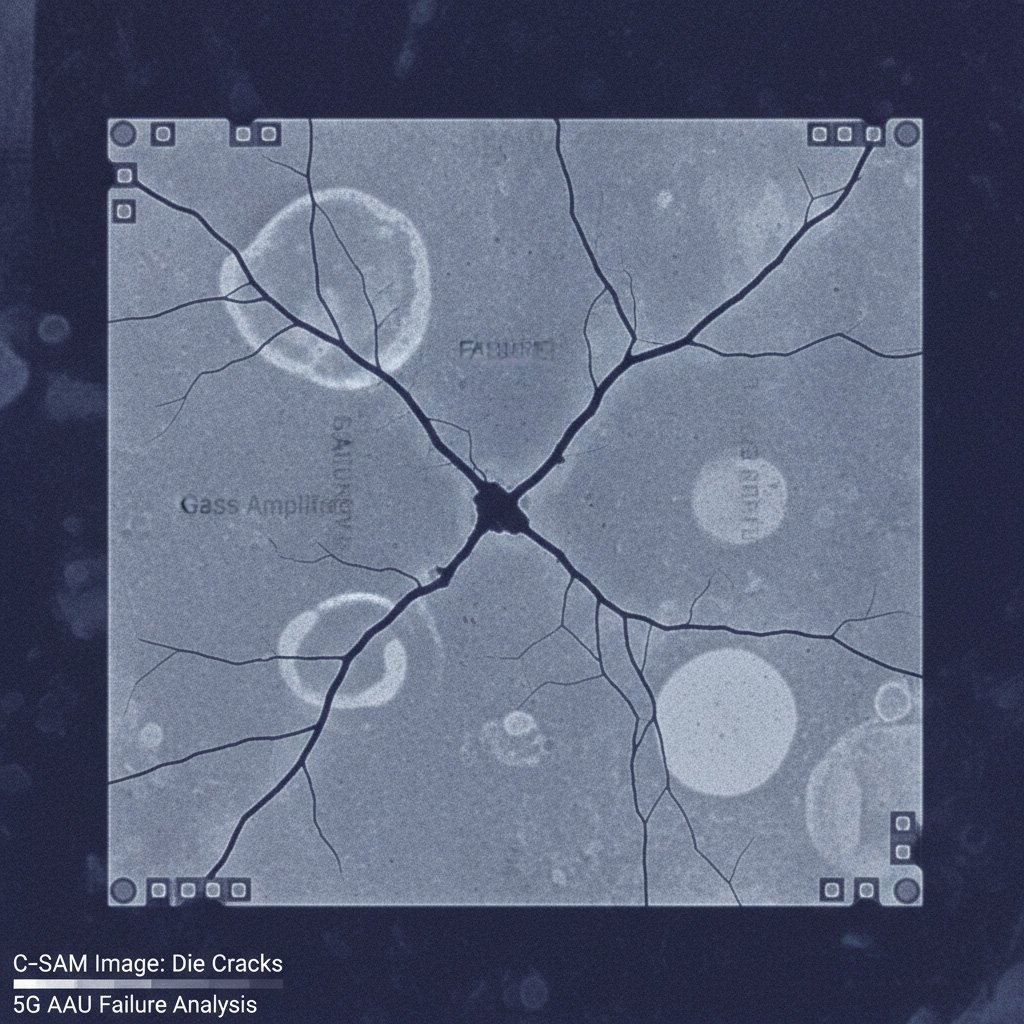

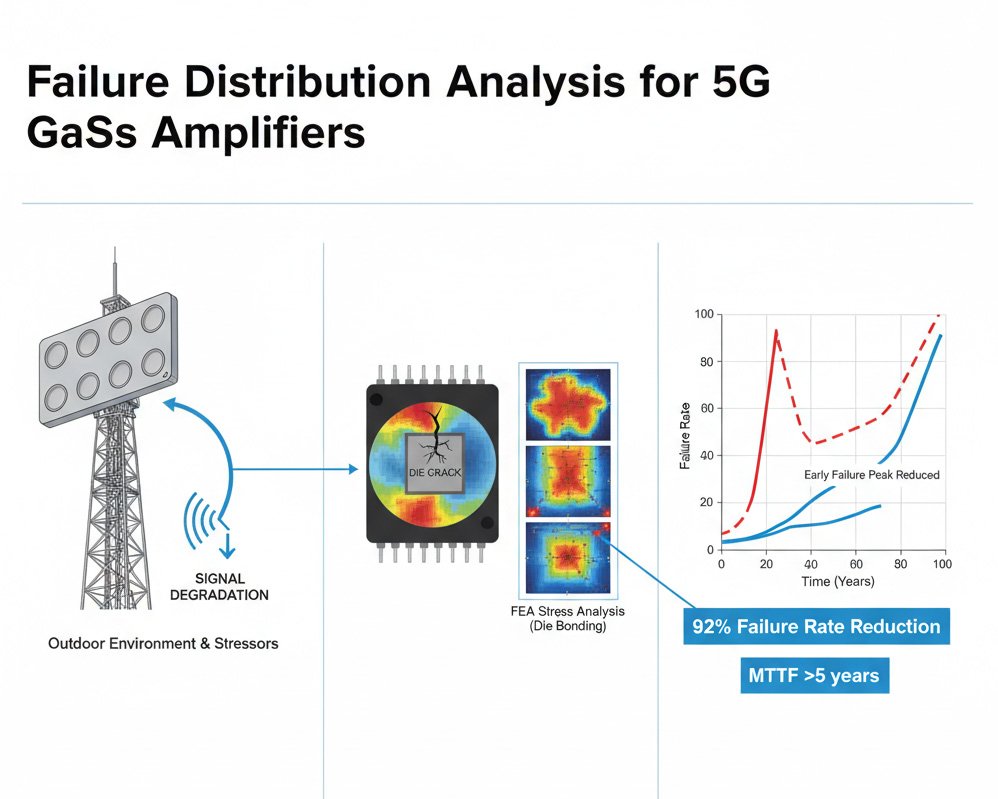

Guasto dell'amplificatore GaAs nelle AAU 5G

Sintomo

Guasti sul campo nelle unità di antenna attiva 5G (AAU) entro 6 mesi dall'installazione, con conseguente degrado del segnale.

Analisi consentita

- L'ispezione C-SAM ha rilevato crepe nel chip degli amplificatori di potenza in GaAs

- Un controllo dell'imballaggio ha rilevato segni di espulsione anomali sul retro dello stampo.

- L'analisi dei dati di affidabilità ha mostrato una distribuzione dei guasti che corrispondeva alla modalità di guasto precoce

- L'analisi agli elementi finiti ha confermato lo stress meccanico durante il processo di incollaggio del chip.

Soluzione e risultato

Pellicola blu modificata per il die bonding al fine di ridurre lo stress meccanico e implementazione di un'ispezione post-bonding al 100% mediante ispezione ottica automatizzata.

Risultato: il tasso di guasti si è ridotto del 92%, estendendo il tempo medio tra i guasti a oltre 5 anni.

Norme pertinenti

Immagine C-SAM delle crepe dello stampo

Analisi della distribuzione dei guasti

Guasto BGA negli smartphone

Sintomo

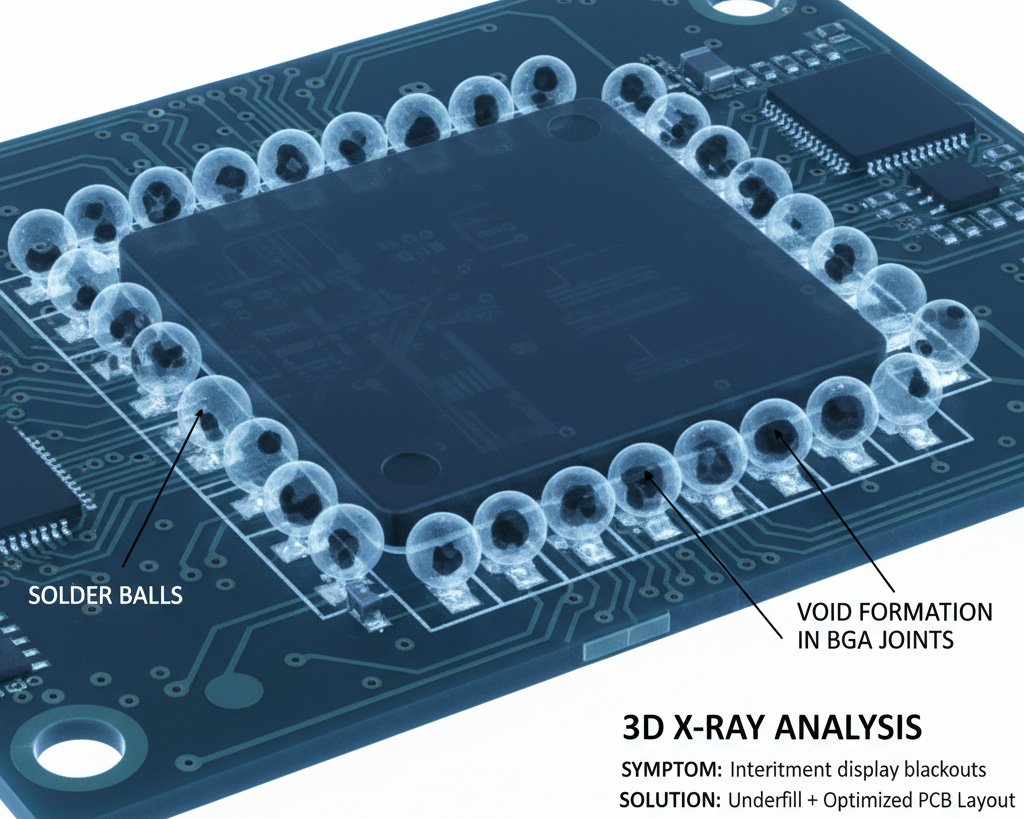

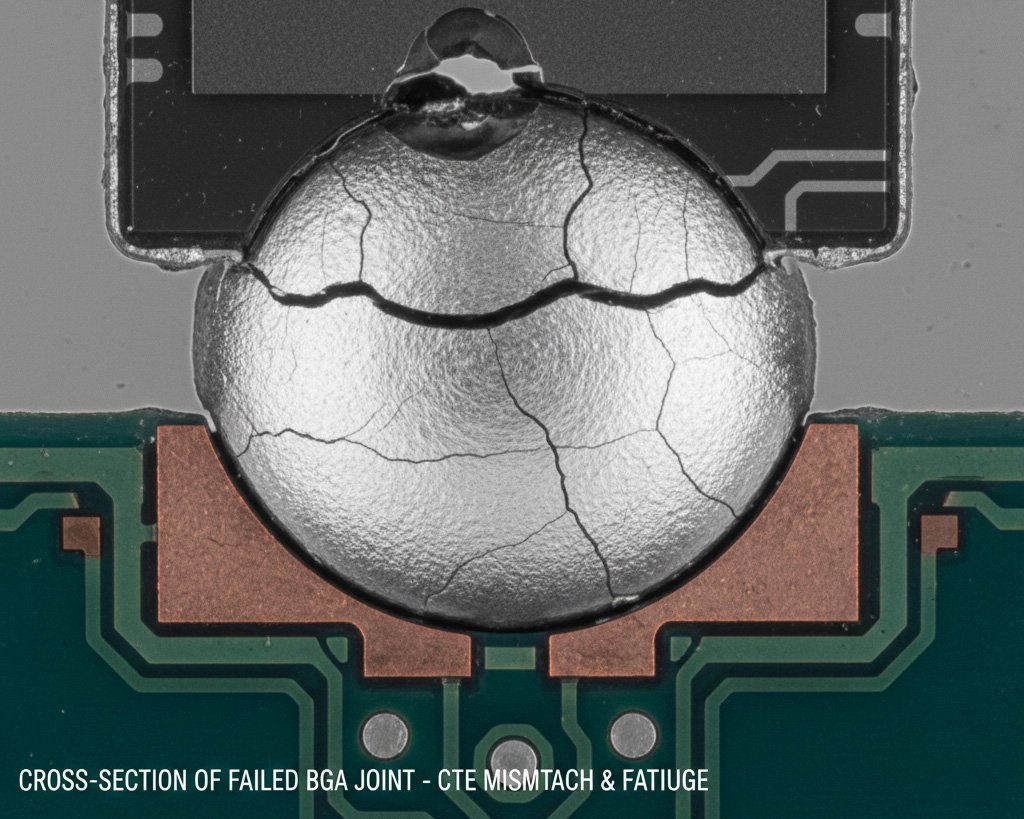

Dopo 6-8 mesi di utilizzo, si verificano spegnimenti intermittenti del display e mancata risposta del touchscreen negli smartphone di fascia alta.

Analisi consentita

- Il ciclo termico (da -40 °C a 85 °C) ha riprodotto il guasto in condizioni di laboratorio

- La microscopia acustica a scansione (SAM) ha rivelato la fatica delle giunzioni di saldatura.

- La sezione trasversale ha confermato la discrepanza del CTE (coefficiente di dilatazione termica).

- L'analisi a raggi X 3D ha quantificato la formazione di vuoti nel 18% delle giunzioni BGA.

Soluzione e risultato

È stato implementato un materiale di riempimento inferiore con una Tg (temperatura di transizione vetrosa) più elevata e il layout del PCB è stato ottimizzato per ridurre i gradienti termici.

Risultato: i resi sul campo si sono ridotti del 76%, senza che si siano verificati guasti dopo 18 mesi di utilizzo.

Norme pertinenti

Radiografia 3D dei vuoti BGA

Sezione trasversale del giunto difettoso

Guasto del circuito integrato di controllo avionico

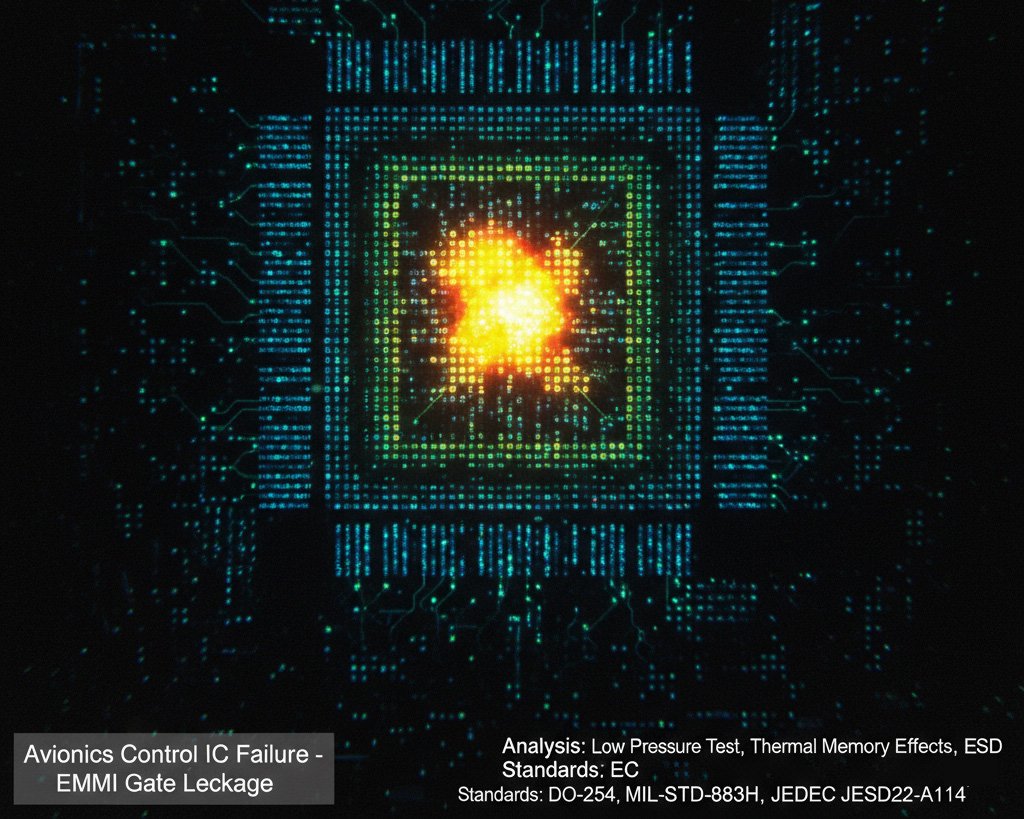

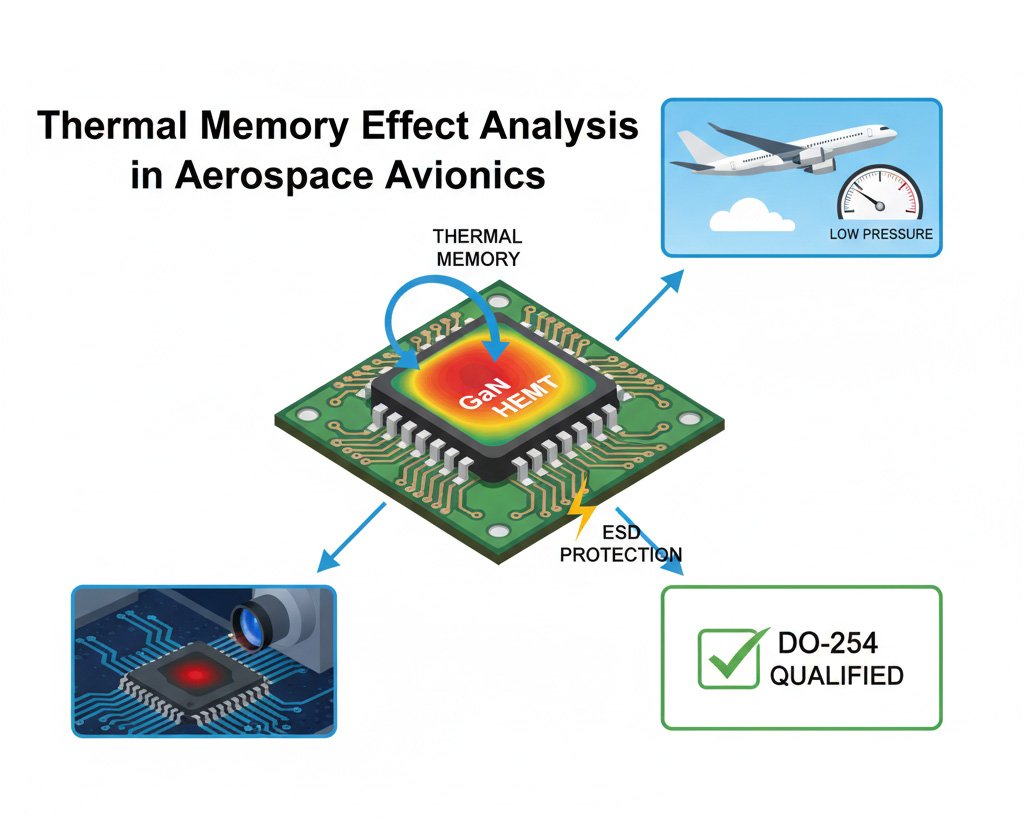

Sintomo

Durante il volo ad alta quota si verificano riavvii casuali dei sistemi nei moduli di controllo avionici, senza uno schema preciso.

Analisi consentita

- Le prove ambientali hanno riprodotto il guasto in condizioni di bassa pressione (alta quota).

- EMMI ha rilevato perdite di corrente intermittenti nel circuito integrato di gestione dell'alimentazione.

- La modellazione IC-CAP ha identificato effetti di memoria termica non modellati negli HEMT GaN

- I test ESD hanno rivelato una protezione insufficiente nei circuiti di ingresso.

Soluzione e risultato

Modello ASM-HEMT aggiornato per includere gli effetti di memoria termica e circuiti di protezione ESD migliorati.

Risultato: Eliminazione completa dei ripristini in volo, con qualificazione positiva secondo gli standard DO-254.

Norme pertinenti

Immagine EMMI della perdita del gate

Analisi dell'effetto memoria termica

Strumenti e attrezzature

| Attrezzo | Caso d'uso principale | Limite di risoluzione | Ideale per | Limitazione |

|---|---|---|---|---|

| EMMI | Localizzazione dei punti critici (perdite, guasti) | ~1μm | CMOS/FinFET | Nessun segnale per circuiti aperti |

| C-SAM | Rilevamento di delaminazione/vuoti | 50 nm | Flip-chip, BGA | Richiede accoppiamento liquido |

| Tomografia computerizzata a raggi X 3D | Ispezione TSV/die impilati | 100 nm | Circuiti integrati 3D | Costo elevato per un'alta risoluzione |

| Termografia lock-in | mappatura termica a temperature inferiori a °C | 0,1 °C | Circuiti integrati di potenza (IGBT) | Tempo di scansione lento |

| SEM/EDS | Caratterizzazione dei materiali, imaging dei difetti | 1-5 nm | Analisi fisica a livello di chip | Richiede un rivestimento conduttivo per gli isolanti |

| FIB-SEM | Sezionamento trasversale, modifica del circuito | 5 nm | Circuiti integrati 3D, packaging avanzato | Distruttivo, richiede molto tempo |

Guida all'abbinamento strumento-tecnica

Abbinare gli strumenti giusti a specifici scenari di guasto garantisce un'analisi delle cause profonde efficiente e accurata:

Analisi dei danni da scariche elettrostatiche

- Inizia con EMMI per individuare i punti di perdita

- Successivamente, si procede con la microscopia elettronica a scansione con fascio ionico focalizzato (FIB-SEM) per l'imaging su scala nanometrica dei danni.

- Utilizzare l'EDS per verificare la presenza di contaminazione nei punti di guasto.

- Verificare con test elettrici (analisi della curva I-V)

Fratture TSV nei circuiti integrati 3D

- Utilizzare la tomografia computerizzata a raggi X 3D per l'ispezione non distruttiva.

- Convalidare con sezioni trasversali FIB in punti critici

- Eseguire immagini SEM per caratterizzare la morfologia delle crepe

- Applicare l'analisi agli elementi finiti per determinare le origini delle sollecitazioni.

Guasti di natura termica

- Iniziate con la termografia lock-in per la mappatura termica.

- Utilizzare C-SAM per verificare la delaminazione dovuta a stress termico.

- Eseguire un'analisi di sezione trasversale per esaminare l'integrità del giunto di saldatura.

- Convalidare con test di cicli termici

Guasti intermittenti

- Utilizzare una camera climatica per riprodurre le condizioni di guasto.

- Applicare OBIRCH per l'analisi dinamica del percorso di corrente.

- Utilizzare la termografia durante i test di stress.

- Verificare con test di vibrazione se si sospetta una sollecitazione meccanica.

Strumenti e tecnologie emergenti

EMMI potenziato dall'intelligenza artificiale

Algoritmi di apprendimento automatico che distinguono automaticamente i modelli di emissione di fotoni normali da quelli anomali, riducendo i tempi di analisi fino al 70%.

Etichettatura a punti quantici

Marcatori fluorescenti su scala nanometrica che evidenziano le regioni difettose nei semiconduttori, consentendo un rilevamento più precoce dei potenziali punti di guasto.

Piattaforme FA predittive

Sistemi integrati che combinano dati di produzione, segnalazioni di guasti sul campo e intelligenza artificiale per prevedere i potenziali meccanismi di guasto prima che si verifichino.

Standard e conformità

Standard JEDEC

JESD22-A121: Test ESD

Definisce le procedure per i test di scarica elettrostatica su modello del corpo umano (HBM), modello della macchina (MM) e modello del dispositivo carico (CDM).

JESD47: Metodi di prova di stress per circuiti integrati

Standard completo che copre vari test di stress, tra cui cicli termici, tensione-temperatura, elettromigrazione e rottura dielettrica dipendente dal tempo.

JESD22-A104: Ciclo termico

Norma specifica per le prove di cicli termici al fine di valutare l'affidabilità dei componenti in condizioni di stress termico.

Standard specifici di settore

AEC-Q100: Circuiti integrati per applicazioni automobilistiche

Specifiche di qualificazione per circuiti integrati utilizzati in applicazioni automobilistiche, con rigorosi requisiti di affidabilità.

DO-254: Avionica aerospaziale

Linee guida per la garanzia della progettazione di hardware elettronico di bordo, compresi i circuiti integrati utilizzati nei sistemi critici per il volo.

Telcordia GR-468: Telecomunicazioni

Requisiti per la garanzia di affidabilità dei dispositivi a semiconduttore utilizzati nelle apparecchiature di telecomunicazione.

Analisi dei dati di affidabilità

Un'analisi efficace dei guasti richiede un'analisi statistica dei dati di affidabilità per comprendere la distribuzione dei guasti e prevedere la durata di vita del prodotto:

Distribuzioni dei guasti

- Distribuzione log-normale: comune per i guasti dei semiconduttori

- Distribuzione di Weibull: utile per analizzare guasti precoci, casuali e dovuti all'usura.

- Distribuzione esponenziale: adatta per regioni con tasso di guasto costante.

Indicatori chiave

- MTBF (tempo medio tra i guasti)

- Tasso di guasto (λ) - tipicamente espresso in FIT (Failures In Time: 1 FIT = 1 guasto ogni 10^9 ore-dispositivo)

- Fattori di conversione per i test di vita accelerati (ALT)

Esempio di analisi del tasso di guasto

Tendenze future nell'analisi dei guasti dei circuiti integrati

Nodi di processo avanzati (2 nm/1 nm)

Analisi di sfide a livello atomico con effetti quantistici che diventano fattori significativi nei meccanismi di guasto.

Sfide principali

- • Effetti di tunneling quantistico

- • Difetti di alimentazione dal lato posteriore

- • Rilevamento della contaminazione a livello atomico

Soluzioni emergenti

- • Microscopia elettronica a trasmissione criogenica per l'ispezione a livello atomico

- • Tecniche di nanosondaggio guidate dall'intelligenza artificiale

- • Tomografia avanzata con sonda atomica

Circuiti integrati 3D e integrazione eterogenea

Modalità di guasto complesse nelle architetture a chip sovrapposti che richiedono nuove tecniche di analisi non distruttiva.

Sfide principali

- • Cracking dei TSV (Through-Silicon Via)

- • Delaminazione del materiale di riempimento in stampi impilati

- • Problemi di gestione termica

Soluzioni emergenti

- • Tomografia computerizzata a raggi X 3D avanzata ad alta risoluzione

- • Tecniche di imaging multimodale

- • Progettazione orientata alla testabilità nei circuiti integrati 3D

Intelligenza artificiale e apprendimento automatico

Rilevamento e classificazione automatizzati dei guasti per gestire la crescente complessità dei circuiti integrati.

Applicazioni chiave

- • Classificazione automatizzata dei difetti nelle immagini SEM

- • Analisi predittiva dei guasti a partire dai dati di produzione

- • Rilevamento di anomalie nei dati di test dei wafer

Benefici

- • Riduzione del 50-70% dei tempi di analisi

- • Maggiore accuratezza nell'identificazione delle cause profonde

- • Previsione tempestiva dei guasti prima dell'impiego sul campo