Di antara instrumen pintar, konverter ADC dan DAC memainkan peran yang sangat penting. Kita tahu bahwa mikroprosesor yang saat ini banyak digunakan hanya dapat memproses sinyal digital diskrit. Tanpa ADC, tidak mungkin memasukkan sinyal analog kontinu dari dunia fisik ke dalam mikroprosesor. Selain itu, tanpa DAC, tidak mungkin mengeluarkan sinyal analog dari mikroprosesor. (klik di sini untuk mempelajari lebih lanjut tentang sinyal digital dan sinyal analog)

Konverter analog ke digital (ADC)

Definisi ADC

Dalam sistem instrumentasi, seringkali diperlukan untuk mengubah besaran analog yang terus berubah, seperti suhu, tekanan, laju aliran, kecepatan, intensitas cahaya, dan sebagainya, menjadi besaran digital diskrit sebelum dimasukkan ke dalam komputer untuk diproses. Besaran analog ini diubah menjadi sinyal listrik (biasanya sinyal tegangan) oleh sensor, dan setelah diperkuat oleh penguat, sinyal tersebut perlu melalui proses tertentu agar menjadi besaran digital. Perangkat yang mengubah sinyal analog menjadi digital biasanya disebut konverter analog-ke-digital (ADC), atau disingkat A/D.

Prinsip kerja ADC

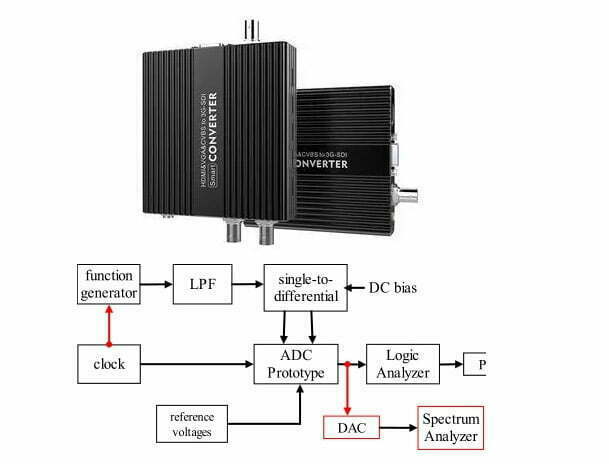

Dalam keadaan normal, konversi A/D umumnya harus melalui empat tahap, yaitu pengambilan sampel, penahanan, kuantisasi, dan pengkodean.

Pengambilan sampel dan penyimpanan

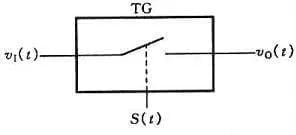

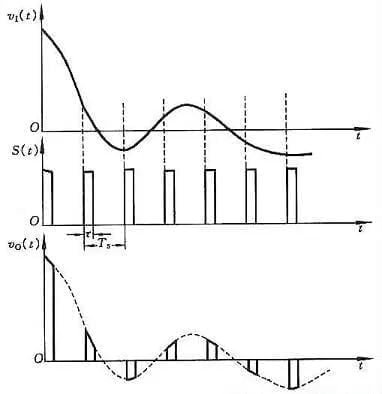

Pengambilan sampel adalah proses mengubah besaran analog yang berubah secara kontinu seiring waktu menjadi besaran analog diskrit waktu. Diagram skematik proses pengambilan sampel ditunjukkan pada Gambar 1. Gambar (a) adalah struktur rangkaian pengambilan sampel, di mana gerbang transmisi dikendalikan oleh sinyal pengambilan sampel S(t); selama lebar pulsa τ dari S(t), gerbang transmisi diaktifkan, sinyal keluaran vO(t) sama dengan sinyal masukan v1, dan selama (Ts-τ), gerbang transmisi ditutup sehingga sinyal keluaran vO(t) = 0. Bentuk gelombang sinyal dalam rangkaian ditunjukkan pada Gambar (b).

Dari analisis tersebut dapat dilihat bahwa semakin tinggi frekuensi sinyal sampling S(t), semakin akurat sinyal yang diperoleh dalam mereproduksi sinyal masukan setelah melewati filter low-pass. Namun, masalahnya adalah jumlah data akan bertambah. Untuk memastikan frekuensi sampling yang tepat, frekuensi tersebut harus memenuhi teorema sampling.

Teorema sampling: Misalkan frekuensi sinyal sampling S(t) adalah fs, dan frekuensi komponen frekuensi tertinggi dari sinyal analog masukan v1(t) adalah fimax, maka fs dan fimax harus memenuhi hubungan berikut: fs ≥ 2fimax, dan dalam praktik teknik, fs umumnya diambil sebesar (3–5) kali fimax.

Diperlukan waktu tertentu untuk mengubah sinyal analog yang diperoleh dari sirkuit sampling menjadi sinyal digital setiap kali. Untuk memberikan nilai yang stabil bagi proses kuantisasi dan pengkodean selanjutnya, sinyal analog yang diperoleh setiap kali harus ditahan selama periode tertentu oleh sirkuit penahan.

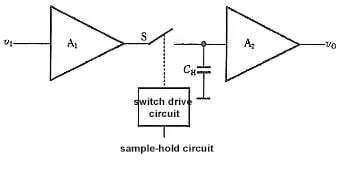

Proses pengambilan sampel dan penahanan sering kali diselesaikan secara bersamaan melalui sirkuit pengambilan sampel-penahanan. Diagram skematik dan bentuk gelombang keluaran dari sirkuit pengambilan sampel-penahanan ditunjukkan pada Gambar 2.

Rangkaian ini terdiri dari penguat masukan A1, penguat keluaran A2, kapasitor penahan CH, dan rangkaian penggerak sakelar. A1 harus memiliki impedansi masukan yang tinggi dalam rangkaian ini untuk mengurangi pengaruhnya terhadap sumber sinyal masukan. Agar muatan yang tersimpan pada CH sulit terlepas selama fase penahanan, A2 juga harus memiliki impedansi masukan yang tinggi, serta impedansi keluaran yang rendah, yang dapat meningkatkan kapasitas beban rangkaian. Secara umum, juga diperlukan agar AV1·AV2=1 dalam rangkaian.

Sekarang, dengan mengacu pada Gambar 2, mari kita analisis prinsip kerja sirkuit sample-hold. Pada t=t0, saklar S ditutup, dan kapasitor terisi dengan cepat. Karena AV1 · AV2=1, v0=vI, periode pengambilan sampel terjadi pada interval waktu t0~t1. Pada waktu t=t1, S diputus. Jika impedansi masukan A2 tak terhingga dan S adalah saklar ideal, dapat dianggap bahwa kapasitor CH tidak memiliki sirkuit pelepasan, dan tegangan di kedua ujungnya tetap konstan pada v0. Bagian datar dari t1 hingga t2 pada Gambar 11.8.2(b) adalah tahap penahanan.

Sirkuit sample-hold dapat diproduksi oleh berbagai jenis sirkuit terpadu monolitik. Misalnya, terdapat AD585 dan AD684 untuk teknologi bipolar; AD1154 dan SHC76 untuk teknologi campuran.

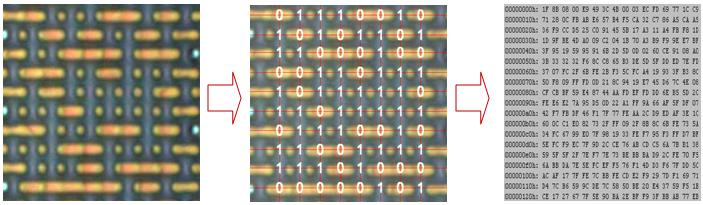

Kuantisasi dan pengkodean

Sinyal digital tidak hanya bersifat diskrit dalam hal waktu, tetapi juga tidak kontinu dalam hal amplitudo. Besarnya suatu besaran digital hanya dapat berupa kelipatan bilangan bulat dari satuan besaran minimum yang ditentukan. Untuk mengubah sinyal analog menjadi besaran digital, dalam proses konversi A/D, tegangan keluaran rangkaian sample-hold juga harus dinormalisasi ke tingkat diskrit yang sesuai dengan cara perkiraan tertentu. Proses konversi ini disebut kuantisasi. Kuantifikasi, disebut sebagai kuantisasi. Nilai yang telah dikuantisasi akhirnya perlu direpresentasikan oleh sebuah kode melalui proses pengkodean. Kode yang diperoleh setelah pengkodean adalah besaran digital yang dihasilkan oleh konverter A/D.

Satuan kuantitas terkecil yang diambil dalam proses kuantisasi disebut satuan kuantisasi, dilambangkan dengan △. Ini adalah besaran analog yang sesuai ketika bit terendah dari sinyal digital adalah 1, yaitu 1LSB.

Dalam proses kuantisasi, karena tegangan sampel tidak selalu dapat dibagi dengan △, maka pasti terdapat kesalahan sebelum dan sesudah kuantisasi. Kesalahan ini disebut kesalahan kuantisasi dan dilambangkan dengan ε. Kesalahan kuantisasi merupakan kesalahan prinsipil yang tidak dapat dihilangkan. Semakin banyak bit yang dimiliki konverter A/D, semakin kecil selisih antara tingkat diskrit dan semakin kecil pula kesalahan kuantisasi.

Dua metode kuantisasi perkiraan sering digunakan dalam proses kuantisasi: kuantisasi pembulatan dan kuantisasi pembulatan.

hanya membulatkan ke atas pada metode kuantisasi

Ambil contoh konverter A/D 3-bit, misalkan sinyal masukan v1 berkisar antara 0 hingga 8 V. Saat menggunakan metode kuantisasi pembulatan ke atas, ambil △=1 V, dan buang bagian yang nilainya kurang dari satu unit kuantisasi. Jika nilainya berada antara 0 dan 8 V, tegangan analog antara 0 dan 1 V dianggap sebagai 0△, yang diwakili oleh bilangan biner 000, dan tegangan analog antara 1 V dan 2 V dianggap sebagai 1△, yang diwakili oleh bilangan biner 001… Kesalahan maksimum dari metode kuantisasi ini adalah △.

metode pembulatan kuantisasi

Jika metode kuantisasi pembulatan diterapkan, maka digunakan satuan kuantisasi △=8V/15; bagian yang nilainya kurang dari setengah satuan kuantisasi akan dibuang selama proses kuantisasi, sedangkan bagian yang nilainya sama dengan atau lebih besar dari setengah satuan kuantisasi akan dianggap sebagai satu satuan kuantisasi. Metode ini memperlakukan tegangan analog antara 0 ~ 8V/15 sebagai 0△, yang diwakili oleh bilangan biner 000, dan tegangan analog antara 8V/15 ~ 24V/15 dianggap sebagai 1△, yang diwakili oleh bilangan biner 001.

Perbandingan

Kesalahan kuantisasi maksimum│εmax│=1LSB pada metode kuantisasi pertama yang hanya menggunakan pembulatan, sedangkan pada metode kuantisasi kedua yang menggunakan pembulatan dan pembulatan ulang, kesalahan kuantisasi│εmax│=1LSB/2. Kesalahan kuantisasi pada metode kedua lebih kecil daripada metode pertama, sehingga metode ini lebih banyak digunakan pada konverter A/D.

Seiring dengan perkembangan pesat sirkuit terpadu, ide-ide desain dan teknik manufaktur baru untuk konverter A/D terus bermunculan tanpa henti. Konverter A/D dengan struktur dan kinerja yang berbeda dirancang untuk memenuhi berbagai kebutuhan deteksi dan pengendalian.

Jenis-jenis ADC

Mengintegrasikan ADC

prinsip konversi

Prinsip konversi integrasi ADC didasarkan pada integrasi tegangan dan perbandingan tegangan hasil integrasi tersebut dengan tegangan lain untuk mengontrol nilai hitung, dan nilai hitung yang dihasilkan merupakan keluaran ADC. Objek integrasi dapat didasarkan pada tegangan referensi, atau didasarkan pada tegangan referensi dan tegangan masukan.

Kelebihan dan Kekurangan

Keunggulan:

- ADC terintegrasi ini memiliki resolusi tinggi, dan jumlah digitnya bisa mencapai 12 atau bahkan lebih.

- Linearitasnya sangat baik. Pada dasarnya, input dibandingkan dengan tegangan referensi terintegrasi untuk menentukan output, sehingga linearitas akan bergantung pada akurasi komparator.

- Topologi realisasi sirkuitnya sederhana, dan komponen yang digunakan untuk merealisasikan perangkat ini relatif sedikit, sehingga sirkuitnya relatif sederhana dan biaya produksinya rendah.

Kekurangan:

- Kelemahan utamanya adalah kecepatan konversi yang lambat. Pada ADC N-bit, keluaran mungkin memerlukan hingga 2N siklus jam untuk mengonversi satu titik sampel.

Aplikasi

Umumnya digunakan dalam aplikasi sensor dan perangkat seperti voltmeter dan amperemeter, di mana akurasi lebih diutamakan daripada kecepatan. Dengan kata lain, kecepatan pengambilan sampel pada ADC integral relatif rendah, namun akurasinya sangat tinggi.

klasifikasi

Ada berbagai jenis ADC integral, dan yang umum digunakan adalah ADC integral lereng tunggal dan ganda. Menambahkan "lereng" meningkatkan presisi, namun hal ini mengorbankan waktu konversi.

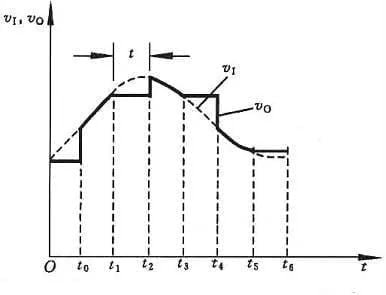

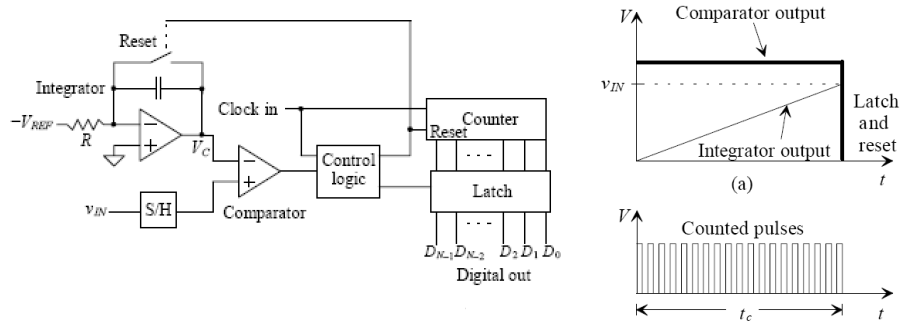

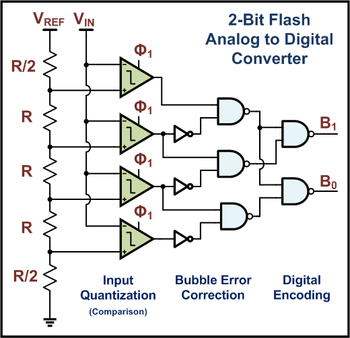

ADC integral lereng tunggal

Komparator membandingkan tegangan masukan dengan nilai tegangan referensi terintegrasi (perhatikan bahwa kita akan menjadikannya negatif karena terhubung ke input invers penguat operasional). Secara bersamaan, hitung jumlah siklus jam. Ketika keluaran integrator sama, komparator mengeluarkan sinyal logika "0", yang memicu reset pada penghitung dan integrator, dan latch menahan keluaran digital.

VINVREFVrefVrefVin

Ini adalah waktu konversi. Saya tahu mengapa ADC integral ini lambat. Mari kita lihat kasus terburuk, dengan asumsi tegangan masukan , dengan asumsi , dengan asumsi ini adalah ADC 20-bit, maka!

VIN=VREFTCLK=1ustc=220us=1048576us

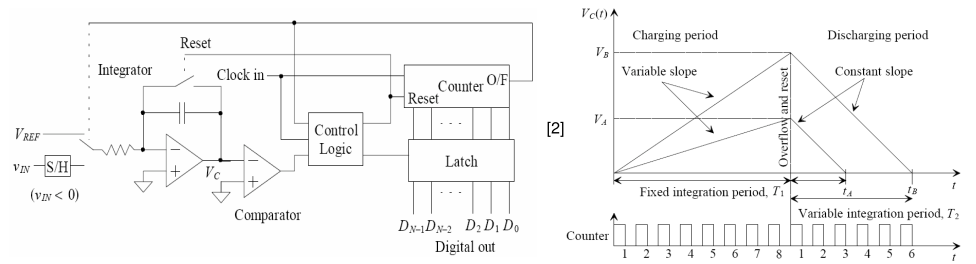

ADC integral lereng tunggal

ADC lereng ganda berbeda dengan ADC lereng tunggal karena perbandingan terhadap ground kini dilakukan dan dua jumlah tegangan diintegrasikan. Awalnya, input negatif dihubungkan ke integrator, yang naik secara bertahap hingga penghitung meluap. Karena integrasi pada input invers menghasilkan nilai negatif, keluaran integrator akan selalu positif dan lebih besar dari nol, sehingga penghitung akan terus berjalan hingga meluap, yang membutuhkan 2N siklus jam (=T1).

VCVREFVINVC

Pada waktu T2, nilainya akan sama dengan jumlah dari dan, dan

VC = VC1 + VC2 = 0

Tetapi:

VIN/VREF = T2/T1

Oleh karena itu, berdasarkan prinsip konversi ADC, ADC dual-slope bekerja lebih lambat daripada ADC single-slope, karena proses integrasi dilakukan dua kali; kesalahan yang terkait dengan kemiringan integrator akan saling meniadakan, sehingga secara prinsip meningkatkan akurasi.

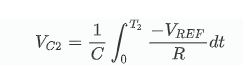

ADC Sigma-Delta Σ-Δ

Dimulai dari masukan, penguat selisih menghasilkan keluaran yang merupakan selisih antara Vin dan keluaran DAC 1-bit. Keluaran DAC 1-bit dapat berupa salah satu dari dua nilai: ATAU . Dalam topologi ini, integrator dapat dipandang sebagai penghitungan rata-rata bergerak dari nilai sebelumnya dan nilai masukan saat ini.

–Vref+Vref

Oleh karena itu, dengan asumsi bahwa segmen positif komparator pada awalnya ditetapkan pada nilai kecil di atas 0V, komparator akan berbalik. Nilainya akan menjadi tinggi atau 1. Kemudian, keluaran DAC akan menjadi . Pada iterasi berikutnya, nilai ini akan dikurangkan dari nilai saat ini sebesar . Karena nilai sebelumnya adalah 0V, keluaran integrator sekarang akan menjadi – Vref. Pada titik ini, keluaran komparator akan menjadi 0 dan keluaran DAC akan menjadi.

+VrefVin-Vref

Pada sampel berikutnya, keluaran integrator akan menjadi 0 karena nilai sebelumnya, dan penguat selisih akan benar-benar mengurangkan , sehingga menambah ke . Keluaran komparator akan menjadi 1.

-Vref – Vref + VrefVin

Proses ini berlanjut secara berulang, sehingga untuk input 0V, keluaran komparator akan menjadi aliran stabil 101010…. Ingat bahwa logika 1 berarti , logika 0 berarti , jadi jika N sampel diambil dan dirata-ratakan, mudah untuk melihat bahwa nilai rata-ratanya adalah 0V. Blok pemrosesan setelah komparator hanya akan mengeluarkan ini sebagai nilai tunggal 0000…, dengan asumsi nilai referensi ( ~ ) atau 2 x.

+Vref-Vref-Vref+VrefVref

Sekarang, dengan asumsi 1V, ini adalah ADC 5V. adalah ±2,5V. Dengan mengikuti langkah-langkah yang sama seperti sebelumnya secara berulang, outputnya akan menjadi: 1011101… Outputnya adalah 1,07V.

Vin±Vref

Singkatnya:

ADC sigma-delta melakukan oversampling terhadap sinyal yang diproses (lihat "How Analog-to-Digital Sampling" untuk konsep ini) dan menyaring sinyal tersebut dengan filter low-pass. Biasanya, jumlah bit yang dikonversi menggunakan Flash ADC setelah penyaringan lebih sedikit daripada jumlah bit yang dibutuhkan. Sinyal hasil konversi, beserta kesalahan dari tingkat diskrit FLASH, dikembalikan (feedback) dan dikurangkan dari sinyal masukan, lalu disalurkan ke filter. Umpan balik negatif ini meredam noise sehingga tidak muncul pada frekuensi sinyal yang diinginkan. Filter digital setelah ADC (menggunakan filter decimation) mengurangi laju sampling, menyaring sinyal noise yang tidak diinginkan, dan meningkatkan resolusi output (karena itulah dinamakan modulasi sigma-delta, juga dikenal sebagai modulasi delta-sigma).

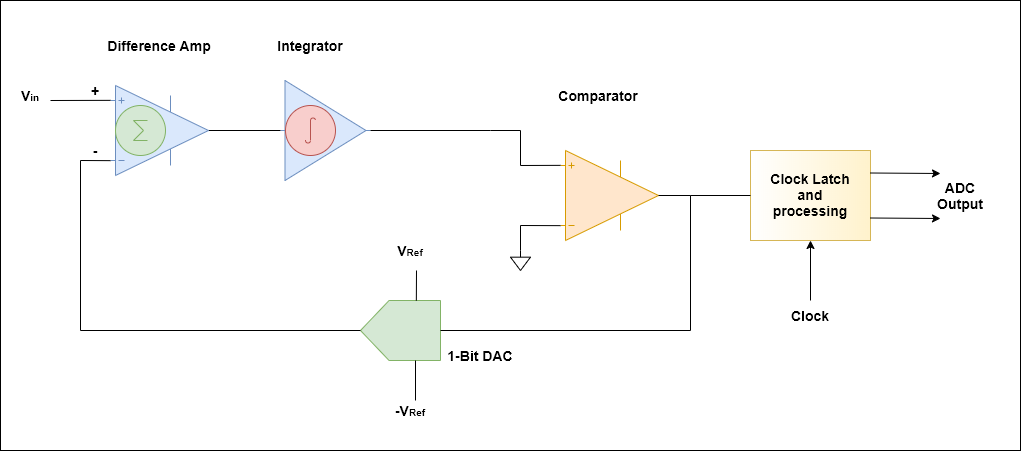

Flash ADC (tipe perbandingan langsung)

Prinsip kerja FLASH ADC mungkin merupakan yang paling mudah dipahami. Gambar di bawah ini adalah diagram skematik dari ADC dua bit, yang terdiri dari banyak komparator, masing-masing dilengkapi dengan tegangan referensi yang nilainya satu bit lebih tinggi daripada nilai referensi sebelumnya. Oleh karena itu, untuk ADC 8 bit, diperlukan 256 komparator semacam itu. Untuk 10 bit, Anda memerlukan 1024 komparator.

LASH ADC (tipe perbandingan langsung) bekerja dengan cepat. Alat ini langsung mengonversi sinyal masukan tanpa proses pengambilan sampel atau pemrosesan lanjutan yang rumit. Masalahnya, LASH ADC membutuhkan banyak komparator, dan banyaknya komparator tersebut memakan banyak ruang silikon pada chip. Oleh karena itu, gunakan LASH ADC hanya jika Anda membutuhkan kecepatan yang sangat tinggi yang tidak dapat dicapai dengan implementasi ADC lainnya.

Dikotomi yang terwujud dalam perangkat keras

Dalam penerapan praktis, terdapat varian lain yang lebih umum digunakan, yaitu semi-FLASH ADC. Alat ini menggunakan proses dua tahap untuk mengurangi jumlah konverter yang diperlukan dalam rantai konversi sebenarnya:

Pertama, sinyal masukan dibandingkan dengan sekumpulan level yang tepat berada di tengah. Jika sinyal lebih rendah, maka bit paling signifikan (MSB) disetel ke 0 dan sinyal masukan diteruskan ke rantai komparator dengan tegangan referensi yang disetel untuk mengonversi sisa bit.

Jika sinyal masukan berada di atas , atur MSB menjadi 1, kurangi dari sinyal masukan . Rantai komparator digunakan kembali untuk mendapatkan bit-bit yang tersisa. Jadi, pada dasarnya, FLASH ADC setengah langkah mengorbankan satu perbandingan tambahan untuk menghemat setengah dari jumlah komparator. Pemikiran semacam ini juga dapat terus dikembangkan dan diperluas, seperti FLASH ADC 4-titik dan seterusnya

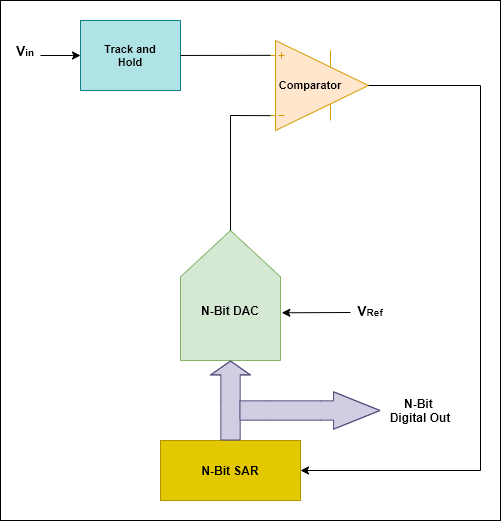

Register Aproksimasi Berurutan (SAR)

Register Aproksimasi Berurutan (SAR) merupakan bagian integral dari ADC aproksimasi berurutan. SAR bekerja dengan memanfaatkan komparator untuk secara bertahap mempersempit area yang mencakup tegangan masukan. Untuk melakukannya, konverter membandingkan tegangan masukan dengan keluaran konverter digital-ke-analog, yang biasanya menunjukkan titik tengah rentang tegangan yang dipilih. Pada setiap langkah proses, hasil perkiraan disimpan dalam SAR.

Misalnya, anggaplah tegangan masukan adalah 6,3 V dan rentang awal adalah 0 hingga 16 V.

- Pada langkah pertama, masukkan 6,3 V untuk dibandingkan dengan 8 V (titik tengah rentang 0–16 V). Komparator melaporkan bahwa tegangan masukan kurang dari 8 V, sehingga SAR diperbarui untuk mempersempit rentang menjadi 0–8 V.

- Pada langkah kedua, tegangan masukan dibandingkan dengan 4 V (titik tengah rentang 0–8 V); komparator melaporkan bahwa tegangan masukan lebih besar dari 4 V, sehingga SAR diperbarui untuk mencerminkan bahwa tegangan masukan berada dalam rentang 4–8 V.

- Pada langkah ketiga, tegangan masukan dibandingkan dengan 6 V (setengah dari rentang 4 V hingga 8 V); komparator melaporkan tegangan masukan lebih besar dari 6 V, dan rentang pencarian menjadi 6–8 V.

Lanjutkan langkah-langkah ini hingga mencapai solusi yang diinginkan. Topologinya adalah sebagai berikut:

Untuk memahami secara intuitif, lihat animasi berikut ini:

ADC Berurutan

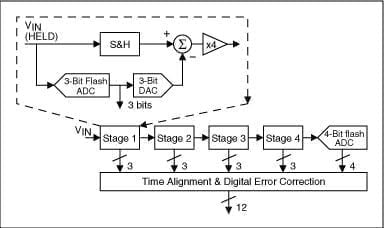

ADC pipelined (juga dikenal sebagai kuantizer subrutin) menggunakan dua atau lebih jalur pipelined. Pertama, dilakukan konversi kasar. Pada langkah kedua, digunakan konverter digital-ke-analog (DAC) untuk menentukan selisih sinyal masukan. Selisih ini kemudian dikonversi menjadi nilai-nilai yang lebih halus, dan hasilnya digabungkan pada langkah terakhir. Hal ini dapat dianggap sebagai peningkatan dibandingkan dengan ADC pendekatan berturut-turut, di mana sinyal referensi umpan balik terdiri dari transisi-transisi antara di seluruh rentang bit (misalnya, 4 bit), bukan hanya bit paling signifikan berikutnya. Dengan menggabungkan keunggulan metode pendekatan berturut-turut dan ADC flash, jenis ini memiliki keunggulan berupa kecepatan tinggi, resolusi tinggi, dan ukuran cetakan yang kecil.

Dalam skema ini, sinyal masukan analog VIN terlebih dahulu diambil sampelnya dan dipertahankan nilainya oleh sirkuit sample-and-hold (S&H), sementara ADC flash pada tahap pertama mengkuantisasi sinyal tersebut menjadi tiga bit. Output 3-bit tersebut kemudian disalurkan ke DAC 3-bit (akurasi 12-bit) dan output analognya dikurangkan dari input. "Sisa" ini diperbesar dengan faktor 4 dan dikirim ke tahap berikutnya (tahap 2). Sisa yang ditambahkan ini terus melewati tahap-tahap bawah pipa, memberikan 3 bit per tahap, hingga mencapai ADC flash 4-bit, yang akan menentukan 4 bit LSB akhir. Karena bit untuk setiap tahap ditentukan pada titik waktu yang berbeda, semua bit yang sesuai dengan sampel yang sama diselaraskan waktu dengan register geser sebelum dikirim ke logika koreksi kesalahan digital. Perhatikan bahwa ketika sebuah pipa telah selesai memproses sampel masukan, menentukan bit akuisisi untuk pipa ini, dan meneruskan sisa ke pipa berikutnya, pipa tersebut dapat mulai memproses sampel berikutnya yang diterima dari penahan sampel yang tertanam di setiap pipa. Pipa ini adalah alasan di balik throughput yang tinggi, yang juga merupakan konsep pipa.

Lainnya

Selain beberapa jenis ADC umum di atas, terdapat pula ADC berbasis prinsip keseimbangan muatan, ADC pembagian waktu, ADC FM, ADC perpanjangan waktu, ADC pengkodean inkremental, ADC Wilkinson, dan sebagainya.

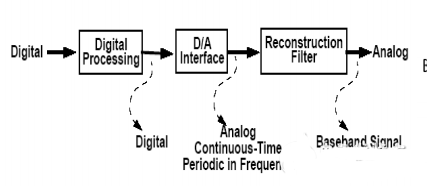

Konverter Digital ke Analog (DAC)

Definisi DAC

Kuantitas digital yang diproses oleh sistem digital terkadang perlu diubah menjadi kuantitas analog agar dapat digunakan secara praktis. Konversi ini disebut "konversi digital-ke-analog". Sirkuit yang melakukan konversi digital-ke-analog ini disebut konverter digital-ke-analog, atau disingkat DAC (Digital to Analog Converter).

Parameter DAC

Keputusan

Resolusi pada DAC didefinisikan sebagai jumlah tingkat analog keluaran yang mungkin terjadi berdasarkan nilai kode digital masukan yang berbeda-beda. Resolusi N-bit berarti DAC dapat menghasilkan 2^(N−1) tingkat analog yang berbeda. Secara umum, hal ini mengacu pada jumlah digit dari kode digital masukan.

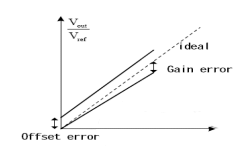

Kesalahan offset dan gain

Offset didefinisikan sebagai nilai sinyal analog keluaran aktual ketika nilai kode 0 dimasukkan, sedangkan kesalahan penguatan didefinisikan sebagai selisih antara nilai keluaran skala penuh ideal dan nilai keluaran aktual setelah dikurangi offset, seperti yang ditunjukkan pada gambar.

Ketepatan

Ketepatan pada DAC dibagi menjadi ketepatan absolut dan ketepatan relatif. Ketepatan absolut didefinisikan sebagai selisih antara keluaran ideal dan keluaran aktual, termasuk berbagai kesalahan offset dan non-linear. Ketepatan relatif didefinisikan sebagai kesalahan non-linear integral maksimum. Ketepatan dinyatakan sebagai rasio dari skala penuh, yang diungkapkan dalam digit efektif. Misalnya, akurasi 8-bit berarti bahwa kesalahan DAC kurang dari 1/8 dari keluaran skala penuh DAC. Perlu dicatat bahwa konsep presisi tidak terkait dengan resolusi. DAC dengan resolusi 12-bit mungkin hanya memiliki presisi 10-bit; dan DAC dengan resolusi 10-bit mungkin memiliki presisi 12-bit. Akurasi yang lebih tinggi daripada resolusi berarti bahwa respons transmisi DAC dapat dikendalikan dengan lebih tepat.

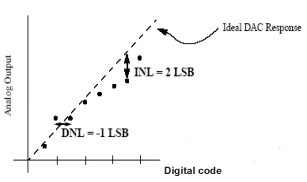

INL—Nonlinearitas Integral

Setelah kesalahan offset dan gain dihilangkan, kesalahan linearitas integral didefinisikan sebagai penyimpangan karakteristik transfer keluaran aktual dari karakteristik transfer ideal (garis lurus), seperti yang ditunjukkan pada gambar.

DNL-Nonlinearitas Diferensial

Pada DAC ideal dengan minimal 1 LSB per perubahan keluaran analog, kesalahan linearitas diferensial didefinisikan sebagai penyimpangan dari 1 LSB per perubahan keluaran analog terkecil (tidak termasuk kesalahan gain dan offset). DNL yang kami definisikan berlaku untuk setiap nilai kode masukan digital, dan terkadang DNL terbesar digunakan untuk mendefinisikan DNL dari seluruh DAC. Sebuah DAC ideal akan memiliki kesalahan linearitas diferensial nol untuk setiap masukan digital, sedangkan DAC dengan DNL maksimum 0,5 LSB akan memiliki perubahan keluaran minimum antara 0,5 LSB dan 1,5 LSB per keluaran. Kesalahan linearitas integral dan diferensial dari DAC ditunjukkan pada gambar.

Energi jitter (Area Impuls Glitch)

Luas maksimum di bawah kurva jitter yang muncul pada keluaran setelah sinyal masukan berubah.

Waktu Penyelesaian

Waktu penyetelan berada dalam rentang kesalahan tertentu dari nilai akhir, dan merupakan waktu yang diperlukan agar keluaran mencapai konversi skala penuh.

Monotonisitas DAC monoton adalah DAC yang tingkat analog outputnya selalu meningkat seiring dengan meningkatnya nilai kode digital input. Jika DNL maksimum dikendalikan dalam 0,5LSB, maka monotonisitas DAC dapat dijamin secara alami.

Rentang Dinamis Bebas Gangguan (SFDR) SFDR adalah Rentang Dinamis Bebas Gangguan, yaitu rentang dinamis tanpa noise dan harmonik. Baik noise maupun harmonik disebut sinyal gangguan.

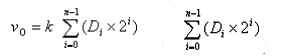

Prinsip DAC

Ubah setiap kode biner masukan menjadi besaran analog yang sesuai berdasarkan bobotnya, lalu tambahkan besaran-besaran analog yang mewakili setiap bit; besaran analog total yang diperoleh sebanding dengan besaran digital, sehingga mewujudkan konversi dari besaran digital ke besaran analog.

Ini adalah nilai desimal yang diubah menjadi bilangan biner melalui perluasan bobot bit.

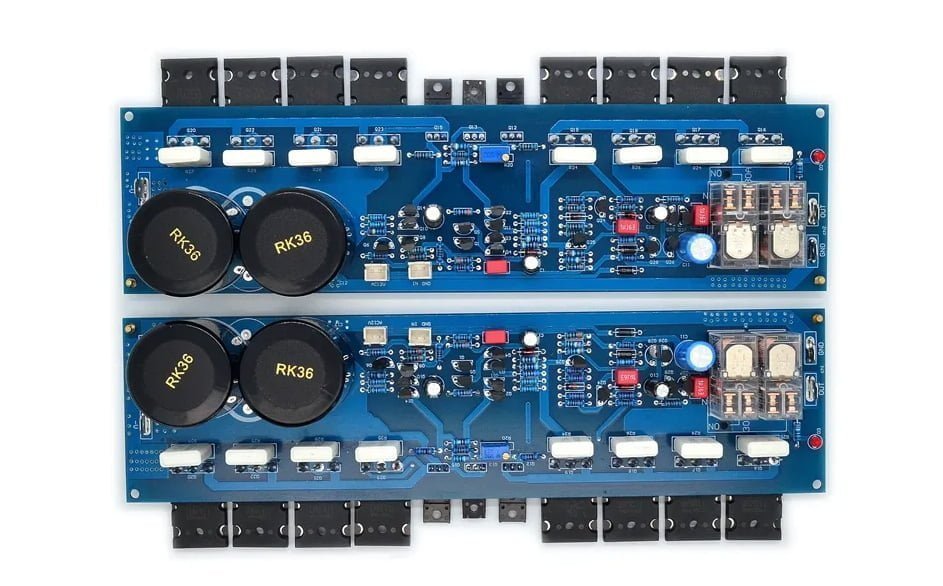

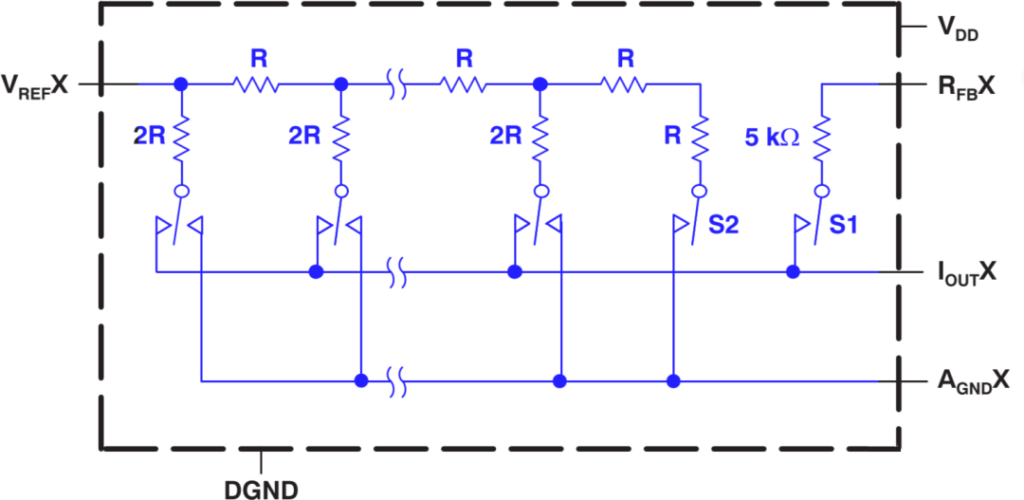

Komposisi dan karakteristik DAC

DAC terutama terdiri dari register digital, sakelar elektronik analog, jaringan bobot bit, penguat operasional penjumlah, dan sumber tegangan referensi (atau sumber arus konstan). Gunakan digit dari besaran digital yang disimpan dalam register digital untuk mengontrol sakelar elektronik analog dari masing-masing digit yang sesuai, sehingga digit dengan angka 1 menghasilkan nilai arus yang sebanding dengan bobot digitnya pada jaringan bobot digit, dan kemudian penguat operasional mengontrol setiap nilai arus yang dijumlahkan dan diubah menjadi nilai tegangan.

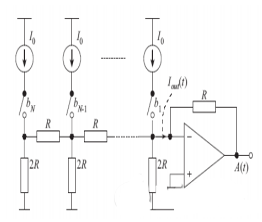

Jaringan bobot bit yang bervariasi memungkinkan perakitan berbagai jenis DAC, termasuk DAC jaringan resistor bobot, DAC jaringan resistor berbentuk T terbalik R-2R, dan DAC jaringan arus nilai tunggal, dll. Ketepatan konversi yang dihasilkan oleh DAC jaringan resistor bobot bergantung pada akurasi tegangan referensi VREF, serta kualitas sakelar elektronik analog, penguat operasional, dan nilai resistor bobot. Kekurangannya adalah nilai resistansi setiap resistor bobot berbeda-beda, dan ketika jumlah digit banyak, nilai resistansi tersebut sangat bervariasi, yang menimbulkan kesulitan besar dalam memastikan akurasi, terutama untuk produksi sirkuit terpadu. Oleh karena itu, dalam sirkuit DAC terpadu, sirkuit ini jarang digunakan secara mandiri.

Indikator teknis utama DAC

Akurasi dan kecepatan konversi DAC: Akurasi konversi pada DAC umumnya dijelaskan melalui resolusi dan kesalahan konversi.

Keputusan

Secara umum, jumlah bit pada DAC digunakan untuk mengukur resolusi, karena semakin besar jumlah bit, semakin banyak nilai (2^n) tegangan keluaran vO, dan semakin baik pula kemampuannya dalam mencerminkan perubahan-perubahan halus pada tegangan keluaran.

Selain itu, resolusi juga dapat didefinisikan sebagai rasio antara tegangan keluaran minimum 1 LSB yang dapat dibedakan oleh DAC terhadap tegangan keluaran maksimum FSR. Yaitu:

resolusi = 1LSB/FSR = k/(2n-1) = 1/(2n-1)

Semakin kecil nilainya, semakin tinggi resolusinya.

Kesalahan konversi

Kesalahan konversi adalah selisih maksimum antara tegangan analog keluaran aktual dan nilai ideal. Biasanya dinyatakan dalam bentuk persentase atau beberapa LSB dari rasio selisih maksimum tersebut terhadap FSR. Pada dasarnya, ini merupakan indikator komprehensif dari ketiga jenis kesalahan tersebut.

Kecepatan konversi

Kecepatan konversi umumnya ditentukan oleh waktu penyetelan. Mulai dari saat input berubah dari seluruhnya 0 menjadi seluruhnya 1, hingga tegangan output stabil dalam rentang FSR±½ LSB (atau rentang yang ditentukan oleh FSR±x%FSR), periode ini disebut waktu penyetelan, yang merupakan waktu respons maksimum DAC; oleh karena itu, gunakanlah untuk mengukur kecepatan konversi.

Jenis-jenis DAC

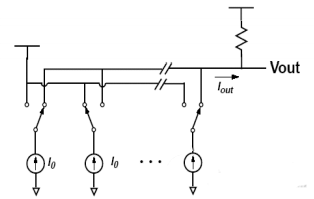

Jenis resistansi

Strukturnya ditunjukkan pada Gambar 1. Yang ditampilkan pada Gambar 1 adalah konverter tipe jaringan tangga R-2R. Keunggulannya adalah konverter ini dapat menghasilkan linearitas yang sangat baik. Karena semua sumber arus setara, kita dapat menggunakan teknologi tambahan khusus untuk mengurangi selisih antara mereka, dan strukturnya jauh lebih sederhana daripada pembagi resistor. Kelemahannya adalah resistansi selalu nonlinier, dan juga mengandung kapasitansi parasit yang terkait dengan sinyal, sehingga sulit untuk mencapai kesesuaian yang sempurna. Pada saat yang sama, kecepatan dibatasi oleh buffer keluaran, dan kecepatannya tidak dapat terlalu tinggi.

Tipe kapasitif

Strukturnya ditunjukkan pada Gambar 2. Kapasitansi orde tertinggi CN adalah 1 2N− kali lipat dari kapasitansi orde terendah C1. Keuntungannya adalah konsumsi daya yang kecil, dan akurasi pencocokan yang lebih tinggi daripada resistor. Faktor pembatas utamanya adalah ketidaksesuaian kapasitor, resistansi on-resistance sakelar, penundaan RC yang besar, dan dampak bandwidth amplifier yang terbatas terhadap kecepatan DAC. Kekurangan utama DAC distribusi muatan adalah kapasitor dalam proses CMOS memakan banyak area chip untuk diimplementasikan. Akhirnya, karena kapasitansi dalam proses CMOS bersifat nonlinier, linearitas DAC secara keseluruhan akan tertekan. Cocok untuk aplikasi presisi tinggi dengan bandwidth sedang hingga lebar.

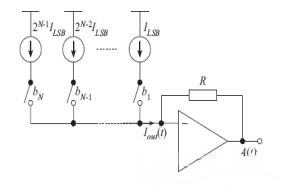

Jenis saat ini

Strukturnya ditunjukkan pada Gambar 3. Keuntungannya adalah ketika akurasi kurang dari 10 bit, luas area dapat dibuat sangat kecil, dan kecepatannya tidak dibatasi oleh bandwidth penguat serta penundaan RC yang besar. Kecepatannya dapat mencapai tingkat yang sangat tinggi. Karena seluruh arus mengalir langsung ke terminal keluaran, konsumsi energinya sangat efisien dan mudah diterapkan. Kekurangannya adalah sensitivitas terhadap ketidaksesuaian perangkat dan impedansi keluaran sumber arus yang terbatas. Cocok untuk kebutuhan broadband berkecepatan tinggi.

Juga dimungkinkan untuk tidak menggunakan penguat operasional sebagai output, dan langsung menggunakan resistansi beban untuk mengubah arus menjadi output tegangan, seperti yang ditunjukkan pada Gambar 4. Bentuk ini memungkinkan laju DAC tidak dibatasi oleh bandwidth penguat operasional.

Perkalian standar

Beberapa konverter DA menggunakan tegangan referensi konstan, sementara yang lain menambahkan sinyal AC ke input tegangan referensi. Jenis yang terakhir ini disebut konverter DA tipe perkalian karena dapat menghasilkan hasil perkalian antara input digital dan input tegangan referensi. Secara umum, konverter DA tipe perkalian tidak hanya dapat melakukan perkalian, tetapi juga dapat digunakan sebagai attenuator untuk meredam sinyal input secara digital dan sebagai modulator untuk memodulasi sinyal input.

Konverter DA tunggal

Berbeda dengan sistem konversi yang baru saja dibahas, konverter DA menggunakan metode khusus untuk mengubah nilai digital menjadi modulasi lebar pulsa atau modulasi frekuensi, yang kemudian disaring menggunakan filter digital untuk menghasilkan keluaran tegangan yang umum digunakan (juga dikenal sebagai mode aliran bit) untuk audio, dan sebagainya.

Kesimpulan

Konverter ADC dan DAC merupakan dua komponen penting dalam sistem digital apa pun. Keduanya berfungsi untuk mengubah sinyal analog menjadi sinyal digital dan sebaliknya. ADC (Analog-to-Digital Converter) menerima sinyal analog dan mengubahnya menjadi sinyal digital, sedangkan DAC (Digital-to-Analog Converter) menerima sinyal digital dan mengubahnya menjadi sinyal analog. Kedua komponen ini sangat penting untuk berbagai macam aplikasi, mulai dari pemrosesan audio dan video hingga transmisi data. Dalam artikel ini, kami telah membahas cara kerja konverter-konverter ini serta pentingnya dalam berbagai aplikasi. Kami juga telah mengulas berbagai jenis konverter, jenis-jenis sinyal yang dapat mereka ubah, serta kelebihan dan kekurangan masing-masing jenis.