Seiring dengan meningkatnya kecepatan switching keluaran sirkuit terpadu dan kepadatan papan PCB, integritas sinyal telah menjadi salah satu aspek yang harus diperhatikan dalam desain PCB digital berkecepatan tinggi. Karena masalah integritas sinyal dapat menyebabkan sistem mengeluarkan data yang salah, sirkuit tidak berfungsi dengan baik, atau bahkan sama sekali tidak berfungsi. Lalu, bagaimana cara mempertimbangkan faktor integritas sinyal secara menyeluruh dalam proses desain papan PCB dan menerapkan langkah-langkah pengendalian yang efektif? Silakan baca artikel ini lebih lanjut.

Apa itu Integritas Sinyal PCB?

Integritas sinyal PCB mengacu pada kemampuan sinyal untuk merespons dengan waktu dan tegangan yang tepat dalam rangkaian. Ini adalah kondisi di mana sinyal tidak mengalami gangguan, dan menunjukkan kualitas sinyal pada jalur sinyal.

Berbagai Masalah Integritas Sinyal

Masalah integritas sinyal dapat menyebabkan atau secara langsung memicu distorsi sinyal, kesalahan waktu, data yang salah, gangguan pada jalur alamat dan kontrol, kegagalan sistem, bahkan kegagalan total sistem. Masalah integritas sinyal yang utama meliputi: penundaan, pantulan, gangguan switching sinkron, osilasi, ground bounce, crosstalk, dan sebagainya.

Penundaan

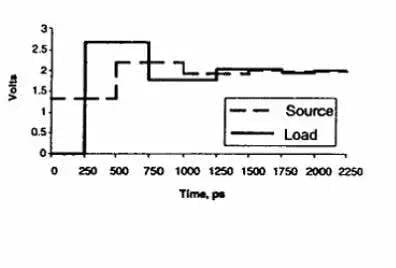

Penundaan berarti sinyal ditransmisikan dengan kecepatan terbatas melalui kabel pada papan PCB, dan sinyal dikirim dari ujung pengirim ke ujung penerima, dengan adanya penundaan transmisi di antara keduanya. Penundaan sinyal akan memengaruhi sinkronisasi sistem, dan penundaan transmisi terutama bergantung pada panjang kabel serta konstanta dielektrik medium di sekitar kabel. Dalam sistem digital berkecepatan tinggi, panjang jalur transmisi sinyal merupakan faktor paling langsung yang memengaruhi perbedaan fase pulsa jam. Perbedaan fase pulsa jam berarti bahwa dua sinyal jam yang dihasilkan pada waktu yang sama tidak sinkron saat tiba di ujung penerima. Perbedaan fase pulsa jam mengurangi prediktabilitas kedatangan tepi sinyal. Jika perbedaan fase pulsa jam terlalu besar, sinyal yang salah akan dihasilkan di ujung penerima. Seperti yang ditunjukkan pada gambar di bawah ini, penundaan jalur transmisi telah menjadi bagian penting dari siklus pulsa jam.

Refleksi

Refleksi adalah gema pada saluran sub-transmisi. Ketika waktu tunda sinyal jauh lebih lama daripada waktu transisi sinyal, saluran sinyal harus dianggap sebagai saluran transmisi. Ketika impedansi karakteristik saluran transmisi tidak sesuai dengan impedansi beban, sebagian daya sinyal (tegangan atau arus) ditransmisikan melalui saluran dan mencapai beban, tetapi sebagian lainnya dipantulkan. Jika impedansi beban lebih kecil daripada impedansi saluran, refleksi tersebut bersifat negatif. Sebaliknya, refleksi bersifat positif. Perubahan geometri rute, terminasi jalur transmisi yang tidak tepat, transmisi melalui konektor, dan diskontinuitas pada bidang daya dapat menyebabkan refleksi semacam ini.

Gangguan Pemindahan Sekaligus (SSN)

Gangguan switching simultan akan muncul jika banyak sinyal digital pada PCB diaktifkan secara bersamaan (seperti bus data CPU, bus alamat, dll.). Hal ini disebabkan adanya impedansi pada jalur daya dan ground, serta terjadinya gangguan ground bounce pada lapisan ground. Kekuatan SSN dan ground bounce juga bergantung pada karakteristik I/O sirkuit terpadu, impedansi lapisan daya dan lapisan ground PCB, serta tata letak dan rute perangkat berkecepatan tinggi pada PCB.

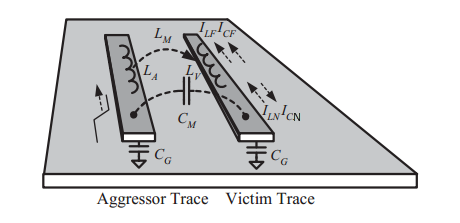

Crosstalk

Crosstalk adalah interaksi antara dua jalur sinyal, dan induktansi serta kapasitansi timbal balik antara jalur-jalur sinyal tersebut menyebabkan gangguan pada jalur tersebut. Kopling kapasitif menimbulkan arus terinduksi, sedangkan kopling induktif menimbulkan tegangan terinduksi. Gangguan crosstalk berasal dari interaksi elektromagnetik antara jaringan sinyal, antara sistem sinyal dan sistem distribusi daya, serta antara via. Cross-winding dapat menyebabkan clock palsu, kesalahan data yang terputus-putus, dll., dan memengaruhi kualitas transmisi sinyal yang berdekatan. Faktanya, kita tidak perlu sepenuhnya menghilangkan crosstalk, cukup menjaganya agar tetap dalam batas toleransi sistem. Parameter lapisan papan PCB, jarak antar jalur sinyal, karakteristik listrik driver dan receiver, serta metode terminasi baseline semuanya memiliki dampak tertentu terhadap crosstalk.

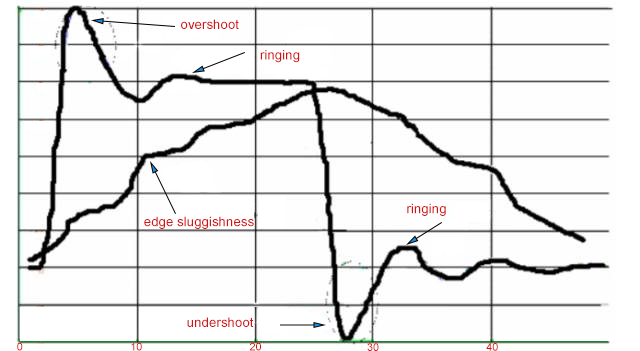

Melebihi dan Tidak Mencapai

Overshoot adalah puncak atau lembah pertama yang melampaui tegangan yang ditetapkan. Untuk tepi naik, hal ini mengacu pada tegangan tertinggi, sedangkan untuk tepi turun, mengacu pada tegangan terendah. Undershoot terjadi ketika lembah atau puncak berikutnya melampaui tegangan yang ditetapkan. Overshoot yang berlebihan dapat menyebabkan dioda pelindung bekerja, yang berujung pada kegagalan dini. Undershoot yang berlebihan dapat menyebabkan kesalahan jam atau data yang tidak diinginkan (penanganan yang salah).

Bunyi Berdering dan Bulat

Fenomena osilasi ditandai dengan terjadinya overshoot dan undershoot secara berulang. Osilasi sinyal merupakan osilasi yang disebabkan oleh induktansi dan kapasitansi transien pada jalur, yang termasuk dalam kondisi underdamped. Osilasi sekunder merupakan kondisi over-damped. Osilasi dan osilasi sekunder, seperti halnya pantulan, disebabkan oleh berbagai faktor. Osilasi dapat dikurangi dengan terminasi yang tepat, namun tidak dapat dihilangkan sepenuhnya.

Gangguan Pantulan Tanah dan Gangguan Pantulan Balik

Gangguan pantulan tanah

Ketika terjadi lonjakan arus yang besar dalam rangkaian, hal ini akan menyebabkan gangguan ground plane bounce. Misalnya, jika keluaran dari sejumlah besar chip diaktifkan secara bersamaan, akan ada arus transien yang besar mengalir melalui lapisan daya chip dan papan sirkuit. Gangguan catu daya kemudian diinduksi oleh induktansi dan resistansi kemasan chip serta bidang catu daya, yang menciptakan fluktuasi dan variasi tegangan pada bidang ground sejati (0 V). Gangguan ini memengaruhi operasi komponen lainnya. Peningkatan kapasitansi beban, penurunan resistansi beban, peningkatan induktansi ground, dan peningkatan jumlah perangkat switching semuanya akan menyebabkan peningkatan ground bounce.

Suara Gema

Gangguan balik ground plane terjadi ketika sinyal digital mengalir ke area ground analog. Hal ini dapat disebabkan oleh pembagian lapisan ground (termasuk lapisan daya dan ground), misalnya, lapisan ground dibagi menjadi ground digital, ground analog, ground pelindung, dan sebagainya. Demikian pula, lapisan daya juga dapat dibagi menjadi 2,5 V, 3,3 V, 5 V, dan sebagainya. Oleh karena itu, dalam desain PCB multi-tegangan, kita perlu memberikan perhatian khusus terhadap noise pantulan dan noise balik pada lapisan ground.

Penyebab Masalah Integritas Sinyal

Faktor-faktor seperti parameter komponen dan papan PCB, tata letak komponen pada papan PCB, serta pengkabelan jalur sinyal berkecepatan tinggi dapat menyebabkan masalah integritas sinyal. Dalam hal tata letak PCB, integritas sinyal memerlukan komponen terminasi, strategi penempatan, dan informasi rute jalur.

Bagaimana Cara Mengoptimalkan Integritas Sinyal?

Masalah integritas sinyal tidak disebabkan oleh satu faktor saja, melainkan oleh berbagai faktor dalam desain papan sirkuit. Oleh karena itu, kita perlu menggunakan berbagai metode untuk meningkatkan integritas sinyal sesuai dengan situasi yang spesifik.

Analisis crosstalk

Besarnya crosstalk berbanding terbalik dengan jarak antar jalur, dan berbanding lurus dengan panjang jalur yang sejajar serta frekuensi sinyal. Crosstalk akan bervariasi tergantung pada beban sirkuit. Untuk topologi dan konfigurasi kabel yang sama, semakin besar bebannya, semakin besar pula crosstalk-nya. Pada sirkuit digital, perubahan tepi sinyallah yang memiliki dampak terbesar terhadap crosstalk, dan semakin cepat perubahan tepi tersebut, semakin besar pula crosstalk-nya. Mengingat karakteristik crosstalk di atas, kita dapat menggunakan metode berikut untuk mengurangi crosstalk:

- Pilih perangkat yang lambat untuk mengurangi laju transisi tepi sinyal;

- Hindari mencampur jenis sinyal yang berbeda;

- Kurangi gangguan kopling dengan mengurangi beban;

- Minimalkan panjang paralel antara jalur transmisi yang berdekatan;

- Tingkatkan jarak antara konduktor di mana kopling kapasitif mungkin terjadi;

- Pendekatan yang lebih efektif adalah mengisolasi kabel dengan kabel ground;

- Masukkan kabel ground di antara kabel sinyal yang berdekatan;

- Minimalkan jumlah loop dan luas area loop;

- Hindari penggunaan kabel yang sama untuk loop sinyal;

- Lapisan sinyal dari dua lapisan yang berdekatan harus sebisa mungkin menghindari pemasangan kabel secara paralel;

- Sinyal yang sensitif terhadap crosstalk sebaiknya ditempatkan di lapisan dalam sebanyak mungkin;

analisis refleksi

Refleksi terjadi setiap kali sinyal menemui perubahan impedansi saat bergerak sepanjang saluran transmisi. Cara utama untuk mengatasi masalah refleksi adalah dengan melakukan penyesuaian impedansi terminasi. Biasanya terdapat dua strategi untuk terminasi saluran transmisi: terminasi paralel dan terminasi seri.

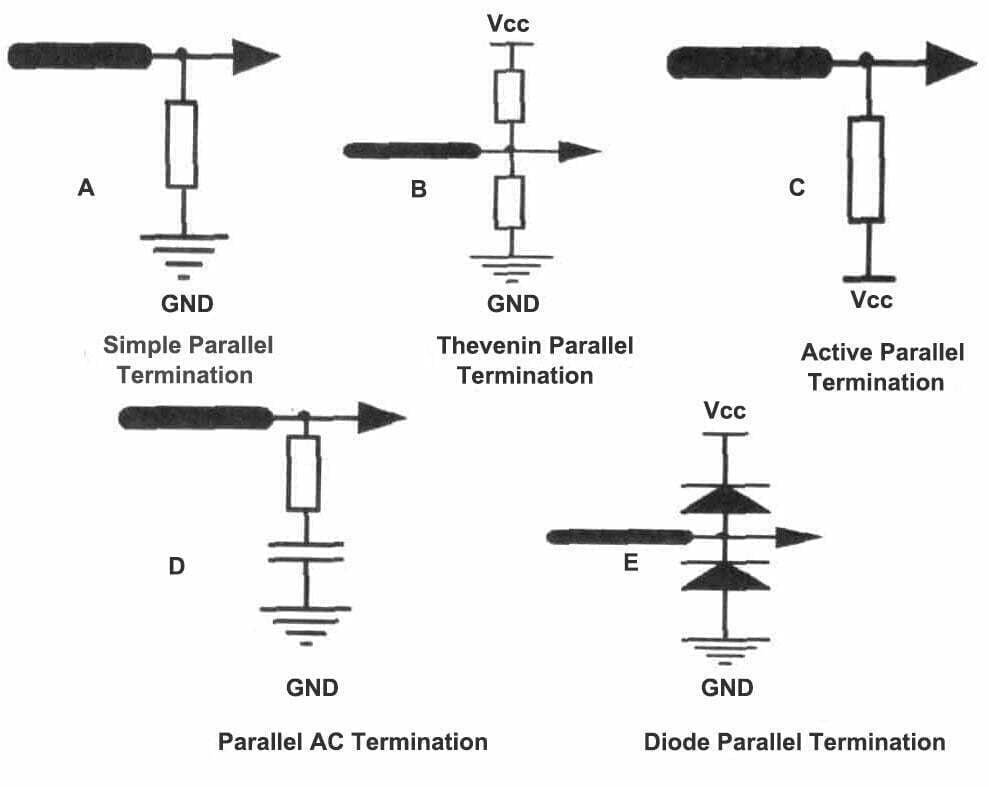

Terminasi Paralel

Terminasi paralel pada dasarnya bertujuan untuk menghubungkan impedansi pull-up atau pull-down sedekat mungkin dengan ujung beban guna mencapai kesesuaian impedansi pada terminal. Berdasarkan lingkungan aplikasi yang berbeda, terminasi paralel dapat dibagi menjadi beberapa jenis seperti yang ditunjukkan pada gambar di bawah ini.

Terminasi Serial

Terminasi serial dilakukan dengan memasang resistor secara seri pada jalur transmisi sedekat mungkin dengan sumber. Terminasi seri bertujuan untuk mencocokkan impedansi sumber sinyal; resistansi resistor seri yang disisipkan ditambah impedansi keluaran sumber penggerak harus lebih besar dari atau sama dengan impedansi jalur transmisi. Strategi ini menekan sinyal yang dipantulkan dari beban dengan membuat koefisien pantulan ujung sumber menjadi nol (masukan ujung beban bersifat impedansi tinggi dan tidak menyerap energi), sehingga sinyal dipantulkan kembali ke ujung beban dari ujung sumber.

Pemodelan Analisis Integritas Sinyal

Pemodelan dan simulasi sirkuit yang tepat merupakan solusi integritas sinyal yang paling umum. Dalam desain sirkuit berkecepatan tinggi, analisis simulasi semakin menunjukkan keunggulannya. Hal ini karena analisis simulasi dapat memberikan hasil desain yang akurat dan intuitif kepada para perancang. Dengan demikian, kita dapat mendeteksi masalah sejak dini dan memperbaikinya tepat waktu. Terdapat tiga metode pemodelan sirkuit yang umum digunakan: model SPICE, model IBIS, dan model Verilog-A.

Model SPICE

SPICE adalah simulator sirkuit analog serbaguna yang sangat mumpuni. SPICE terdiri dari dua bagian: Persamaan Model dan Parameter Model. Karena persamaan modelnya telah disediakan, model SPICE dapat terintegrasi secara erat dengan algoritma simulator, sehingga memungkinkan diperolehnya efisiensi analisis dan hasil analisis yang lebih baik.

Model IBIS

Model IBIS adalah model yang secara khusus digunakan untuk analisis integritas sinyal digital pada tingkat papan PCB dan tingkat sistem. Model ini menggunakan tabel I/V dan V/T untuk menggambarkan karakteristik sel I/O dan pin sirkuit terpadu digital. Akurasi analisis model IBIS terutama bergantung pada jumlah titik data dan keakuratan data dalam tabel I/V dan V/T. Dibandingkan dengan model SPICE, beban perhitungan model IBIS sangat kecil.

Kesimpulan

Seiring dengan perkembangan teknologi mikroelektronika yang terus berlanjut, penggunaan perangkat berkecepatan tinggi dan perancangan sistem digital berkecepatan tinggi pun semakin meningkat. Kecepatan data sistem, frekuensi clock, dan kepadatan sirkuit juga semakin meningkat. Oleh karena itu, persyaratan perancangan papan PCB pun semakin tinggi, terutama terkait masalah integritas sinyal. Untuk memastikan papan PCB memiliki integritas sinyal yang baik, berbagai faktor yang memengaruhi harus dipertimbangkan secara menyeluruh.