Le test de circuit intégré (CI) permet de détecter si la puce présente des défauts de conception ou des défauts physiques causés par le processus de fabrication. Le processus peut être réalisé en utilisant diverses méthodes de test.

Le conditionnement de circuit intégré (CI) est le processus consistant à enfermer un circuit intégré (CI) dans un boîtier protecteur. Ce processus protège le CI contre les dommages et garantit son bon fonctionnement. Il permet également de connecter le CI à d’autres appareils et circuits.

comment tester un CI avec un testeur de CI ?

kit de test de CI

Il existe différents types de kits de test de CI sur le marché, chacun étant conçu pour un objectif spécifique. Par exemple, certains kits de test de CI sont conçus pour des tests généraux. Alors que d’autres sont conçus pour des applications spécifiques comme les CI automobiles ou les CI d’alimentation.

La plupart des kits de test de CI comprennent une variété d’accessoires de base, tels qu’un multimètre, des sondes, un testeur de CI numérique et des câbles de test. Certains kits peuvent également inclure des équipements plus spécialisés, tels qu’un oscilloscope ou un analyseur logique.

Méthode de test

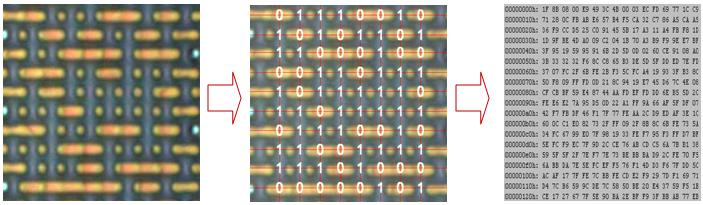

Il existe plusieurs façons de tester les circuits intégrés (CI), mais la méthode la plus courante s’appelle le test en circuit intégré (ICT). Ce type de test est effectué en connectant un dispositif de test au dispositif sous test (DUT). Ensuite, nous exécutons une série de tests pour vérifier les fonctionnalités de base.

L’ICT peut être utilisé pour tester les CI numériques et analogiques. Pour les CI numériques, le testeur enverra une série de signaux d’entrée au DUT. Et vérifiera ensuite les sorties pour voir si elles correspondent aux résultats attendus. Les CI analogiques sont généralement testés à l’aide d’une technique appelée test dynamique. Pendant ce processus, le testeur applique une série de signaux au DUT, puis mesure la réponse.

Différentes entreprises fabriquent des testeurs ICT, vous devez en choisir un qui soit compatible avec vos CI spécifiques. Une fois que vous avez un testeur, vous devez créer un dispositif de test qui se connecte au DUT. Le dispositif de test peut appliquer les signaux nécessaires au DUT et également mesurer la réponse.

Une fois que vous avez les deux, vous devez ensuite écrire un programme de test pour vérifier les résultats. Cela peut être un processus long, mais il est important de s’assurer que vos CI fonctionnent correctement.

Types de tests

Test de continuité du CI

Le test de continuité du CI est simple et vous permet de déterminer si les CI fonctionnent correctement ou non.

Ce test est effectué en connectant un multimètre au CI et en mesurant la résistance entre les différentes broches.

Si le CI fonctionne correctement, la résistance doit être faible (généralement inférieure à 10 ohms). Sinon, la résistance sera élevée (généralement supérieure à 10 ohms).

test de niveau

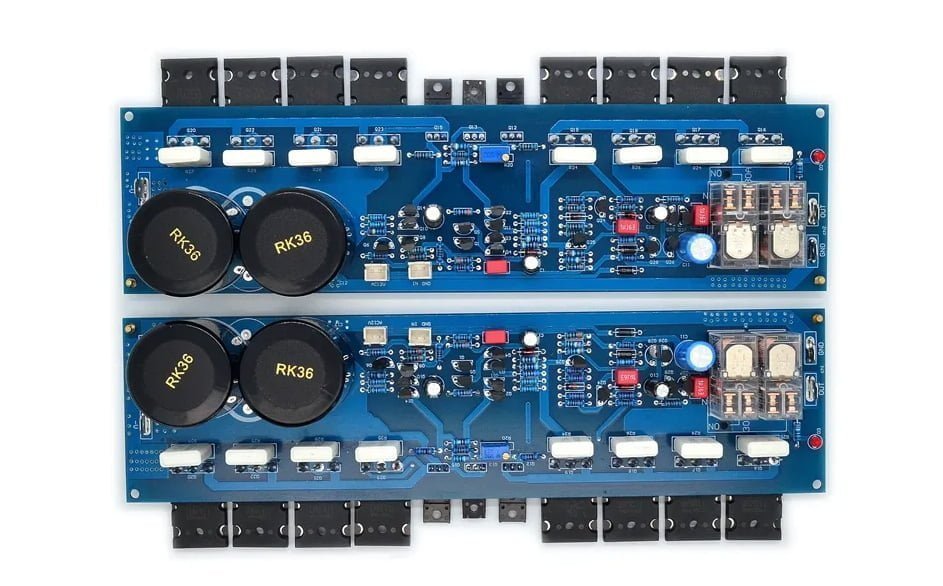

Les tests au niveau des circuits intégrés (CI) sont un type de test électrique destiné à déterminer la fonction et les performances des circuits intégrés (CI).

Ces tests sont généralement effectués sur des CI déjà installés sur une carte de circuit imprimé.

L’objectif de ces tests est de vérifier que le CI fonctionne correctement et qu’il répond aux spécifications d’utilisation prévue.

Il existe une variété de différentes méthodes de test pour les tests au niveau des CI, notamment les tests logiques, les tests fonctionnels et les tests paramétriques.

Chemin de développement de l'emballage des CI

L’emballage a globalement suivi le processus de développement suivant :

1. En termes de structure :

TO->DIP->PLCC->QFP->BGA->CSP->WLP et SiP, etc.

2. Matériaux :

Métal, céramique -> céramique, plastique -> plastique ;

3. Forme des broches :

Longes broches en ligne -> montage à broches courtes ou sans broches -> plots de soudure (ball bump)

4. Méthode d’assemblage :

Insertion traversante -> Montage en surface -> Montage direct

5. La force motrice de l’amélioration continue de l’emballage :

Taille plus petite, plus de types de puces, plus d’E/S

6. Difficultés :

Le processus devient de plus en plus complexe, et il est nécessaire de tenir compte de la dissipation thermique et de la conductivité électrique tout en réduisant le volume.

Caractéristiques et compétitivité essentielle

1. Fortes caractéristiques de fabrication

La capacité de production dépend entièrement de l’acquisition d’équipements (investissement en capital) et, comme dans la fabrication traditionnelle, elle passe également par le processus d’augmentation de la capacité et d’optimisation des processus. L’échelle permet l’accumulation d’expérience et les avantages d’une technologie de pointe.

2. L'échelle de l'emballage et des tests détermine la structure client

Les grands fabricants de conception ne coopéreront qu’avec les fabricants de tests d’une certaine échelle. Si l’échelle n’augmente pas, il est difficile de prendre de grosses commandes et il est difficile d’optimiser la structure client. Par conséquent, les entreprises dotées d’une technologie et d’une échelle de pointe entreront dans un cercle vertueux : technologie de pointe → développement client → expansion du financement → augmentation de la capacité de production → optimisation des processus → technologie de pointe, et creuseront progressivement l’écart avec les concurrents.

3. Compétitivité essentielle

Les deux caractéristiques de l’industrie ci-dessus déterminent la compétitivité essentielle des entreprises de tests professionnels de circuits intégrés :

Capacité de R&D : se concentrer sur le développement de procédures de test et de solutions de test.

Degré de commercialisation : les capacités de développement de programmes de test et d’optimisation des processus proviennent de l’expérience de test de différents types de puces apportée par un grand nombre de clients.

Processus de test parfait : grâce à l’intégration étroite de la conception en amont et du traitement des plaquettes, le processus de test et le processus sont continuellement optimisés.

Capacité d’opération financière : l’étape actuelle du développement national détermine que l’échelle est la condition préalable au développement. Par conséquent, la capacité de financement correspondant à la technologie et à la force du marché est le soutien au développement et à la croissance de l’entreprise.

marché de l'emballage et des tests de circuits intégrés

1. Échelle de l'emballage et des tests de circuits intégrés

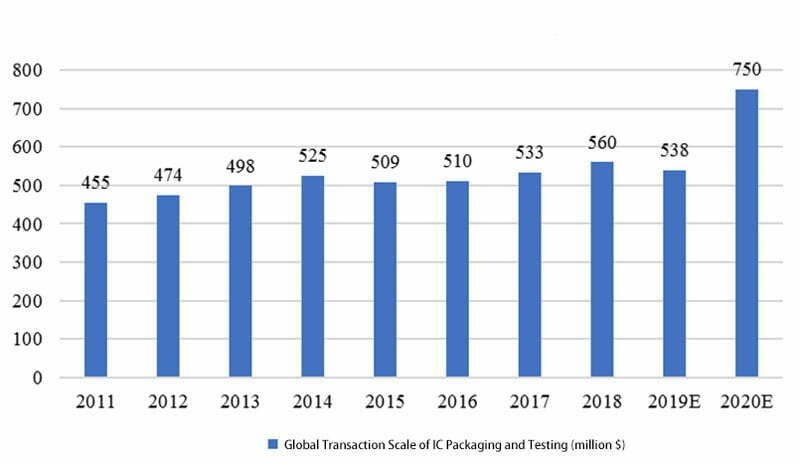

1.1 Transaction mondiale d'emballage et de tests de circuits intégrés (2011-2020)

En 2019, l’ensemble de l’industrie des semi-conducteurs a ralenti et a affiché une croissance négative, ainsi que le marché de l’emballage et des tests de puces. Cependant, le marché s’est ensuite redressé en raison de la demande de 5G, d’IA, d’IoT, d’informatique en nuage et de big data. Les experts prédisent que l’ensemble du marché de l’emballage et des tests de puces en 2024 pourrait atteindre 75 milliards de dollars.

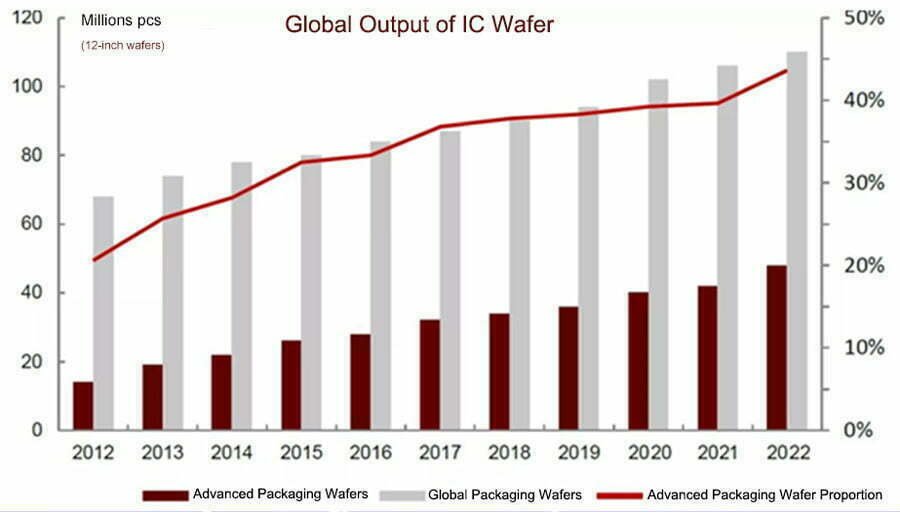

1.2 Production mondiale de plaquettes de circuits intégrés (2012-2022)

Avec l’accélération de domaines émergents tels que la 5G, l’IoT et l’IA, la taille requise des puces devient de plus en plus petite. En même temps, il existe de plus en plus de types de puces. Le nombre de broches d’E/S a également augmenté de manière significative, et la demande d’emballage avancé a progressivement augmenté.

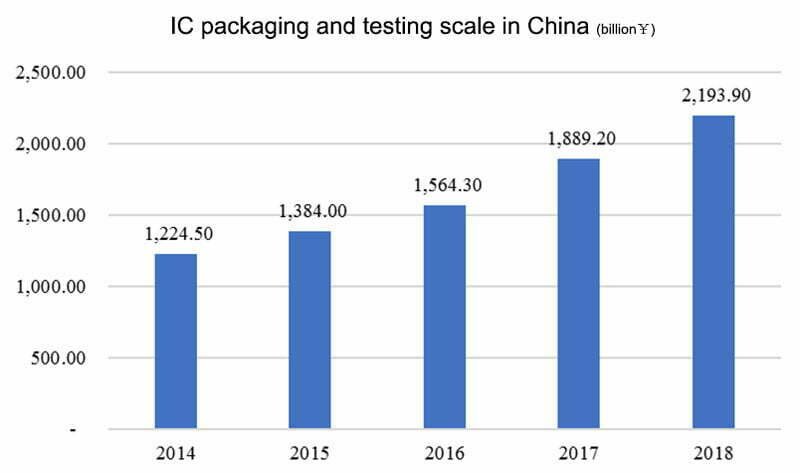

1.3 Échelle de l'emballage et des tests de circuits intégrés en Chine (2014-2018)

En 2018, la capacité d’emballage et de test de circuits intégrés en Chine continentale a atteint 217,44 milliards d’unités, et la taille du marché de l’industrie de l’emballage et des tests de circuits intégrés a atteint 219,39 milliards de yuans, soit une augmentation de 16,1 % d’une année sur l’autre.

2. La croissance de l'échelle de l'emballage avancé

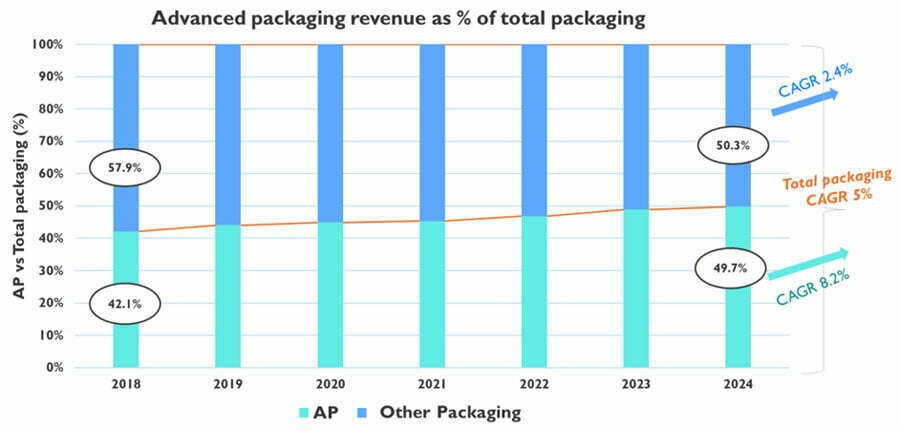

2.1 Proportion de l'emballage avancé de circuits intégrés dans le total

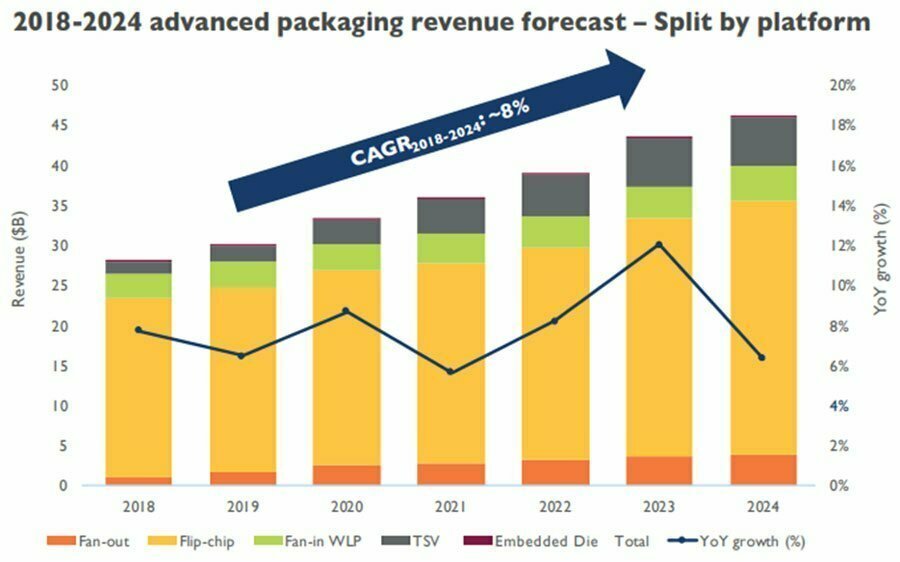

Selon les statistiques de Yole, bien que l’industrie mondiale des semi-conducteurs ait ralenti et ait connu une croissance négative en 2019, la taille du marché de l’emballage avancé maintiendra une tendance à la croissance. En 2018, la taille du marché de l’emballage avancé était de 27,6 milliards de dollars américains.

Croissant à un taux de croissance annuel composé de 8 %, atteignant environ 44 milliards de dollars d’ici 2024. Le marché traditionnel de l’emballage croîtra à un taux de croissance annuel composé de 2,4 %, tandis que le TCAC de l’ensemble de l’industrie de l’emballage de circuits intégrés atteindra 5 %.

2.2 Tendances de prévision des revenus de l'emballage avancé (2018-2024)

Dans le secteur de l’emballage avancé, la technologie flip-chip représente la plus grande part. En 2018, les revenus de l’emballage et des tests flip-chip représentaient environ 81 % du marché de l’emballage avancé. D’ici 2024, en raison du développement rapide d’autres technologies, ce chiffre devrait tomber à 72 %.

De 2018 à 2024, les TVS, ED et fan-out sont les technologies à la croissance la plus rapide. Le taux de croissance des revenus de l’emballage 2.5D/3D (TSV), ED et de l’emballage fan-out (Fan-out) devrait être respectivement de 26 %, 49 %, 26 %.

Le TCAC de Fan-in WLP 2018-2024 est relativement faible, seulement 6,5 %, et la taille du marché des dies embarqués en 2018 est inférieure à 25 millions de dollars américains.

Cependant, le TCAC sera aussi élevé que 49 % au cours des cinq prochaines années, et les principaux facteurs de croissance proviendront de la demande des installations de communication, de l’électronique automobile et des marchés mobiles.

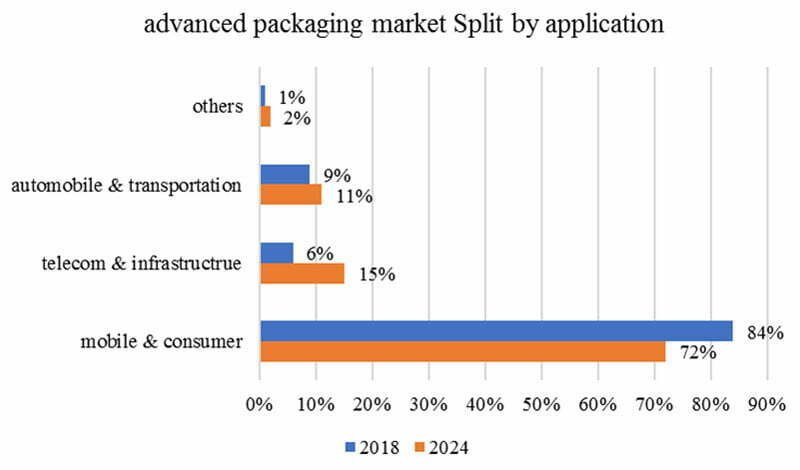

2.3 applications d'emballage avancé

Par domaine d’application, en 2018, les applications mobiles et grand public représentaient 84 % du marché total de l’emballage avancé. De 2019 à 2024, le TCAC de ce segment du marché des applications était de 5 %, et en 2024, il représentait 72 % du marché total de l’emballage avancé.

Le segment des télécommunications et des infrastructures est le segment à la croissance la plus rapide du marché de l’emballage avancé (environ 28 %), et sa part de marché passera de 6 % en 2018 à 15 % en 2024.

Dans le même temps, la part de marché du segment automobile et des transports a augmenté de 9 % en 2018 à 11 % en 2024.

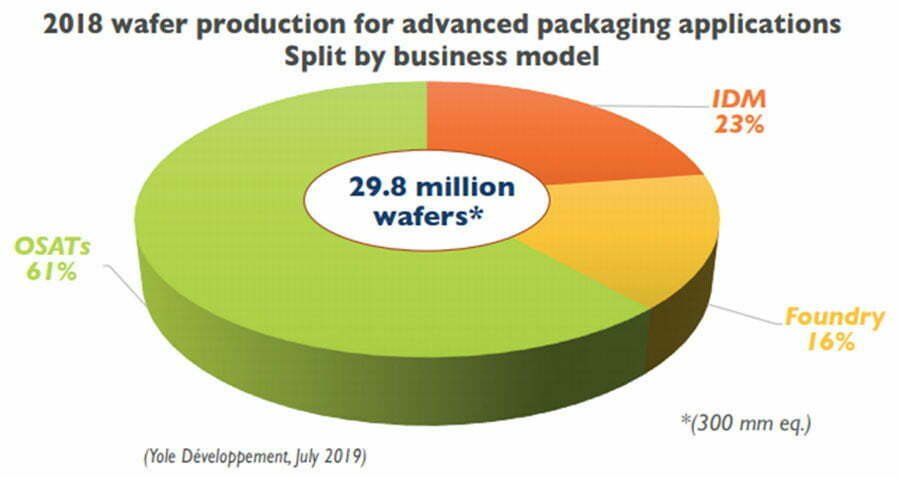

En 2018, les fonderies professionnelles de conditionnement et de test de puces représentaient 61 % du marché de l’emballage et du test avancés, tandis que les entreprises de type IDM représentaient 23 % et les fabricants de type fonderie représentaient 16 %.

Paysage concurrentiel

1. 10 premières entreprises mondiales (2018-2019)

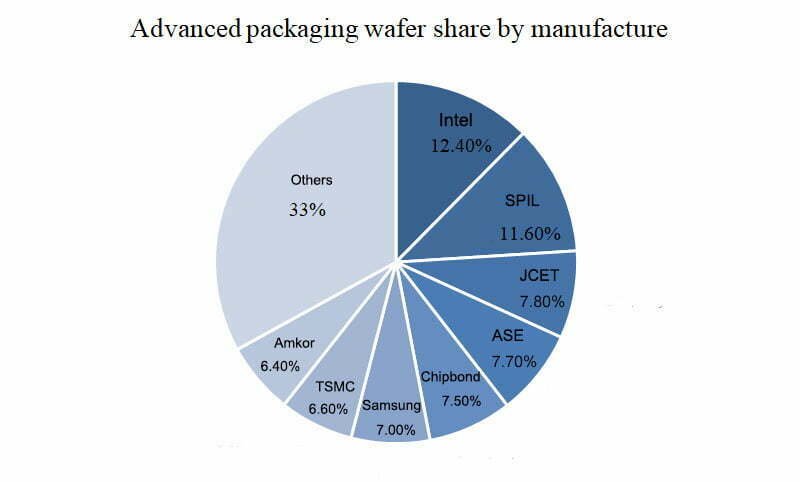

Le marché du conditionnement et des tests de puces est relativement concentré. Les dix principaux fabricants contrôlent environ 80 % du marché. Les fabricants de Chine continentale et de Taïwan dominent le marché. Pendant de nombreuses années, l’industrie taïwanaise du conditionnement et des tests a capturé près de la moitié du chiffre d’affaires mondial, s’établissant fermement parmi les dix premiers.

Indépendamment des revenus de conditionnement et de tests de puces des IDM (tels qu’Intel et Samsung), ASE et Amkor occupent fermement les deux premières places dans le conditionnement et les tests de puces professionnels.

2. Opportunités et défis

Les changements dans la chaîne d’approvisionnement des semi-conducteurs, les évolutions des modèles économiques et l’incertitude des relations commerciales entre les États-Unis et la Chine ont créé des opportunités pour certains fabricants et des menaces pour d’autres.

2.1 Extension de la chaîne industrielle

Dans cet environnement commercial en constante évolution, la chaîne d’approvisionnement des semi-conducteurs change à tous les niveaux. Certains fournisseurs ont réussi à étendre de nouveaux modèles économiques.

Cela a considérablement affecté la chaîne de fabrication de circuits intégrés, tandis que d’autres fabricants n’ont pas réussi à profiter de la dynamique. Différents fournisseurs ont des moteurs différents qui les poussent à se développer dans de nouvelles activités.

Par exemple, des entreprises de logiciels telles que Google, Microsoft, Facebook et Alibaba conçoivent leurs propres processeurs pour gagner en intégration/personnalisation au niveau du système et en contrôle de la chaîne d’approvisionnement au niveau de l’assemblage.

Le plus grand changement se trouve dans les fonderies qui commencent à se développer dans le secteur de l’emballage avancé. Bien qu’elles soient relativement « nouvelles », leur impact est énorme.

2.2 Innovation technologique de l'emballage

TSMC est un leader de l’innovation en matière d’emballage fan-out et de plateformes d’emballage avancé 3D. Ils offrent une variété de produits tels que InFO (et ses variantes), CoWoS, WoW, 3D SoIC, et plus encore.

L’emballage avancé est devenu une activité mature pour TSMC. Ils s’attendent à ce qu’il génère 3 milliards de dollars de revenus en 2019, ce qui le placerait au quatrième rang du classement OSAT.

UMC est un fournisseur majeur d’interposeurs en silicium pour l’emballage 2.5D. Ils ont récemment établi un partenariat avec Xperi pour optimiser et commercialiser les technologies ZiBond et DBI pour divers dispositifs semi-conducteurs.

Pendant ce temps, Wuhan Xinxin (XMC) fournit des packages 3D IC TSV pour les capteurs d’image et les applications haute performance. Collectivement, ces acteurs ont joué un rôle majeur dans le passage de l’emballage des substrats aux plateformes silicium.

2.3 L'emballage au niveau du système tend à être populaire

C’est une tendance que les participants à la chaîne d’approvisionnement de l’emballage SiP étendent leurs activités en amont et en aval. Dans la chaîne d’approvisionnement traditionnelle de l’emballage SiP, les entreprises représentatives de l’emballage et des tests de circuits intégrés comprennent Changdian Technology et ASE, qui fournissent principalement des produits d’emballage et de test standard au niveau fonctionnel. L’entreprise représentative de l’emballage au niveau du système est USI, qui effectue principalement un emballage système au niveau du module. Ces deux entreprises appartiennent à la relation amont et aval, et leurs processus et équipements impliqués sont différents.

2.4 Puces intégrées

D’autre part, les fabricants de substrats de circuits intégrés et de PCB tels que Samsung Electro-Mechanics (SEMCO), Unimicron, AT&S et Shinko Electric (Shinko) tirent parti des puces intégrées (et des composants passifs) dans les packages fan-out au niveau du panneau et les substrats organiques. composants) dans l’espace d’emballage avancé et réduisent la part de marché d’OSAT (en particulier dans les activités impliquant un emballage avancé).

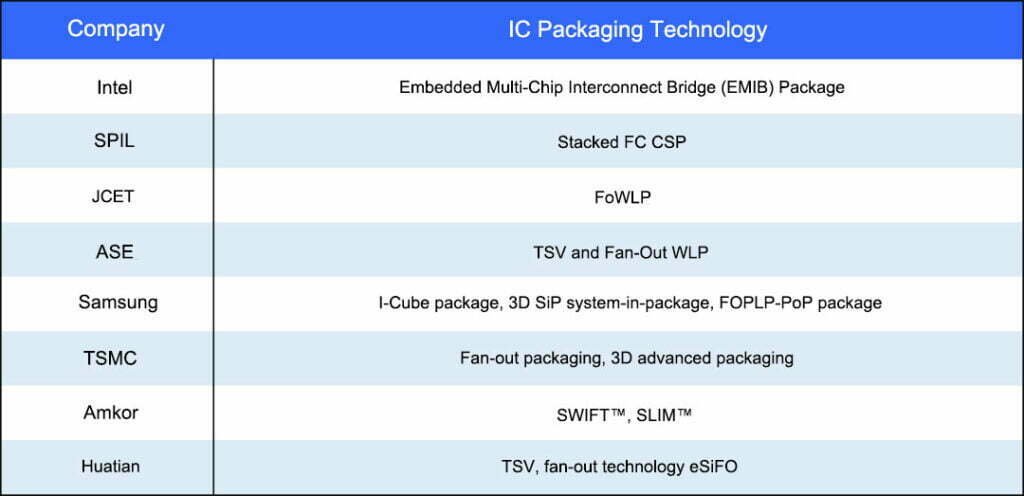

3. Part de marché des wafers d'emballage avancé

Comparée à la concentration globale du marché de l’emballage et des tests, la concentration du marché de l’emballage et des tests avancés est relativement faible. En 2017, les 8 principaux fabricants représentaient 67 % des parts de marché de l’emballage avancé.

Les fournisseurs du marché de l’emballage avancé ont différents domaines d’expertise :

Situation de l'industrie chinoise de l'emballage IC

L’industrie chinoise de l’emballage IC a démarré très tôt et s’est développée rapidement, elle est principalement basée sur des produits d’emballage traditionnels. Ces dernières années, les fabricants nationaux ont procédé à des fusions et acquisitions. À l’heure actuelle, la plateforme technologique chinoise s’est pratiquement synchronisée avec celle des fabricants étrangers. De plus, les technologies d’emballage avancées telles que BGA, TVS, WLCSP et SiP ont été produites en masse.

Cependant, il existe encore un certain écart entre le chiffre d’affaires global de l’emballage avancé à Taiwan et aux États-Unis. Selon les statistiques de TrendForce, le chiffre d’affaires de l’emballage avancé de la Chine en 2018 était d’environ 52,6 milliards de yuans. Il représentait 25 % du chiffre d’affaires total national de l’emballage et des tests, ce qui est inférieur au ratio mondial de 41 %. Il y a donc encore beaucoup de marge de croissance à l’avenir.

Marché chinois de l'emballage IC avancé

De plus, il existe également un écart important entre les entreprises d’emballage du continent et les principaux fabricants internationaux. En particulier, l’écart est évident dans la technologie d’emballage de circuits intégrés à haute densité, telle que la technologie d’emballage de puces HPC. La technologie d’empilement 3D multi-puce SoC proposée par TSMC. Elle adopte une structure de liaison sans bosses, ce qui peut considérablement améliorer la vitesse de calcul globale du CPU/GPU et de la mémoire. Intel a également proposé un concept d’emballage 3D similaire, empilant la mémoire sur les puces CPU et GPU.

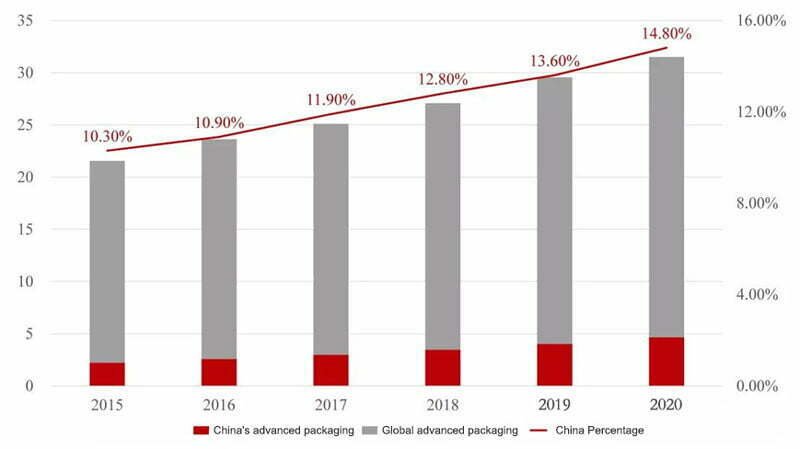

La valeur de production globale du marché chinois de l’emballage avancé est relativement faible, mais elle croît rapidement et sa proportion s’étend. Les données de Yole le montrent. En 2017, la valeur de production de l’emballage avancé en Chine était de 2,9 milliards de dollars américains, représentant 11,9 % du monde, et atteindra 4,6 milliards de dollars américains en 2020, représentant 14,8 % du monde. Selon les données, les entreprises chinoises d’emballage et de test ont accéléré l’augmentation de leur capacité de production dans le domaine de l’emballage avancé en 2018, avec un taux de croissance de 16 %, soit deux fois le taux mondial.

force motrice du marché

Il existe deux voies de développement pour l’emballage avancé :

L’une consiste à réduire la taille pour la rapprocher de la taille de la puce. Un indicateur important est le rapport entre la surface de la puce et la surface de l’emballage. Plus ce rapport est proche de 1, mieux c’est, y compris WLCSP, FC, Bumping, Fanout, etc.

Le second est le développement fonctionnel, qui met l’accent sur l’intégration hétérogène et fournit des fonctionnalités multiples dans la miniaturisation des systèmes, y compris TSV, SIP et ainsi de suite.

1. Technologie SIP

Le processus mondial de fabrication de semi-conducteurs approche de la limite physique des diodes. Le processus le plus avancé est de 7 nm. En raison de l’investissement énorme, il devient de plus en plus coûteux d’améliorer davantage les performances des puces du côté de la fabrication. À partir de l’emballage des puces, la technologie système-en-boîtier SIP combine des puces avec différentes fonctions telles que des puces logiques et de la mémoire.

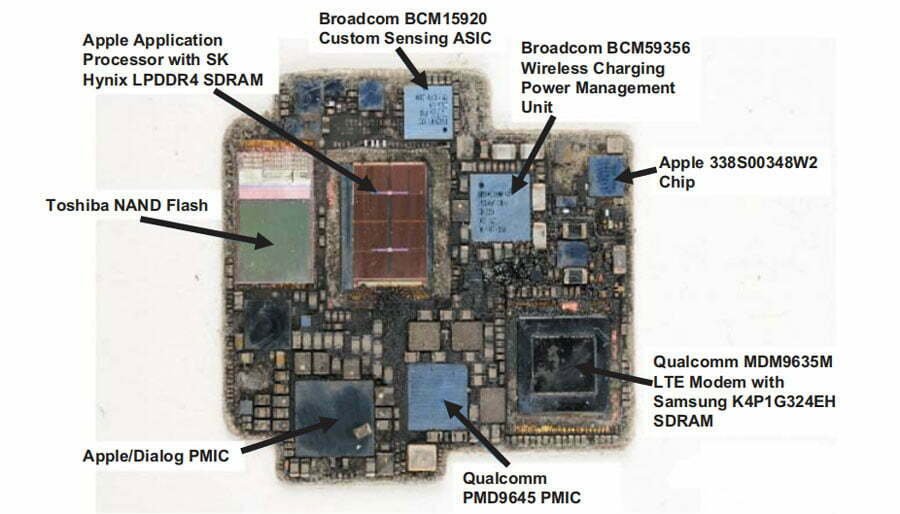

Les composants passifs IPD, RF RF et les capteurs et autres puces sont emballés dans un seul module, ce qui peut réduire la taille de la puce, améliorer les performances de la puce et réduire la consommation d’énergie. L’Internet des objets (IoT) est un scénario d’application important qui favorise le développement de l’emballage SIP, et les appareils portables sont un domaine avec un grand potentiel d’application pour la technologie système-en-boîtier à l’avenir. Le capteur de reconnaissance d’empreintes digitales, le capteur de reconnaissance faciale 3D, le réseau sans fil WiFi et d’autres modules fonctionnels de l’Apple Watch sont emballés ensemble, ce qui est l’utilisation de la technologie de module système-en-boîtier (SiP) d’ASE.

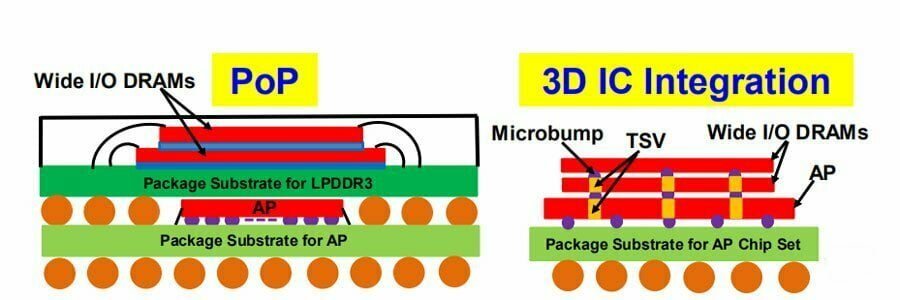

La technologie SIP intègre avec succès les circuits intégrés, les dispositifs discrets, les dispositifs optiques, les mémoires, les condensateurs céramiques multicouches et les résistances de puce dans des substrats minces, minces et courts sans que leurs informations ne s’interfèrent mutuellement. Nous pensons qu’Apple a au moins une avance d’un à deux ans sur ses concurrents dans l’application de l’emballage système. Selon les différentes exigences d’application et la complexité du produit, les types de système-en-boîtier SiP peuvent être divisés en modules 2D contenant plusieurs composants actifs et passifs et en modules 3D plus complexes. Par exemple, PiP (Package-in-Package) dans le système, PoP (Package-on-Package) et la technologie d’emballage 2.5D/3D sur le système.

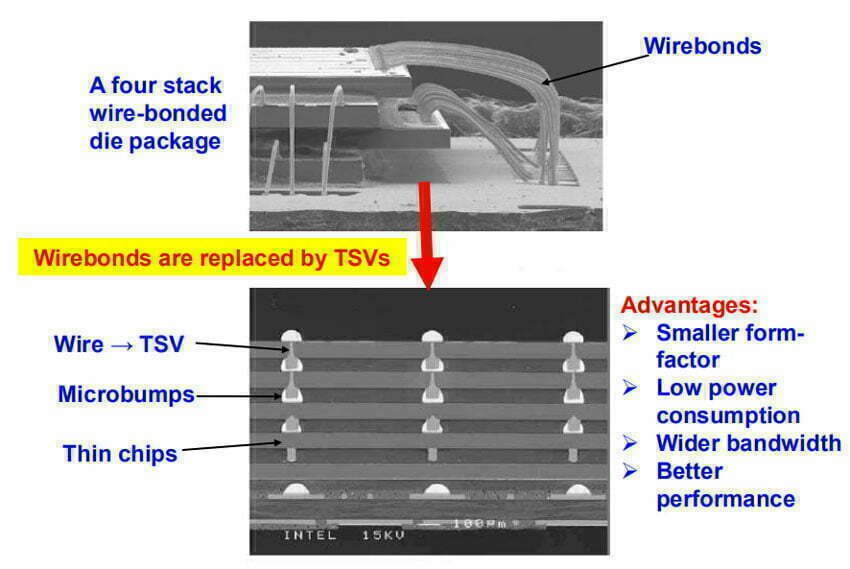

2. Technologie TSV

En tant que représentant de la technologie d’emballage 3D, la technologie TSV aura des applications plus larges dans le domaine de l’emballage de la mémoire flash 3DNANDFLASH et de l’emballage de la mémoire DRAM à l’avenir. La mémoire est devenue la sous-section avec le plus grand potentiel de croissance dans le domaine national des semi-conducteurs. Les deux principaux projets de mémoire, Yangtze Memory (NAND FLASH) et Hefei Changxin (DRAM), seront produits en masse en 2020, ce qui sera sans aucun doute d’énormes opportunités de croissance pour les fabricants nationaux dotés de technologies d’emballage avancées.

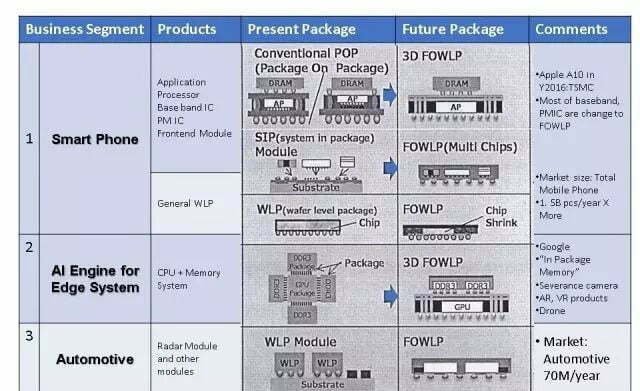

3. Fan-out

Entrant dans l’ère de la 5G, afin d’obtenir un débit de données et une capacité de bande passante plus élevés, des ondes électromagnétiques de fréquence plus élevée doivent être utilisées comme support de transmission, et les longueurs d’onde sont plus courtes et atteignent le niveau des ondes millimétriques. Les deux fréquences principales de l’ère 5G, la bande de fréquence Sub-6 GHz et la bande de fréquence de 28 GHz, en raison de l’augmentation de la fréquence, le résultat de la diminution de la longueur d’onde est que l’antenne est plus courte, de sorte que l’antenne devrait être intégrée dans la puce à l’ère de la puce 5G pour simplifier la conception et peut réduire les coûts.

Il existe deux technologies d’emballage possibles pour les puces 5G de nouvelle génération : AiP (Antenna in Package) avec un substrat et un emballage fan-out sans carte support. Étant donné que le deuxième schéma d’emballage fan-out ne nécessite pas de substrat, il peut réduire davantage les coûts et réduire la taille de la puce sur la base de l’intégration de plusieurs puces, de sorte que la technologie d’emballage fan-out pourrait devenir la technologie dominante de l’emballage des puces 5G.

Chaque module électronique de la voiture adopte différentes technologies d’encapsulation, et l’encapsulation de la puce radar à ondes millimétriques dans l’électronique automobile utilisera également un grand nombre de technologies d’encapsulation Fan-out.

L’usine de conditionnement et de test nationale Changdian Technology a acquis la technologie d’encapsulation eWLB après avoir acquis Xingke Jinpeng, devenant l’un des premiers fabricants de conditionnement et de test dans le domaine des radars à ondes millimétriques. Huatian Technology devrait s’efforcer dans ce domaine après des percées technologiques récentes.

Direction du développement technologique

Il existe deux types d’encapsulation de semi-conducteurs : l’encapsulation traditionnelle et l’encapsulation avancée. Avec l’expansion continue de l’échelle de l’encapsulation avancée, la proportion s’est progressivement rapprochée et dépassé la tendance de l’encapsulation traditionnelle. Pour l’industrie des semi-conducteurs, le conditionnement et le test ne sont plus seulement un lien de fonderie distinct dans le passé, mais une solution intégrée qui combine la conception, les matériaux et l’équipement.

Par conséquent, l’encapsulation avancée devient de plus en plus importante dans le domaine du conditionnement et du test de semi-conducteurs. Selon les prévisions de Yole, le marché mondial de l’encapsulation avancée atteindra 44 % de l’ensemble des services d’encapsulation de circuits intégrés d’ici 2020, avec un chiffre d’affaires annuel d’environ 31,5 milliards de dollars américains ; le marché chinois de l’encapsulation avancée atteindra 4,6 milliards de dollars américains en 2020, avec un taux de croissance annuel composé de 16 %. D’un point de vue technique, FOWLP, SiP et 3DTSV sont les trois technologies de conditionnement et de test avancées les plus préoccupantes.

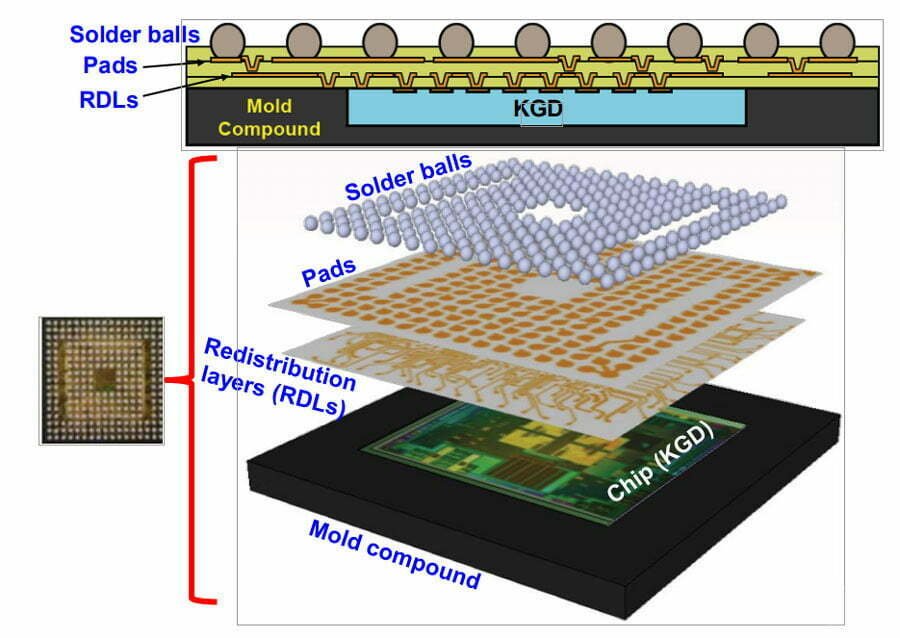

1. Conditionnement FOWLP

Le package FOWLP fait référence à une nouvelle méthode de combinaison de plusieurs matrices provenant de processus hétérogènes dans un package compact. Il a été proposé pour la première fois par Intel. Les avantages de FOWLP par rapport à la technologie d’emballage fan-in sont : une épaisseur de package réduite, une évolutivité (pour augmenter le nombre d’E/S), des performances électriques améliorées, de bonnes performances thermiques et un processus sans substrat.

2. Emballage SiP

L’emballage système sur puce (SiP) est un nouveau type de technologie d’emballage au sommet du domaine de l’emballage de circuits intégrés, qui intègre une ou plusieurs puces de circuits intégrés et des composants passifs dans un seul package. SiP est une solution idéale qui combine les avantages des ressources principales existantes et des processus de production de semi-conducteurs pour réduire les coûts et raccourcir le délai de mise sur le marché. En même temps, il surmonte les difficultés telles que la compatibilité des processus, le mélange des signaux, les interférences de bruit et les interférences électromagnétiques dans SOC. De plus, l’application de SiP est très étendue. Actuellement, la valeur de production des smartphones représente la proportion la plus élevée, soit environ 70%.

La demande croissante d’emballage SiP induite par l’utilisation commerciale de la technologie 5G. Tout d’abord, en raison de l’augmentation de la valeur du RF autonome, la taille globale du marché du RF front-end a augmenté rapidement. Il existe une tendance générale à modulariser le RF front-end, l’antenne 5G à ondes millimétriques et les composants d’intégration RF, qui sont généralement basés sur GaAs. L’antenne 5G est principalement composée de LCP (polymère à cristaux liquides), et l’emballage SiP est bien adapté à l’intégration hétérogène. L’emballage SiP devrait devenir plus populaire dans le secteur du RF.

3. Emballage 3D - TSV

L’emballage 3D améliore les performances du cœur telles que la taille, le poids, la vitesse, le rendement et la consommation d’énergie, et est considéré par la plupart des fabricants de semi-conducteurs comme la méthode d’emballage la plus prometteuse. Alors que les tentacules de l’emballage avancé continuent de s’étendre aux technologies avancées à haute performance et à haute densité d’intégration, TSV, connu comme la technologie d’emballage 3D de quatrième génération, devrait devenir une force motrice durable pour le développement futur de l’emballage avancé.