FPGA, abreviatura de Field Programmable Gate Array (matriz de puertas programables en campo), es una arquitectura de hardware reconfigurable. En otras palabras, es un chip que se puede programar para cambiar su estructura interna. Las FPGA se han utilizado durante muchos años como sustituto de bajo volumen de los chips específicos para aplicaciones (ASIC).

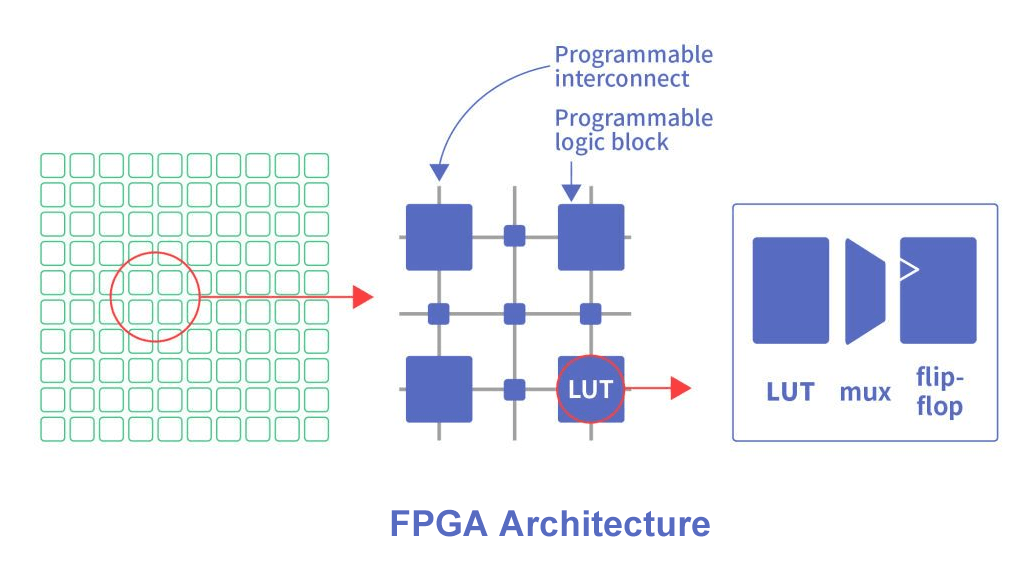

Estructura básica de FPGA

La arquitectura FPGA incluye principalmente cuatro partes: bloque lógico configurable (CLB), bloque de entrada y salida (IOB), cableado interno (interconexión) y otras unidades integradas. A continuación se muestra la estructura interna del dispositivo FPGA.

Bloque lógico configurable (CLB)

CLB es la unidad lógica básica de FPGA. El número real y las características variarán de un dispositivo a otro, pero cada CLB contiene una matriz de conmutación configurable de 4 o 6 entradas, varios circuitos de selección (multiplexores, etc.) y flip-flops.

Bloque de entrada y salida (IOB)

Los FPGA pueden admitir muchos estándares de E/S, lo que los convierte en un puente de interfaz ideal para diseños de sistemas. Las E/S del FPGA se agrupan por bancos, y cada banco puede admitir de forma independiente diferentes estándares de E/S. En la actualidad, los FPGA más avanzados proporcionan más de diez bancos de E/S, lo que permite una compatibilidad flexible con las E/S.

Cableado interno (interconexión)

Los CLB proporcionan el rendimiento lógico, y el enrutamiento de interconexión flexible se encarga de transmitir las señales entre los CLB y las E/S. Existen varios tipos de enrutamiento, que van desde interconexiones CLB dedicadas (recursos de cable corto) hasta cables largos horizontales y verticales de alta velocidad (recursos de cable largo) dentro del dispositivo, pasando por el enrutamiento global de baja distorsión para relojes y otras señales globales (recursos de enrutamiento global dedicados).

Unidades integradas

Las unidades de núcleo duro integradas incluyen RAM, DSP, DCM (módulo de gestión de reloj digital) y otros núcleos duros de interfaz específicos, etc.

Características de FPGA

- El uso de FPGA para diseñar circuitos ASIC ofrece un ciclo corto, un coste reducido, un riesgo mínimo y una calidad estable.

- FPGA adopta tecnología CHMOS de alta velocidad con bajo consumo de energía.

- Arquitectura FPGA, unidad lógica flexible, alta integración, amplia gama de aplicaciones.

- La FPGA es compatible con las ventajas de la PLD y la matriz de puertas general, y puede realizar circuitos a gran escala.

- Es posible la reprogramación in situ y el coste de mantenimiento posterior es bajo.

- FPGA es un sistema de computación paralela que puede satisfacer requisitos multifuncionales al mismo tiempo.

¿Cómo funciona un FPGA?

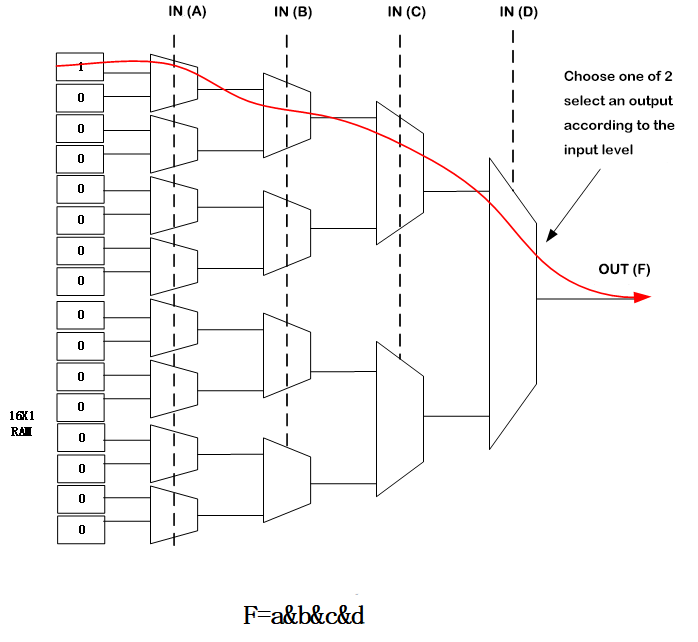

La FPGA implementa funciones lógicas cargando datos de programación en unidades de almacenamiento estáticas internas. El valor almacenado en la unidad de almacenamiento determina la función lógica de la unidad lógica y el modo de conexión entre cada módulo de la unidad lógica o entre el módulo y la E/S, y finalmente determina la función que realiza la FPGA. La FPGA utiliza una pequeña tabla de consulta para implementar la lógica combinacional, cada tabla de consulta está conectada a la entrada de un flip-flop D, y el flip-flop D se utiliza para accionar otros circuitos lógicos o E/S, formando así una función lógica combinada y realizando el módulo básico de la unidad lógica de la función lógica secuencial. Estos módulos están conectados entre sí o al módulo de E/S mediante cables metálicos.

A continuación se muestra un ejemplo sencillo para explicar el principio de la FPGA:

Como se muestra en la figura anterior, configuramos 16bitRAM como 0000000000000001, y este circuito es equivalente a F=A&B&C&D;

Solo cuando A=B=C=D=1, F=1; de lo contrario, F=0.

«0000000000000001». Esta cadena de números es programación FPGA.

Bloque lógico de FPGA

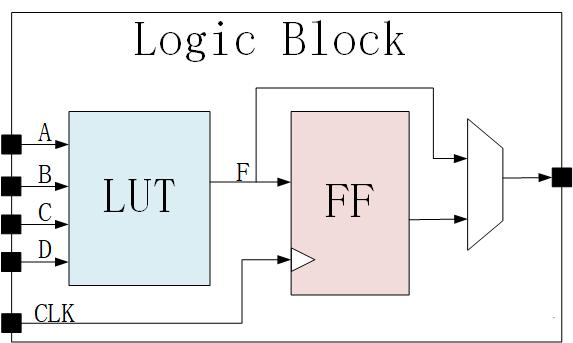

En FPGA existe un término específico, denominado LUT, tabla de consulta (tabla de búsqueda).

La LUT constituye la unidad más básica de cualquier FPGA.

La LUT solo puede implementar lógica combinacional digital, por lo que se añade un flipflop de registro (ff) para realizar el bloqueo de datos.

Como se muestra en la siguiente figura: Las LUT + registros forman la estructura básica de las FPGA modernas.

Proceso de desarrollo de FPGA

El proceso de desarrollo de FPGA es el proceso de utilizar software de desarrollo EDA y herramientas de programación para desarrollar chips FPGA. El proceso de desarrollo de FPGA se muestra generalmente en la figura siguiente, incluyendo pasos principales tales como definición de funciones/selección de dispositivos, entrada de diseño, simulación de funciones, síntesis lógica, diseño y enrutamiento e implementación, programación y depuración.

Definición de función/selección de dispositivo:

Antes de comenzar el proyecto de diseño FPGA, es necesario definir las funciones del sistema y la división de los módulos. Además, según los requisitos de la tarea, como la función y la complejidad del sistema, se pueden distribuir la velocidad de trabajo y los recursos, los costes y las conexiones del propio dispositivo. Se deben sopesar aspectos como el rendimiento y seleccionar el esquema de diseño adecuado y el tipo de dispositivo apropiado.

Aportación al diseño:

La entrada de diseño se refiere al uso del lenguaje de descripción de hardware para expresar el sistema o circuito diseñado en código. El lenguaje de descripción de hardware más utilizado es Verilog HDL.

Simulación funcional:

La simulación funcional se refiere a la verificación de la función lógica del circuito diseñado por el usuario antes de la síntesis lógica. Antes de la simulación, es necesario crear una plataforma de prueba y preparar los estímulos de prueba. Los resultados de la simulación generarán archivos de informe y formas de onda de señal de salida, a partir de los cuales se pueden observar los cambios de las señales de cada nodo. Si se encuentran errores, vuelva al diseño para revisar el diseño lógico. Las herramientas de simulación más comunes incluyen ModelSim de Model Tech, VCS de Sysnopsys y otros programas.

Síntesis lógica:

La denominada síntesis consiste en transformar la descripción del nivel superior de abstracción en la descripción del nivel inferior. La optimización sintética optimiza las conexiones lógicas generadas de acuerdo con los objetivos y requisitos, y hace que el diseño jerárquico sea plano para que el software de diseño y enrutamiento de FPGA lo implemente. En lo que respecta al nivel actual, la optimización integral se refiere a la compilación de la entrada de diseño en una lista de redes conectadas lógicamente compuesta por unidades lógicas básicas, como puertas AND, puertas OR, puertas NOT, RAM y flip-flops, en lugar de circuitos reales a nivel de puerta.

Diseño e implementación:

El diseño y el enrutamiento pueden entenderse como el uso de herramientas de implementación para asignar la lógica a los recursos de la estructura del dispositivo de destino, determinar el diseño óptimo de la lógica, seleccionar los canales de cableado vinculados por la lógica y las funciones de entrada y salida, y generar los archivos correspondientes (como archivos de configuración e informes relacionados); la implementación consiste en configurar la lista de redes lógicas generada por la síntesis para un chip FPGA específico. Dado que solo el fabricante del chip FPGA conoce mejor la estructura del chip, el diseño y el enrutamiento deben elegir las herramientas proporcionadas por el desarrollador del chip.

Depuración de programación:

El último paso del diseño es la programación y la depuración. La programación del chip se refiere a la generación de archivos de datos (archivos de flujo de bits, Bitstream Generaon) y a la carga de los datos de programación en el chip FPGA; después de eso, se puede llevar a cabo la prueba de la placa. Por último, descargue el archivo FPGA (como el archivo .bit) desde el ordenador al chip FPGA de la placa.

FPGA frente a CPU y GPU

Tanto las CPU como las GPU siguen la arquitectura von Neumann con decodificación de instrucciones y memoria compartida. Por el contrario, los FPGA tienen una arquitectura intrínsecamente diferente que no se basa en instrucciones ni requiere memoria compartida. La siguiente tabla muestra sus diferencias:

| Feature | FPGA | CPU | GPU |

|---|---|---|---|

| Architecture | Reconfigurable logic | Von Neumann | Von Neumann |

| Instruction | No instructions | Instructions | Instructions |

| Shared Memory | No shared memory | Arbitration and shared memory | Arbitration and shared memory |

| Parallel Processing | Pipeline and data parallelism | Data parallelism | Data parallelism |

| Flexibility | Reprogrammable | Fixed functionality | Fixed functionality |

| Computational Power | Suitable for complex tasks | General-purpose computing | Parallel computing and vector processing |

| Latency | Low latency | Medium latency | Relatively high latency |

| Power Consumption | High power consumption | Medium power consumption | High power consumption |

| Application Areas | Electronics, communication, embedded systems | General-purpose computing | Graphics processing, scientific computing |

Habilidades necesarias para los ingenieros de FPGA

- El lenguaje Verilog y su relación con los circuitos de hardware

- Herramientas de desarrollo (dominio de Synplify, vivodo, ISE, Modelsim)

- Familiarizado con el proceso de diseño FPGA (simulación, síntesis, diseño y enrutamiento, análisis de temporización)

- Competencia en la estimación de recursos (especialmente la estimación de slice, lut, ram y otros recursos)

- Competencia en conceptos básicos (como tiempo de configuración, tiempo de retención, cálculo de flujo, cálculo de tiempo de retardo, riesgo competitivo, métodos para eliminar fallos, etc.)

- Circuitos digitales (circuitos combinacionales, flip-flops, especialmente flip-flops D que constituyen un divisor de frecuencia, circuitos secuenciales y que pueden describirse en lenguaje Verilog)

Fabricantes de FPGA

- Xilinx: la plataforma de desarrollo es ISE, el inventor de FPGA;

- Altera: la plataforma de desarrollo es Quartus II, el inventor de los dispositivos lógicos programables;

- Actel: la plataforma de desarrollo es Libero;

- Lattice: la plataforma de desarrollo es ISPLEVER;

- Atmel