SWD und JTAG sind beliebte Debugging-Schnittstellen für MCUs auf Basis von Cortex-M. Diese beiden Schnittstellen unterscheiden sich jedoch sowohl in ihrer Struktur als auch in ihren Anwendungsbereichen. In diesem Artikel stellen wir ihre Pins, ihre Funktionsweise sowie ihre Vor- und Nachteile vor.

SWD-Schnittstelle

SWD (Serial Wire Debug) ist ein von ARM entwickeltes Protokoll zum Programmieren und Debuggen ihrer Mikrocontroller. Es basiert auf der ARM CoreSight-Debugging-Architektur und ermöglicht das Lesen und Schreiben von Chip-Registern über Datenpakete. SWD ist ein Zweidrahtprotokoll für den Zugriff auf ARM-Debugging-Schnittstellen. Es ist Teil der ARM Debug Interface Architecture Specification und dient als Alternative zu JTAG. In Fällen, in denen das PCB-Layout begrenzt ist und die Pin-Ressourcen eingeschränkt sind, ist SWD eine gute Wahl. Viele Debugger auf dem Markt unterstützen SWD-Debugging-Schnittstellen, wie z. B. ST-Link, J-Link, e-Link, GD-Link und andere.

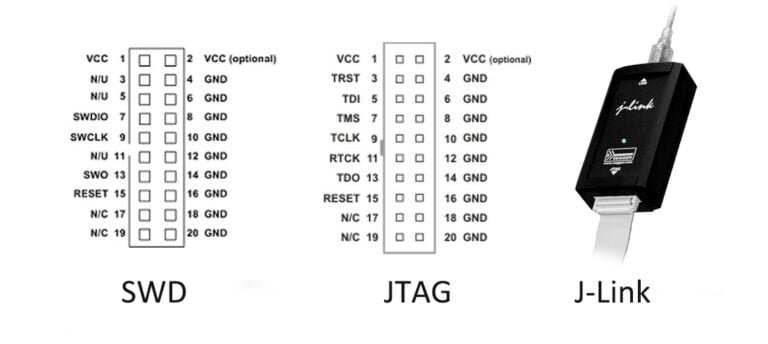

SWD-Stifte

SWDIO: Serial Wire Data Input Output, Pin für serielle

Dateneingabe und -ausgabe SWCLK: Serial Wire Clock, Pin für serielle Leitungstaktung

Bei SWDIO handelt es sich um einen bidirektionalen (Eingabe und Ausgabe) Daten-Pin, und die Leitung muss auf der Leiterplatte hochgezogen werden (ARM empfiehlt 100 K).

Wie funktioniert SWD?

Externe Geräte, wie Debug-Probes, werden an SWDIO/SWCLK angeschlossen, um direkt auf den Serial Wire Debug Port (SW-DP) zuzugreifen. SW-DP kann auf einen oder mehrere Access Ports (APs) zugreifen, und über die APs kann auf die übrigen Register des Systems zugegriffen werden. Ein wichtiger AP für CPUs der Cortex M-Serie ist der AHB-AP, der als Master auf dem internen AHB-Bus fungiert. Mit anderen Worten: Der AHB-AP kann auf die Speicherkarte des internen Kerns zugreifen. Da interne Flash-Speicher, SRAM, Debug-Komponenten und Peripheriegeräte alle speicherabgebildet sind, kann der AHB-AP das gesamte Gerät steuern, einschließlich seiner Programmierung. Der gesamte SWD-Betriebsprozess ist hierarchisch aufgebaut, wobei Taktsignale vom SWCLK-Pin und Datensignale vom SWDIO-Pin ein- und ausgegeben werden. Zunächst arbeitet der Debugger auf dem SW-DP, um die Parameter der AP-Register zu bestimmen, wodurch die Manipulation der Cortex-Speicherzuordnung ermöglicht wird.

Vorteile von SWD

- Reduzierte Signalanzahl

- Zuverlässigkeit bei hohen Geschwindigkeiten

- Reduzierte Ausfallwahrscheinlichkeit

- Kompatibilität mit JTAG-Simulationen

- Erfordert weniger Pins für den Betrieb

JTAG-Schnittstelle

JTAG (Joint Test Action Group) wurde ursprünglich zum Testen von Chips verwendet. Diese Gruppe initiierte Ende der 1980er Jahre Diskussionen und veröffentlichte 1990 offiziell Dokumente zur Auslegung der IEEE-Standards. (IEEE steht für Institute of Electrical and Electronics Engineers, eine internationale Organisation, die für die Veröffentlichung von Standards wie WiFi und Bluetooth zuständig ist.) Das von ihnen vorgeschlagene Protokoll wurde 1990 in IEEE 1149.1 dokumentiert. Dieses Dokument wurde seitdem überarbeitet und verbessert, wobei der aktuelle Standard zum Zeitpunkt der Erstellung dieses Artikels IEEE 1149.7 ist.

JTAG-Pins

- TDI: Testdaten-Eingang, ein serieller Eingangs-Pin.

- TDO: Testdatenausgang, ein serieller Ausgangspin.

- TCK: Test Clock, ein Takt-Pin.

- TMS: Test Mode Select, ein Modusauswahl-Pin (Steuersignal).

- TRST: Test Reset, ein Reset-Pin.

Wie funktioniert JTAG?

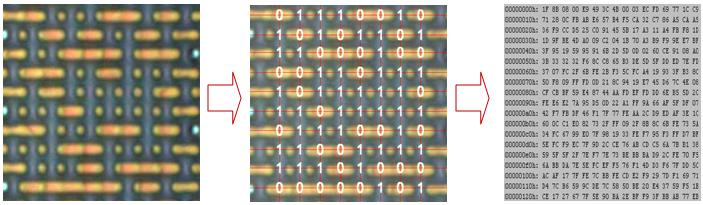

Das Prinzip von JTAG besteht darin, einen Testzugangsport (TAP) innerhalb des Geräts zu definieren. Dies ermöglicht das Testen interner Knoten mit speziellen JTAG-Testwerkzeugen. Durch JTAG-Tests können mehrere Geräte über eine JTAG-Schnittstelle in Reihe geschaltet werden, wodurch eine JTAG-Kette für das Testen einzelner Geräte entsteht. Heutzutage werden JTAG-Schnittstellen auch häufig für In-System-Programmiervorgänge (ISP) verwendet, beispielsweise zum Programmieren von FLASH-Geräten. In Bezug auf die Hardware-Struktur besteht die JTAG-Schnittstelle aus zwei Teilen: dem JTAG-Port und dem Controller. Mit der JTAG-Schnittstelle kompatible Geräte können Mikroprozessoren (MPUs), Mikrocontroller (MCUs), PLDs, CPLDs, FPGAs, DSPs, ASICs oder andere Chips sein, die den IEEE 1149.1-Spezifikationen entsprechen. IEEE 1149.1 schreibt vor, dass für jeden Pin eines digitalen integrierten Schaltkreischips eine Schieberegistereinheit namens Boundary Scan Unit (BSU) vorhanden sein muss. Diese verbindet die JTAG-Schaltung mit der Kernlogikschaltung und isoliert gleichzeitig die Kernlogikschaltung von den Pins des Chips. Alle Boundary Scan Units des Chips bilden zusammen das Boundary Scan Register (BSR). Die Boundary-Scan-Register-Schaltung ist nur während des JTAG-Tests aktiv und hat keinen Einfluss auf die Funktionalität des Chips im Normalbetrieb.

Das JTAG-Protokoll steuert den Übergang der TAP-Zustandsmaschine über das TMS-Signal. Nach dem Einschalten des Systems wechselt der TAP-Controller zunächst in den Zustand „Test-Logic Reset“ und durchläuft dann nacheinander die Zustände „Run-Test/Idle“, „Select-DR-Scan“, „Select-IR-Scan“, „Capture-IR“, „Shift-IR“, „Exit1-IR“ und „Update-IR“, bevor er wieder in den Zustand „Run-Test/Idle“ zurückkehrt. Während dieses Prozesses werden die Zustandsübergänge durch das TCK-Signal (steigende Flanke) gesteuert, wobei TMS-Signale zur Auswahl des TAP-Zustands verwendet werden. Im Capture-IR-Zustand wird eine bestimmte Logiksequenz in das Befehlsregister geladen; im Shift-IR-Zustand kann ein bestimmter Befehl in das Befehlsregister verschoben werden; und im Update-IR-Zustand wird der gerade in das Befehlsregister eingegebene Befehl zur Aktualisierung des Befehlsregisters verwendet. Schließlich kehrt das System in den Run-Test/Idle-Zustand zurück, in dem die Anweisung wirksam wird und der Zugriff auf die Anweisung und die Register abgeschlossen wird. Nach der Rückkehr in den Run-Test/Idle-Zustand wird auf der Grundlage des Inhalts des Befehlsregisters das erforderliche Datenregister ausgewählt und die Arbeit an den Datenregistern beginnt.

Vorteile von JTAG

- JTAG ist nicht auf ARM-Chips beschränkt, sondern wird auch von anderen Chips unterstützt, wie beispielsweise dem bekannten MSP430.

- JTAG hat ein breites Anwendungsspektrum für Programmierung, Debugging und Produktionstests.

- JTAG ist eine unabhängige Gruppe, die sich mit der Entwicklung des Protokolls weiterentwickelt.

Fazit

JTAG und SWD sind beide wichtige Schnittstellen für die Fehlersuche in eingebetteten Systemen, wobei jede ihre eigenen Stärken und Schwächen hat. Die Wahl der Schnittstelle hängt von den Projektanforderungen, der Hardwareunterstützung und den Leistungsanforderungen ab. Bei komplexen Systemen kann JTAG erforderlich sein, um mehr Kontrolle und Funktionalität zu erhalten, während SWD möglicherweise besser für Systeme mit begrenzten Ressourcen geeignet ist. Wenn Sie diese Faktoren gemeinsam berücksichtigen, können Sie fundierte Entscheidungen für eine effektivere Entwicklung und Fehlersuche in eingebetteten Systemen treffen.