Gambaran Umum MSP430F169

Mikrokontroler MSP430F169 merupakan salah satu anggota keluarga MSP430 dari Texas Instruments. Keluarga ini terdiri dari berbagai perangkat yang dilengkapi dengan rangkaian periferal yang berbeda-beda, yang dirancang untuk berbagai aplikasi. Arsitektur mikrokontroler ini, dikombinasikan dengan lima mode hemat daya, telah disesuaikan secara optimal untuk memperpanjang masa pakai baterai pada aplikasi pengukuran portabel. Selain itu, osilator yang dikendalikan secara digital (DCO) memungkinkan waktu bangun yang cepat, kurang dari 6 µs, dari mode hemat daya ke mode aktif.

Mikrokontroler ini umumnya digunakan dalam sistem sensor, aplikasi kontrol industri, alat ukur genggam, dan bidang serupa lainnya.

Fitur

- Konsumsi daya rendah;

- Lima mode hemat daya;

- DMA internal tiga saluran;

- Pemrograman serial onboard;

- Perlindungan kode yang dapat diprogram melalui fuse keamanan;

- Dilengkapi dengan detektor brownout dan bootstrap loader;

- Monitor tegangan suplai dengan deteksi level yang dapat diprogram.

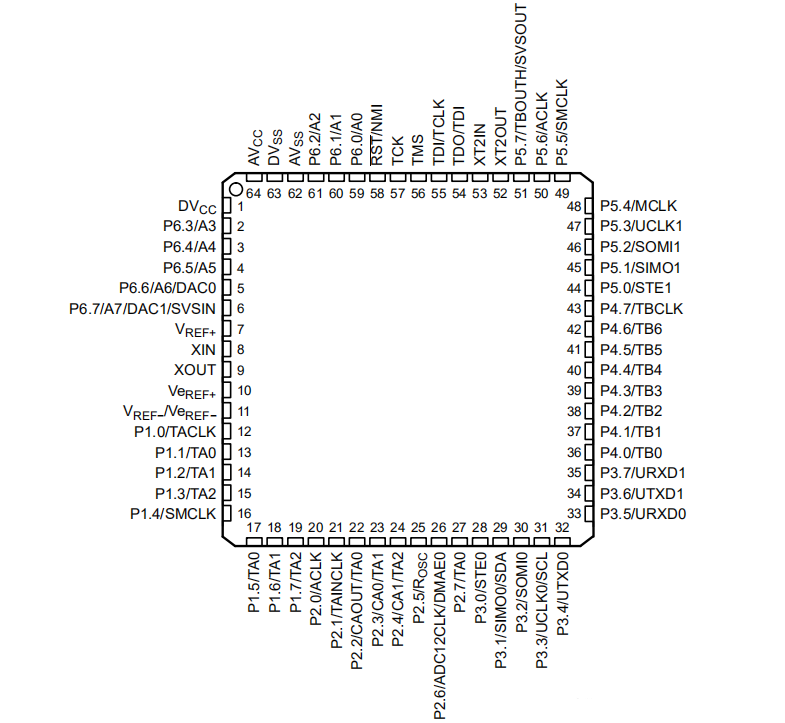

Konfigurasi Pin

MSP430F169 sebenarnya tersedia dalam versi 64-pin dan 100-pin, dengan konfigurasi pin yang berbeda untuk masing-masing versi.

Untuk versi 64-pin, beberapa pin utama meliputi:

| Pin Types | Pin Name | Description |

|---|---|---|

| Power Supply Pins | VCC | Positive supply voltage input |

| GND | Ground | |

| RST/NMI | Reset input and non-maskable interrupt | |

| TEST | Test mode input/output | |

| AVSS/AVCC | Ground and voltage reference for ADC | |

| DVSS/DVCC | Ground and voltage reference for digital circuitry | |

| Input/Output Pins | P1.x-P8.x | General-purpose I/O pins |

| Communication Pins | UCA0CLK | USART module A0 clock input/output |

| UCA0STE | USART module A0 STE input/output | |

| UCA0TXD | USART module A0 transmit data output | |

| UCA0RXD | USART module A0 receive data input | |

| UCB0CLK | SPI module B0 clock input/output | |

| UCB0STE | SPI module B0 STE input/output | |

| UCB0SIMO | SPI module B0 transmit data output | |

| UCB0SOMI | SPI module B0 receive data input | |

| UCB0SDA | I2C module B0 data input/output | |

| UCB0SCL | I2C module B0 clock input/output | |

| Timers and Counters | TA0CCR0-TA0CCR6 | Timer A0 capture/compare register 0-6 |

| Timer A0 control register | ||

| TB0CCR0-TB0CCR2 | Timer B0 capture/compare register 0-2 | |

| Timer B0 control register | ||

| Analog Pins | ADC12CLK | ADC12 clock input |

| ADC12MEM0-ADC12MEM15 | ADC12 memory register 0-15 | |

| AVREF+ | Positive reference voltage input for ADC | |

| AVREF- | Negative reference voltage input for ADC | |

| JTAG Pins | TCLK | Test clock input/output |

| TDI | Test data input | |

| TDO | Test data output | |

| Special Function Pins | ACLK | 32.768 kHz crystal oscillator input |

| SMCLK | System master clock output | |

| RTCCLK | Real-time clock input/output |

Spesifikasi

| Specification | Value |

|---|---|

| CPU | 16-bit RISC |

| Frequency | 8 MHz |

| Flash memory | 16 KB |

| RAM | 2 KB |

| Standby power | 1.1 µA |

| Active power | 330 µA at 1 MHz, 2.2 V |

| Wake-up time | in less than 6 µs |

| Instruction cycle time | 125 ns |

| Supply voltage | 1.8 V to 3.6 V |

| A/D converter | 12-bit |

| Timer/Counter | 2 * 16-bit |

| Operating Temp | -40 to 85 ℃ |

| DMA | 3 |

| I2C | 1 |

| SPI | 2 |

| Peripherals | timers, serial ports, I2C |

| Package | 64-pin QFP or 64-pin QFN |

Sistem Jam pada MSP430F169

Sistem jam sangat penting bagi mikrokomputer satu chip. Alasan mengapa mikrokomputer satu chip MSP430F169 memiliki konsumsi daya yang sangat rendah adalah karena ia dilengkapi dengan sistem jam yang sangat andal!

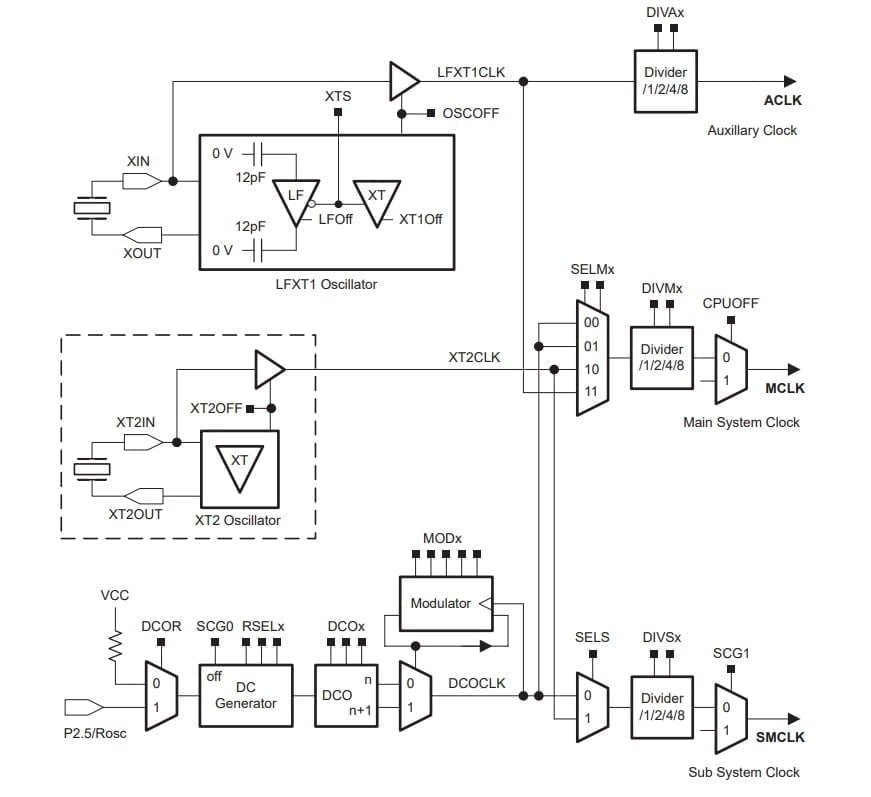

Tiga sumber sinyal jam

1. Frekuensi rendah LFXT1CLK (32,768 kHz)

Osilator kristal standar, osilator, atau sumber jam eksternal dapat digunakan untuk masukan frekuensi 4MHz hingga 32MHz. XT1CLK dapat digunakan sebagai jam referensi untuk modul FLL internal.

Osilator kristal frekuensi rendah (32,768KHz) terhubung langsung ke mikrokomputer chip tunggal melalui pin XIN dan XOUT, dan tidak diperlukan perangkat eksternal lainnya (ada kapasitansi beban 12pF di dalamnya). Pada saat ini, osilator LFXT1 bekerja dalam mode frekuensi rendah (XTS=0).

Jika mikrokontroler terhubung dengan osilator kristal berkecepatan tinggi atau resonator, pengaturan OSCOFF=0 dapat membuat osilator LFXT1 beroperasi dalam mode frekuensi tinggi (XTS=1). Pada saat ini, osilator kristal berkecepatan tinggi atau resonator dihubungkan melalui pin XIN dan XOUT, dan kapasitor eksternal diperlukan. Ukuran kapasitor dipilih sesuai dengan karakteristik osilator kristal atau resonator.

Jika sinyal LFXT1CLK tidak digunakan sebagai sinyal SMCLK atau MCIK, perangkat lunak dapat mengatur OSCOFF=1 untuk menonaktifkan LFXT1, sehingga mengurangi konsumsi daya mikrokontroler.

BCSCTL1:

XTS(BIT6)——Pemilihan mode kecepatan tinggi/rendah LFXT1. 0: LFXT1 bekerja dalam mode osilator kristal kecepatan rendah (default); 1: LFXT1 bekerja dalam mode osilator kristal kecepatan tinggi.

2. Sinyal frekuensi tinggi XT2CLK (8 MHz)

Oscillator kristal standar, oscillator, atau sumber clock eksternal dapat digunakan untuk masukan frekuensi 4MHz hingga 32MHz.

Osilator XT2 menghasilkan sinyal jam XT2CLK, dan karakteristik kerjanya mirip dengan osilator LFXT1 saat beroperasi dalam mode frekuensi tinggi. Jika XT2CLK tidak digunakan sebagai sinyal jam MCLK dan SMCLK, osilator XT2 dapat dinonaktifkan dengan bit kontrol XT2OFF.

BCSCTL1:

XT2OFF (BIT7) – Kontrol osilator kristal berkecepatan tinggi XT2. 0: Osilator kristal berkecepatan tinggi XT2 aktif; 1: Osilator kristal berkecepatan tinggi XT2 nonaktif.

3. Osilator internal DCOCLK (1 MHz)

Distabilkan oleh modul FLL.

Jika osilator gagal, DCO akan secara otomatis dipilih sebagai sumber clock untuk MCLK.

Frekuensi osilator DCO dapat disesuaikan dengan pengaturan perangkat lunak pada bit DCOx. MODx dan RSEL.x. Ketika sinyal DCOCLK tidak digunakan sebagai sinyal clock SMCLK dan MCLK, generator DC dapat dinonaktifkan dengan bit kontrol SCGO.

Setelah sinyal PUC, DCOCLK secara otomatis dipilih sebagai sinyal clock MCLK, dan sumber clock MCLK dapat diatur tambahan ke LFXT1 atau XT2 sesuai kebutuhan. Urutan pengaturan adalah sebagai berikut:

- Tetapkan OSCOFF=1;

- Atur OFIFG=0;

- Tunda dan tunggu setidaknya 50 ps;

- Periksa OFIFG lagi, jika OFIFG=1, ulangi langkah (3) dan (4) hingga OFIFG=0.

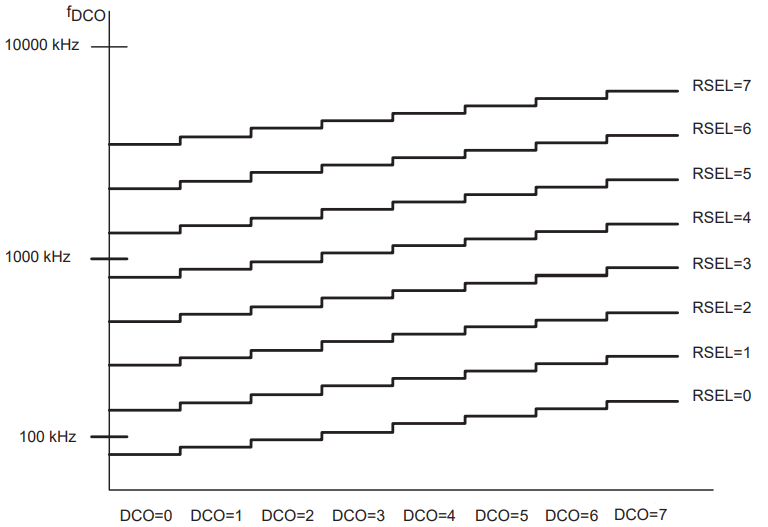

DCOCTL:

DCOx (BIT7, BIT6, BIT5)——Pemilihan frekuensi DCO, 8 jenis frekuensi dapat dipilih, dan frekuensi DCOCLK dapat disesuaikan secara bertahap. Pemilihan frekuensi didasarkan pada pita frekuensi yang dipilih oleh RSELx. Hubungan antara DCOx, RSELx, dan jam internal adalah sebagai berikut:

MODx (BIT4, BIT3, BIT2, BIT1, BIT0) – Pengaturan modulator DAC. Kontrol ini mengalihkan antara dua frekuensi yang dipilih oleh DCOx dan DCOx+1 untuk menyempurnakan frekuensi keluaran DCO. Jika nilai konstanta DCOx adalah 7, artinya frekuensi tertinggi telah dipilih. Pada saat ini, MODx tidak berlaku dan tidak dapat digunakan untuk penyesuaian frekuensi.

BCSCTL1:

RSELx (BIT2, BIT1, BIT0) – pemilihan pita frekuensi osilator DCO, 3 bit ini mengontrol resistansi internal untuk menentukan frekuensi nominal. 0: Pilih frekuensi nominal terendah… 7: Pilih frekuensi nominal tertinggi.

BCSCTL2:

DCOR(BIT0)——Pilih resistansi osilator DCO. 0: resistansi internal; 1: resistansi eksternal.

Tiga sumber sinyal jam

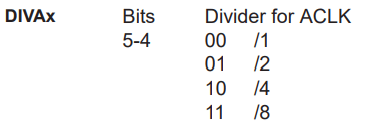

1. Jam bantu ACLK

ACLK diperoleh setelah LFXT1CLK dibagi dengan 1, 2, 4, dan 8. Sinyal ini dapat digunakan sebagai sinyal jam untuk setiap modul periferal dan umumnya digunakan untuk periferal berkecepatan rendah.

BCSCTL1:

DIVAx (BIT5, BIT4)——Pemilihan pembagian frekuensi ACLK, hubungan pemilihan pembagian frekuensi adalah sebagai berikut:

Definisi makro: DIVA_0 (1 pembagian frekuensi/tanpa pembagian frekuensi), DIVA_1 (2 pembagian frekuensi), DIVA_2 (4 pembagian frekuensi), DIVA_3 (8 pembagian frekuensi)

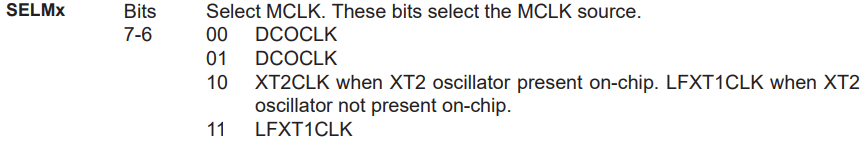

2. Jam utama sistem MCLK

MCLK dapat diperoleh dari LFXT1CLK, XT2CLK, dan DCOCLK setelah pembagian frekuensi dengan 1, 2, 4, dan 8. Sinyal ini sering digunakan untuk pengoperasian CPU, eksekusi program, dan modul-modul lain yang menggunakan clock berkecepatan tinggi.

BCSCTL2:

SELMx (BIT7, BIT6) – memilih sumber clock MCLK, hubungan pemilihan clock adalah sebagai berikut:

Definisi makro: SELM_0 (DCOCLK default), SELM_1 (DCOCLK), SELM_2 (XT2CLK), SELM_3 (LFXT1CLK)

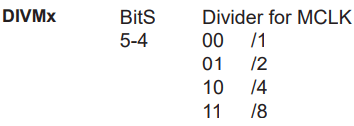

DIVMx (BIT5, BIT4) – Pemilihan pembagian frekuensi MCLK, hubungan pemilihan pembagian frekuensi adalah sebagai berikut:

Definisi makro: DIVM_0 (pembagian frekuensi 1/tanpa pembagian frekuensi), DIVM_1 (pembagian frekuensi 2), DIVM_2 (pembagian frekuensi 4), DIVM_3 (pembagian frekuensi 8)

3. Jam sistem SMCLK

SMCLK dapat diperoleh dengan membagi frekuensi XT2CLK dan DCOCLK dengan 1, 2, 4, dan 8, dan sering digunakan pada modul periferal berkecepatan tinggi.

BCSCTL2:

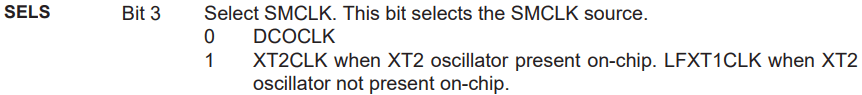

SELSx (BIT3) – pilih sumber clock MCLK, hubungan pemilihan clock adalah sebagai berikut:

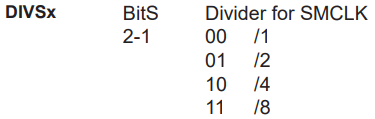

DIVSx (BIT2, BIT1) – Pemilihan pembagian frekuensi SMCLK; hubungan pemilihan pembagian frekuensi tersebut adalah sebagai berikut:

Definisi makro: DIVS_0 (pembagian frekuensi 1/tanpa pembagian frekuensi), DIVS_1 (pembagian frekuensi 2), DIVS_2 (pembagian frekuensi 4), DIVS_3 (pembagian frekuensi 8)