SWD dan JTAG adalah antarmuka debugging yang populer untuk MCU berbasis Cortex-M. Namun, kedua antarmuka ini berbeda baik dari segi struktur maupun aplikasinya. Dalam artikel ini, kami akan membahas pin-pinnya, prinsip kerjanya, serta kelebihan dan kekurangannya.

Antarmuka SWD

SWD (Serial Wire Debug) adalah protokol yang dirancang oleh ARM untuk pemrograman dan debugging mikrokontroler mereka. Protokol ini didasarkan pada arsitektur debugging ARM CoreSight dan memungkinkan pembacaan serta penulisan register chip melalui paket data. SWD adalah protokol dua kabel untuk mengakses antarmuka debugging ARM. SWD merupakan bagian dari Spesifikasi Arsitektur Antarmuka Debug ARM dan berfungsi sebagai alternatif untuk JTAG. Dalam kasus di mana tata letak PCB terbatas dan sumber daya pin terbatas, SWD merupakan pilihan yang baik. Banyak debugger di pasaran yang mendukung antarmuka debugging SWD, seperti ST-Link, J-Link, e-Link, GD-Link, dan lainnya.

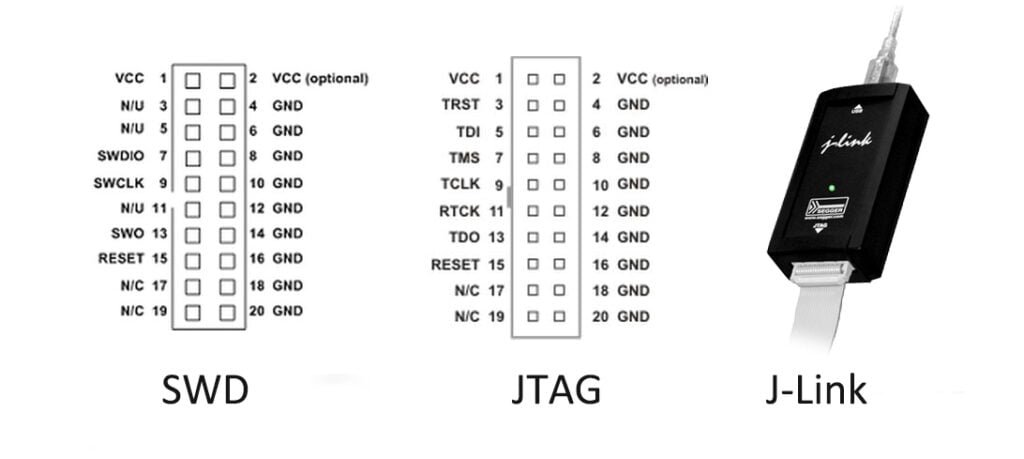

Pin SWD

SWDIO: Serial Wire Data Input Output, pin masukan dan keluaran

data serial SWCLK: Serial Wire Clock, pin jam jalur serial

Untuk SWDIO, ini adalah pin data dua arah (masukan dan keluaran), dan jalur tersebut harus ditarik ke atas pada papan sirkuit (ARM merekomendasikan 100 K).

Bagaimana Cara Kerja SWD?

Perangkat eksternal, seperti probe debug, terhubung ke SWDIO/SWCLK untuk mengakses Serial Wire Debug Port (SW-DP) secara langsung. SW-DP dapat mengakses satu atau beberapa Access Port (AP), dan melalui AP tersebut, register-register lain dalam sistem dapat diakses. AP yang penting untuk CPU seri Cortex M adalah AHB-AP, yang berfungsi sebagai master pada bus AHB internal. Dengan kata lain, AHB-AP dapat mengakses peta memori inti internal. Karena flash internal, SRAM, komponen debug, dan perangkat periferal semuanya dipetakan ke memori, AHB-AP dapat mengontrol seluruh perangkat, termasuk memprogramnya. Seluruh proses operasi SWD bersifat hierarkis, dengan sinyal clock yang dimasukkan dari pin SWCLK, dan sinyal data yang dimasukkan/dikeluarkan dari pin SWDIO. Awalnya, debugger beroperasi pada SW-DP untuk menentukan parameter register AP, sehingga memungkinkan manipulasi Peta Memori Cortex.

Keunggulan SWD

- Jumlah Sinyal Berkurang

- Keandalan pada Kecepatan Tinggi

- Kemungkinan kegagalan yang lebih rendah

- Kompatibilitas dengan Simulasi JTAG

- Membutuhkan lebih sedikit pin untuk pengoperasian

Antarmuka JTAG

JTAG (Joint Test Action Group) awalnya digunakan untuk menguji chip. Kelompok ini memulai diskusi pada akhir tahun 1980-an dan secara resmi menerbitkan dokumen yang menafsirkan standar IEEE pada tahun 1990. (IEEE adalah singkatan dari Institute of Electrical and Electronics Engineers, sebuah organisasi internasional yang bertanggung jawab atas penerbitan standar seperti WiFi dan Bluetooth.) Protokol yang mereka usulkan didokumentasikan dalam IEEE 1149.1 pada tahun 1990. Dokumen ini telah mengalami revisi dan perbaikan, dengan standar terbaru pada saat penulisan ini adalah IEEE 1149.7.

Pin JTAG

- TDI: Masukan Data Uji, pin masukan serial.

- TDO: Keluaran Data Uji, pin keluaran serial.

- TCK: Jam Uji, pin jam.

- TMS: Pemilihan Mode Uji, pin pemilihan mode (sinyal kontrol).

- TRST: Reset Uji, pin reset.

Bagaimana Cara Kerja JTAG?

Prinsip JTAG melibatkan penetapan Test Access Port (TAP) di dalam perangkat. Hal ini memungkinkan pengujian simpul internal menggunakan alat uji JTAG khusus. Pengujian JTAG memungkinkan beberapa perangkat dihubungkan secara seri melalui antarmuka JTAG, sehingga membentuk rantai JTAG untuk pengujian perangkat secara individual. Saat ini, antarmuka JTAG juga umum digunakan untuk operasi In-System Programmable (ISP), seperti pemrograman perangkat FLASH. Dari segi struktur perangkat keras, antarmuka JTAG terdiri dari dua bagian: port JTAG dan pengontrol. Perangkat yang kompatibel dengan antarmuka JTAG dapat berupa mikroprosesor (MPU), mikrokontroler (MCU), PLD, CPLD, FPGA, DSP, ASIC, atau chip lain yang sesuai dengan spesifikasi IEEE 1149.1. IEEE 1149.1 mewajibkan adanya unit register geser yang disebut Boundary Scan Unit (BSU) untuk setiap pin pada chip sirkuit terpadu digital. Unit ini menghubungkan sirkuit JTAG dengan sirkuit logika inti sambil mengisolasi sirkuit logika inti dari pin-pin chip. Semua Boundary Scan Unit pada chip tersebut membentuk Boundary Scan Register (BSR). Sirkuit Boundary Scan Register hanya aktif selama pengujian JTAG dan tidak memengaruhi fungsi chip selama operasi normal.

Protokol JTAG mengendalikan transisi mesin keadaan TAP melalui sinyal TMS. Setelah sistem dinyalakan, pengontrol TAP pertama-tama masuk ke keadaan Test-Logic Reset, kemudian secara berurutan beralih melalui keadaan Run-Test/Idle, Select-DR-Scan, Select-IR-Scan, Capture-IR, Shift-IR, Exit1-IR, dan Update-IR sebelum kembali ke Run-Test/Idle. Selama proses ini, transisi keadaan didorong oleh sinyal TCK (tepi naik), dengan sinyal TMS digunakan untuk memilih keadaan TAP. Pada keadaan Capture-IR, urutan logika tertentu dimuat ke dalam register instruksi; pada keadaan Shift-IR, instruksi tertentu dapat dipindahkan ke dalam register instruksi; dan pada keadaan Update-IR, instruksi yang baru saja dimasukkan ke dalam register instruksi digunakan untuk memperbarui register instruksi. Akhirnya, sistem kembali ke keadaan Run-Test/Idle, di mana instruksi mulai berlaku, menyelesaikan akses ke instruksi dan register. Setelah kembali ke keadaan Run-Test/Idle, berdasarkan isi register instruksi, register data yang diperlukan dipilih, dan pemrosesan pada register data dimulai.

Keunggulan JTAG

- JTAG tidak terbatas pada chip ARM; teknologi ini juga didukung pada chip di luar ARM, seperti MSP430 yang terkenal.

- JTAG memiliki berbagai macam aplikasi untuk pemrograman, debugging, dan pengujian produksi.

- JTAG adalah kelompok independen yang terus berkembang seiring dengan perkembangan protokolnya.

Kesimpulan

JTAG dan SWD sama-sama merupakan antarmuka debugging sistem tertanam yang penting, masing-masing dengan kelebihan dan kekurangannya sendiri. Pilihan antarmuka bergantung pada persyaratan proyek, dukungan perangkat keras, dan kebutuhan kinerja. Untuk sistem yang kompleks, JTAG mungkin diperlukan untuk mendapatkan kontrol dan fungsionalitas yang lebih besar, sementara SWD mungkin lebih cocok untuk sistem dengan sumber daya terbatas. Mempertimbangkan faktor-faktor ini secara menyeluruh dapat membantu Anda mengambil keputusan yang tepat guna pengembangan dan debugging sistem tertanam yang lebih efektif.