Da die Ausgangsgeschwindigkeit integrierter Schaltkreise zunimmt und die Dichte von Leiterplatten steigt, ist die Signalintegrität zu einem der Themen geworden, die beim Entwurf von digitalen Hochgeschwindigkeits-Leiterplatten berücksichtigt werden müssen. Da Probleme mit der Signalintegrität dazu führen können, dass das System falsche Daten ausgibt, funktioniert die Schaltung nicht richtig oder sogar überhaupt nicht mehr. Wie kann also der Faktor der Signalintegrität beim Entwurf von Leiterplatten vollständig berücksichtigt und wirksame Kontrollmaßnahmen ergriffen werden? Lesen Sie diesen Artikel weiter.

Was ist PCB-Signalintegrität?

Die Signalintegrität einer Leiterplatte bezieht sich auf die Fähigkeit des Signals, mit dem richtigen Timing und der richtigen Spannung im Schaltkreis zu reagieren. Es handelt sich um einen Zustand, in dem das Signal nicht beschädigt ist, und er gibt Aufschluss über die Qualität des Signals auf der Signalleitung.

Verschiedene Probleme mit der Signalintegrität

Signalintegritätsprobleme können Signalverzerrungen, Timing-Fehler, fehlerhafte Daten, Adress- und Steuerleitungen, Systemfehlfunktionen und sogar Systemabstürze verursachen oder direkt hervorrufen. Zu den wichtigsten Signalintegritätsproblemen zählen: Verzögerung, Reflexion, synchrones Schaltrauschen, Oszillation, Ground Bounce, Übersprechen usw.

Verzögerung

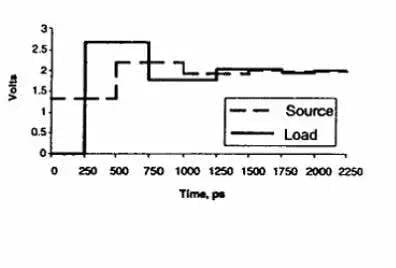

Verzögerung bedeutet, dass das Signal mit begrenzter Geschwindigkeit über die Leiterbahnen der Leiterplatte übertragen wird und dass zwischen dem Sende- und dem Empfangsende eine Übertragungsverzögerung auftritt. Die Verzögerung des Signals wirkt sich auf das Timing des Systems aus, wobei die Übertragungsverzögerung hauptsächlich von der Länge der Leiterbahn und der Dielektrizitätskonstante des Mediums um die Leiterbahn herum abhängt. In einem digitalen Hochgeschwindigkeitssystem ist die Länge der Signalübertragungsleitung der direkteste Faktor, der die Taktimpulsphasenverschiebung beeinflusst. Die Taktimpuls-Phasendifferenz bedeutet, dass die beiden gleichzeitig erzeugten Taktsignale nicht synchronisiert sind, wenn sie am Empfangsende ankommen. Die Taktimpuls-Phasendifferenz verringert die Vorhersagbarkeit des Signalkantenankommens. Wenn die Taktimpuls-Phasendifferenz zu groß ist, wird am Empfangsende ein fehlerhaftes Signal erzeugt. Wie in der Abbildung unten gezeigt, ist die Übertragungsleitungsverzögerung zu einem wichtigen Teil des Taktimpulszyklus geworden.

Reflexion

Reflexion ist das Echo auf der Unterübertragungsleitung. Wenn die Signalverzögerungszeit viel länger ist als die Signalübergangszeit, muss die Signalleitung als Übertragungsleitung betrachtet werden. Wenn die charakteristische Impedanz der Übertragungsleitung nicht mit der Lastimpedanz übereinstimmt, wird ein Teil der Signalleistung (Spannung oder Strom) auf der Leitung übertragen und erreicht die Last, ein Teil wird jedoch reflektiert. Wenn die Lastimpedanz geringer ist als die ursprüngliche Impedanz, ist die Reflexion negativ. Andernfalls ist die Reflexion positiv. Schwankungen in der Routing-Geometrie, eine unsachgemäße Abschlusswiderstand der Übertragungsleitung, die Übertragung durch Steckverbinder und Diskontinuitäten in den Stromversorgungsebenen können solche Reflexionen verursachen.

Simultane Schaltgeräusche (SSN)

Das simultane Schaltgeräusch entsteht, wenn viele digitale Signale auf der Leiterplatte synchron geschaltet werden (z. B. CPU-Datenbus, Adressbus usw.). Dies liegt daran, dass die Stromleitung und die Masse impedanzbehaftet sind und es zu einem Ground-Bounce-Geräusch (Erdungsrückprall) kommt. Die Stärke von SSN und Ground Bounce hängt auch von den I/O-Eigenschaften der integrierten Schaltung, der Impedanz der Stromversorgungs- und Ebenenschicht der Leiterplatte sowie dem Layout und der Verdrahtung von Hochgeschwindigkeitsgeräten auf der Leiterplatte ab.

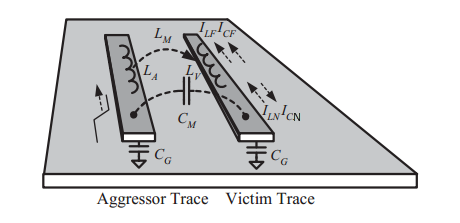

Übersprechen

Übersprechen ist die Kopplung zwischen zwei Signalleitungen, wobei die gegenseitige Induktivität und Kapazität zwischen den Signalleitungen Störungen auf der Leitung verursachen. Kapazitive Kopplung induziert einen gekoppelten Strom, während induktive Kopplung eine gekoppelte Spannung induziert. Übersprechungsstörungen entstehen durch elektromagnetische Kopplung zwischen Signalenetzen, zwischen Signalsystemen und Stromverteilungssystemen sowie zwischen Durchkontaktierungen. Cross-Winding kann zu falschen Takten, intermittierenden Datenfehlern usw. führen und die Übertragungsqualität benachbarter Signale beeinträchtigen. Tatsächlich müssen wir Crosstalk nicht vollständig eliminieren, sondern nur innerhalb der Toleranz des Systems halten. Die Parameter der PCB-Leiterplattenlage, der Abstand der Signalleitungen, die elektrischen Eigenschaften des Treibers und Empfängers sowie die Basisleitungsabschlussmethode haben alle einen gewissen Einfluss auf Crosstalk.

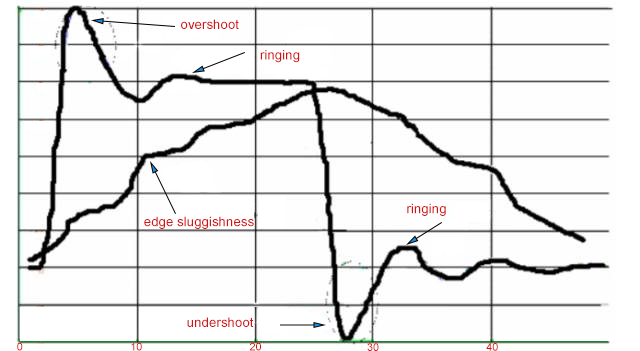

Überschreitung und Unterschreitung

Overshoot ist der erste Spitzen- oder Talwert, der die eingestellte Spannung überschreitet. Bei steigenden Flanken bezieht sich dies auf die höchste Spannung, bei fallenden Flanken auf die niedrigste Spannung. Undershoot liegt vor, wenn der nächste Tal- oder Spitzenwert die eingestellte Spannung überschreitet. Ein übermäßiger Overshoot kann dazu führen, dass Schutzdioden aktiviert werden, was zu deren vorzeitigem Ausfall führt. Ein übermäßiger Undershoot kann zu falschen Takt- oder Datenfehlern (Fehlfunktionen) führen.

Klingeln und Runden

Das Schwingungsphänomen wiederholt sich in Form von Überschwingungen und Unterschwingungen. Die Schwingung des Signals ist die Schwingung, die durch die Übergangsinduktivität und -kapazität auf der Leitung verursacht wird und zum unterdämpften Zustand gehört. Die Umgebungs-Schwingung ist ein überdämpfter Zustand. Schwingungen und Orbitalschwingungen werden, wie Reflexionen, durch eine Vielzahl von Faktoren verursacht. Schwingungen können durch eine ordnungsgemäße Terminierung reduziert, aber nicht vollständig beseitigt werden.

Bodenrückkopplungsrauschen und Rückkopplungsrauschen

Bodenreflexionsrauschen

Wenn es zu einem starken Stromstoß im Schaltkreis kommt, verursacht dies ein Ground-Plane-Bounce-Rauschen. Wenn beispielsweise die Ausgänge einer großen Anzahl von Chips gleichzeitig eingeschaltet werden, fließt ein großer transienter Strom durch die Stromversorgungsebene des Chips und der Platine. Durch die Induktivität und den Widerstand des Chipgehäuses und der Stromversorgungsfläche wird dann ein Stromversorgungsrauschen induziert, das zu Spannungsschwankungen und Abweichungen auf der tatsächlichen Massefläche (O V) führt. Dieses Rauschen beeinträchtigt den Betrieb anderer Komponenten. Eine Erhöhung der Lastkapazität, eine Verringerung des Lastwiderstands, eine Erhöhung der Masseinduktivität und eine Erhöhung der Anzahl der Schaltgeräte führen zu einer Zunahme des Masse-Bounce.

Rücklaufgeräusch

Erdungsflächenrücklaufrauschen entsteht, wenn digitale Signale zum analogen Erdungsbereich gelangen. Dies kann durch die Aufteilung der Massefläche (einschließlich Stromversorgung und Masse) verursacht werden, beispielsweise wenn die Massefläche in digitale Masse, analoge Masse, Abschirmungsmasse usw. unterteilt ist. Ebenso können Stromversorgungsflächen in 2,5 V, 3,3 V, 5 V usw. unterteilt sein. Daher müssen wir bei der Entwicklung von Mehrspannungs-Leiterplatten besonders auf das Sprungrauschen und das Rückflussrauschen der Massefläche achten.

Ursachen für Probleme mit der Signalintegrität

Faktoren wie die Parameter von Bauteilen und Leiterplatten, die Anordnung der Bauteile auf Leiterplatten und die Verdrahtung von Hochgeschwindigkeitssignalleitungen verursachen Probleme mit der Signalintegrität. Für das Leiterplattenlayout muss die Signalintegrität Folgendes bieten: Für das Schaltungslayout erfordert die Signalintegrität Abschlussbauteile, Platzierungsstrategien und Routing-Informationen.

Wie lässt sich die Signalintegrität optimieren?

Das Problem der Signalintegrität wird nicht durch einen einzigen Faktor verursacht, sondern durch mehrere Faktoren im Design auf Board-Ebene. Daher müssen wir je nach Situation unterschiedliche Methoden anwenden, um die Signalintegrität zu verbessern.

Übersprechungsanalyse

Die Größe des Übersprechens ist umgekehrt proportional zum Zeilenabstand und proportional zur parallelen Länge der Zeile und zur Signalfrequenz. Das Übersprechen variiert mit der Schaltungsbelastung. Bei gleicher Topologie und Verdrahtungssituation ist das Übersprechen umso größer, je größer die Belastung ist. In digitalen Schaltungen hat die Flankenänderung des Signals den größten Einfluss auf das Übersprechen, und je schneller sich die Flanken ändern, desto größer ist das Übersprechen. Angesichts der oben genannten Eigenschaften von Übersprechen können wir die folgenden Methoden anwenden, um Übersprechen zu reduzieren:

- Wählen Sie ein langsames Gerät, um die Übergangsrate der Signalflanke zu reduzieren.

- Vermeiden Sie die Vermischung verschiedener Signaltypen.

- Reduzieren Sie Kopplungsstörungen durch Verringerung der Last.

- Minimieren Sie die parallele Länge zwischen benachbarten Übertragungsleitungen.

- Erhöhen Sie den Abstand zwischen Leitern, bei denen es zu kapazitiver Kopplung kommen kann.

- Ein wirksamerer Ansatz besteht darin, die Drähte mit Erdungsdrähten zu isolieren.

- Fügen Sie einen Erdungsdraht zwischen benachbarten Signaldrähten ein.

- Minimieren Sie die Anzahl der Schleifen und die Schleifenfläche.

- Vermeiden Sie die gemeinsame Nutzung desselben Kabels für die Signalleitung.

- Die Signallagen zweier benachbarter Lagen sollten eine parallele Verdrahtung so weit wie möglich vermeiden.

- Signale, die empfindlich gegenüber Übersprechen sind, sollten so weit wie möglich in der inneren Schicht angeordnet werden.

Reflexionsanalyse

Reflexionen treten immer dann auf, wenn ein Signal auf seiner Reise entlang einer Übertragungsleitung auf eine Impedanzänderung trifft. Das Reflexionsproblem lässt sich hauptsächlich durch eine Anpassung der Abschlussimpedanz lösen. Für den Abschluss der Übertragungsleitung gibt es in der Regel zwei Strategien: den parallelen Abschluss und den seriellen Abschluss.

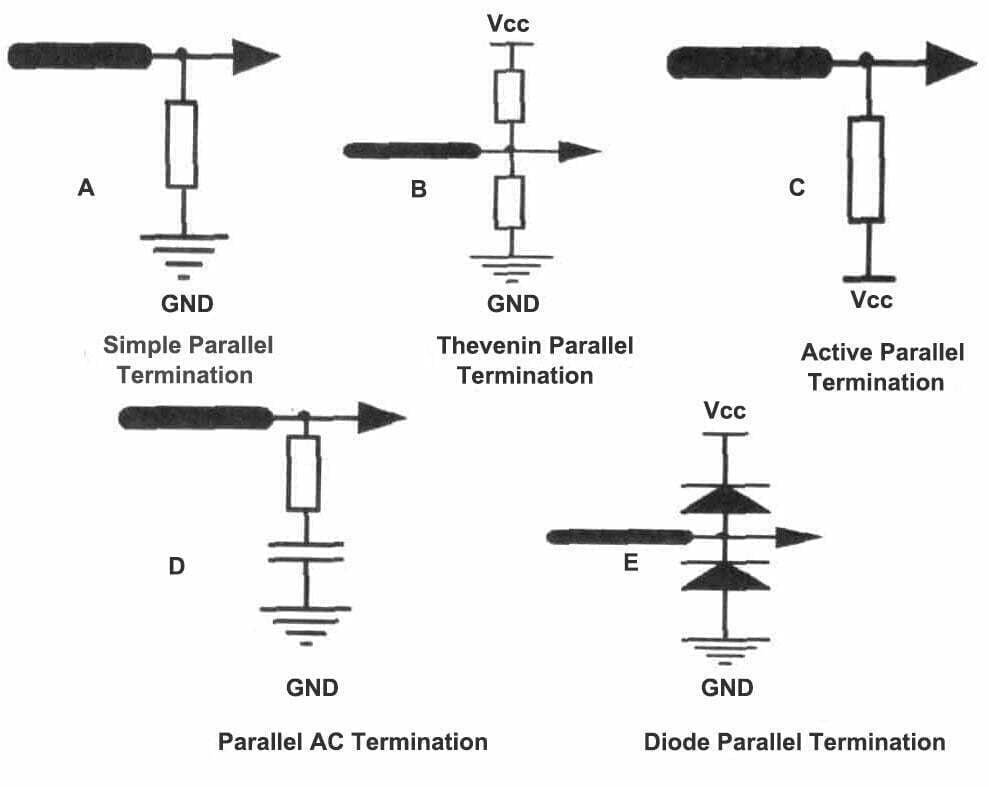

Parallele Terminierung

Die parallele Terminierung dient hauptsächlich dazu, die Pull-up- oder Pull-down-Impedanz so nah wie möglich an das Lastende anzuschließen, um eine Impedanzanpassung des Anschlusses zu erreichen. Je nach Anwendungsumgebung kann die parallele Terminierung in verschiedene Typen unterteilt werden, wie in der folgenden Abbildung dargestellt.

Serielle Terminierung

Die serielle Terminierung wird durch das serielle Einfügen eines Widerstands in die Übertragungsleitung so nah wie möglich an der Quelle erreicht. Die serielle Terminierung dient dazu, die Impedanz der Signalquelle anzupassen. Der Widerstand des eingefügten seriellen Widerstands plus die Ausgangsimpedanz der treibenden Quelle sollte größer oder gleich der Impedanz der Übertragungsleitung sein. Diese Strategie unterdrückt das von der Last reflektierte Signal, indem sie den Reflexionskoeffizienten des Quellenendes auf Null setzt (der Eingang des Lastendes ist hochohmig und absorbiert keine Energie) und dann vom Quellenende zum Lastende zurückreflektiert.

Modellierung der Signalintegritätsanalyse

Die richtige Schaltungsmodellierung und -simulation ist die gängigste Lösung für die Signalintegrität. Bei der Entwicklung von Hochgeschwindigkeitsschaltungen zeigt die Simulationsanalyse zunehmend ihre Überlegenheit. Denn sie kann Designern genaue und intuitive Designergebnisse liefern. Auf diese Weise können wir Probleme frühzeitig erkennen und rechtzeitig beheben. Es gibt drei häufig verwendete Methoden zur Schaltungsmodellierung: SPICE-Modell, IBIS-Modell und Verilog-A-Modell.

SPICE-Modell

SPICE ist ein leistungsstarker Allzweck-Analogschaltungssimulator. Er besteht aus zwei Teilen: Modellgleichung und Modellparameter. Da die Modellgleichung bereitgestellt wird, kann das SPICE-Modell sehr eng mit dem Algorithmus des Simulators verbunden werden, wodurch eine bessere Analyseeffizienz und bessere Analyseergebnisse erzielt werden können.

IBIS-Modell

Das IBIS-Modell ist ein Modell, das speziell für die Analyse der digitalen Signalintegrität auf PCB-Board-Ebene und Systemebene verwendet wird. Es verwendet die Form von I/V- und V/T-Tabellen, um die Eigenschaften von digitalen integrierten Schaltkreis-I/O-Zellen und Pins zu beschreiben. Die Analysegenauigkeit des IBIS-Modells hängt hauptsächlich von der Anzahl der Datenpunkte und der Genauigkeit der Daten in den 1/V- und V/T-Tabellen ab. Im Vergleich zum SPICE-Modell ist die Rechenlast des IBIS-Modells sehr gering.

Fazit

Mit der kontinuierlichen Weiterentwicklung der Mikroelektroniktechnologie nehmen der Einsatz von Hochgeschwindigkeitsgeräten und die Entwicklung von digitalen Hochgeschwindigkeitssystemen zu. Auch die Datenraten, Taktraten und Schaltungsdichten der Systeme steigen. Daher werden die Anforderungen an die Entwicklung von Leiterplatten immer höher, insbesondere hinsichtlich der Signalintegrität. Um eine gute Signalintegrität der Leiterplatte zu gewährleisten, müssen verschiedene Einflussfaktoren umfassend berücksichtigt werden.