Entegre devre nedir?

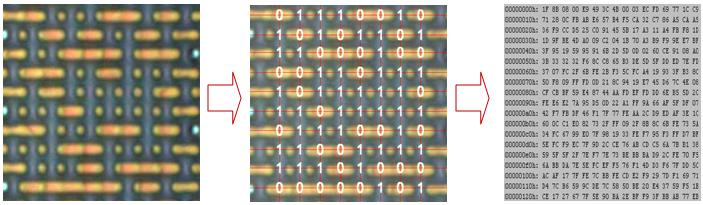

Entegre devre (IC), tek bir yarı iletken çip üzerine inşa edilmiş bir elektronik devredir. Bilgisayarlarda, cep telefonlarında ve diğer elektronik cihazlarda en yaygın olarak kullanılan elektronik cihaz türüdür. Genel olarak bir IC, binlerce veya milyonlarca transistör, direnç ve diğer devre kartı bileşenlerini içeren, yaklaşık 3 mm² büyüklüğünde küçük bir silikon parçasıdır. Bu tür minyatür devreler, bileşenlerin ayrı ayrı inşa edilmesine kıyasla çok daha küçük bir boyutta ve daha yüksek verimlilikle çeşitli işlevlerin yerine getirilmesini sağlar.

Entegre devrenin bileşenleri

Entegre devreler, her biri belirli bir işlevi yerine getiren çeşitli bileşenlerden oluşur. Bu bileşenler genellikle devrenin farklı bölümleri arasında elektrik sinyallerini iletmek için kullanılan minik metal izlerle birbirine bağlanır. Bileşenler genellikle çok küçüktür ve boyutları birkaç mikrometreden birkaç milimetreye kadar değişir. Bu sayede tek bir çip üzerine çok sayıda bileşen yerleştirilebilir ve böylece daha yüksek düzeyde karmaşıklık ve işlevsellik sağlanır.

Entegre devrelerin avantajları

Entegre devreler, elektronik cihazlarımızın karmaşıklığını ve işlevselliğini artırmamızı sağlayan güçlü araçlardır. Birden fazla bileşeni tek bir çip üzerine yerleştirerek, bir cihaz için gereken yer ihtiyacını azaltabiliriz. Bu da maliyetleri düşürür ve cihazın verimliliğini artırır. Bileşenlerin entegrasyonu ayrıca elektromanyetik paraziti azaltmaya yardımcı olarak elektronik cihazlarımızın daha güvenilir bir şekilde çalışmasını sağlar. Entegre devreler, modern elektroniğin temelini oluşturur ve günlük hayatımız için vazgeçilmezdir.

Entegre devrelerin kullanım alanları

Entegre devreler, modern elektronik cihazların çoğunun temelini oluşturur. Bilgisayarlarda, cep telefonlarında, televizyonlarda, radyolarda ve diğer birçok elektronik cihazda kullanılırlar. Ayrıca çamaşır makineleri, mikrodalga fırınlar ve bulaşık makineleri gibi ev aletlerinde de bulunurlar. Bunun yanı sıra, tıbbi cihazlarda, endüstriyel makinelerde ve otomotiv sistemlerinde de giderek daha fazla kullanılmaktadır.

IC Tasarım Sürecine Genel Bakış

IC tasarımı, elektronik devrelerin tasarlanmasına yönelik karmaşık bir süreçtir. Bu süreç, ön uç tasarımı, arka uç tasarımı ve son montaj gibi çeşitli aşamaları içerir. Süreç son derece yinelemeli bir yapıya sahiptir ve tasarımın gerekli tüm teknik özellikleri karşıladığından emin olmak için tasarımcı ile mühendisler arasında yakın bir işbirliği gerektirir. Sürecin her aşamasında, tasarımların beklendiği gibi çalıştığını test etmek ve doğrulamak amacıyla prototipler oluşturulur.

Ön uç tasarımı

Entegre devrelerin ön uç tasarımı, transistörler, dirençler ve kondansatörler gibi bir entegre devrenin (IC) temel bileşenlerini tasarlama sürecidir. Bu işlem, şematik çizim, mantık sentezi ve yerleşim yazılımı gibi çeşitli araçlar kullanılarak gerçekleştirilir. Ön uç tasarımının amacı, istenen teknik özellikleri karşılayan bir IC oluşturmaktır.

IC Teknik Özellikleri

IC tasarımının teknik özellikleri, devrenin içermesi gereken temel bileşenleri ve özellikleri tanımlar. Bu özellikler, tüm tasarım sürecinin üzerine inşa edileceği temeli oluşturur. Teknik özellikler, başarılı bir IC tasarımı oluşturmak için gerekli tüm gereklilikleri kapsayabilmelidir. Ayrıca, sektörün değişen ihtiyaçlarına ve teknolojilerine uyum sağlayabilmelidir. Doğru IC teknik özellikleri, verimli ve etkili bir tasarım süreci için hayati öneme sahiptir; bu nedenle, başarıyı garantilemek için bu özelliklerin doğru bir şekilde belirlenmesini sağlamak önemlidir.

Ayrıntılı tasarım

Fabless, müşterinin belirlediği teknik şartname gerekliliklerine uygun olarak bir tasarım çözümü ve özel bir uygulama mimarisi geliştirir ve modül işlevlerini bölümlere ayırır.

HDL kodlaması

HDL, entegre devre tasarımı için kullanılan güçlü bir donanım tanımlama dilidir. Karmaşık tasarımları tanımlamak için verimli bir yol sunar ve tasarımın işlevselliğinin erken aşamada doğrulanmasını sağlar. HDL, endüstride yaygın olarak kullanılır ve bu da onu modern entegre devre tasarımcıları için vazgeçilmez bir teknoloji haline getirir. HDL'nin esnekliği ve ölçeklenebilirliği, onu çeşitli uygulamalarda ve çoklu platformlarda kullanım için avantajlı kılar. Bu, tasarımcıların kendi özel ihtiyaçlarına uygun, verimli ve kapsamlı IC tasarımları geliştirmelerini sağlar. HDL, herhangi bir IC tasarım projesinin başarısında kritik bir araçtır ve başarılı bir entegre devre oluşturmak isteyen her tasarımcı tarafından kullanımı ciddi olarak değerlendirilmelidir.

Simülasyon doğrulaması

Simülasyon doğrulaması, IC tasarım sürecinde vazgeçilmez bir adımdır. Tasarımcıların geliştirme aşamasında olası hataları ve tasarım kusurlarını tespit etmelerine yardımcı olur. Bu süreç, IC tasarımlarının gerekli teknik özelliklere ve standartlara uygunluğunu sağlamak amacıyla simülasyonlar ve testler yapılmasını içerir. Simülasyon doğrulaması, hataları tespit etmek, tasarım sorunlarını çözmek ve IC tasarımının performansını optimize etmek açısından faydalıdır. Ayrıca, tasarımcıların IC tasarımlarının gerçek dünya koşullarında nasıl davranacağını daha iyi anlamalarını sağlar. Bu nedenle simülasyon doğrulama, IC tasarımlarının üretime geçmeden önce güvenilirliğini sağlamada önemli bir rol oynar.

(simülasyon doğrulama aracı: Synopsys'in VCS ve Cadence'in NC-Verilog.)

Mantık sentezi——Design Compiler

Simülasyon doğrulaması başarıyla tamamlandı ve mantık sentezi gerçekleştirildi. Mantık sentezinin amacı, tasarlanan ve uygulanan HDL kodunu kapı düzeyinde bir ağ listesine dönüştürmektir. Sentez işlemi sırasında, sentezlenen devrenin alan ve zamanlama gibi hedef parametreler açısından uymasını istediğiniz standartları ifade eden kısıtlamaların belirlenmesi gerekir. Mantık sentezi, belirli bir kapsamlı kütüphaneye dayalı olmalıdır. Farklı kütüphanelerde, kapı devresinin temel standart hücresinin (standart hücre) alanı ve zamanlama parametreleri farklıdır.

Bu nedenle, seçilen kapsamlı kütüphaneler farklıdır ve sentezlenen devreler zamanlama ve alan açısından farklılık gösterir. Genel olarak, sentez tamamlandıktan sonra simülasyon doğrulamasının tekrar yapılması gerekir (buna post-simülasyon da denir; önceki aşama ise pre-simülasyon olarak adlandırılır).

(Mantık sentez aracı: Synopsys'in Design Compiler'ı)

STA

STA, yani statik zamanlama analizi, doğrulama kategorisine giren bir yöntemdir; temel olarak devreyi zamanlama açısından doğrular ve devrede kurulum süresi ile bekleme süresi ihlalleri olup olmadığını kontrol eder. Bu, dijital devrelerin temel bilgisi niteliğindedir. Bir kayıtçıda bu iki zamanlama ihlali meydana geldiğinde, verilerin doğru bir şekilde okunması ve çıkarılması mümkün olmaz; dolayısıyla kayıtçılara dayalı dijital yongaların işlevselliğinde mutlaka sorunlar ortaya çıkar.

(STA aracı: Synopsys'in Prime Time.)

Biçimsel doğrulama

Bu aynı zamanda, işlevsel doğrulama (STA ise zamanlama) kapsamında sentezlenmiş ağ listesini doğrulamaya yönelik bir doğrulama kategorisidir. En yaygın olarak kullanılan yöntem, eşdeğerlik kontrolü yöntemidir. İşlevsel doğrulama aşamasından geçen HDL tasarımını referans alarak, sentez sonrası ağ listesinin işlevlerini karşılaştırarak işlevsel olarak eşdeğer olup olmadıklarını kontrol eder. Bu işlem, orijinal HDL ile tanımlanan devre işlevinin mantık sentezi sürecinde değişmediğinden emin olmak amacıyla yapılır.

(Resmi doğrulama aracı: Synopsys Formality.)

Arka uç tasarımı

Entegre devrelerin arka uç tasarımı, devrenin fiziksel düzeninin oluşturulduğu tasarım sürecinin aşamasıdır. Bu aşama, metal maskelerin tasarlanmasını, metal katmanların yönlendirilmesini ve devrenin diğer fiziksel unsurlarını içerir. Arka uç tasarımı genellikle tasarım sürecinin en uzun ve en ayrıntılı kısmıdır ve devrenin doğru şekilde çalışmasını sağlamak açısından hayati öneme sahiptir. Bu süreç, optimize edilmiş bağlantı için Yeniden Dağıtım Katmanları (RDL) kullanımı gibi gelişmiş teknikleri de içerebilir.

Yönlendirilmiş Kuvvet Aktarımı

Test için Tasarım (DFT), test edilebilirlik için tasarım. Yonga devrelerinde genellikle yerleşik test devreleri bulunur ve DFT'nin amacı, tasarım aşamasında gelecekteki testleri göz önünde bulundurmaktır. DFT'ye yönelik yaygın bir yaklaşım, tarama zincirlerini tasarıma ekleyerek tarama yapamayan birimleri (kayıtlar gibi) tarama yapabilen birimlere dönüştürmektir. DFT konusunda bazı kitaplarda ayrıntılı açıklamalar bulunmakta olduğundan, konuyu resimlerle karşılaştırarak anlamak daha kolaydır.

(DFT aracı: Synopsys'in DFT Compiler'ı)

Kat planı

Yerleşim planı, yonganın makro hücre modülünün yerleştirilmesini ve genel olarak IP modülleri, RAM, G/Ç pinleri vb. gibi çeşitli işlevsel devrelerin yerleşimini belirlemeyi içerir. Yerleşim planı, yonganın nihai alanını doğrudan etkileyebilir.

(Kat planı araçları: Synopsys'in Astro'su)

CTS

Saat Ağacı Sentezi, kısaca saat ağacının kablolamasıdır. Dijital yongada saat sinyalinin genel kontrol işlevi nedeniyle, dağıtımı her kayıt birimine simetrik olarak bağlanmalıdır; böylece saat, aynı saat kaynağından her kayda ulaştığında saat gecikmesi farkı en aza indirilir. Saat sinyallerinin ayrı ayrı yönlendirilmesi gereken neden de budur.

(CTS aracı: Synopsys'in Fiziksel Derleyicisi.)

Düzen ve Güzergâh

Buradaki yol, çeşitli standart birimler (temel mantık kapısı devreleri) arasındaki kablolama da dahil olmak üzere, sıradan sinyal kablolamasıdır. Örneğin, sıkça duyduğumuz 0,13 mikronluk süreç ya da 90 nm'lik süreç, aslında burada metal kabloların ulaşabileceği minimum genişliktir ve mikroskobik açıdan bakıldığında MOS transistörünün kanal uzunluğuna karşılık gelir.

(Yönlendirme aracı: Synopsys'in Astro'su)

Parazitlerin çıkarılması

IC tasarımında parazitik ekstraksiyon, entegre devrelerin geliştirilmesinde önemli bir süreçtir. Bu süreç, devrenin fiziksel düzeninden kapasitans, endüktans ve direnç gibi parazitik unsurları ayıklamayı içerir. Bu süreç, IC tasarımının kullanıcının istediği performans gereksinimlerini karşıladığından emin olmak açısından hayati öneme sahiptir. Parazitik ekstraksiyonun doğruluğu da tasarımın beklendiği gibi çalışmasını sağlamada kilit bir rol oynar. Genel olarak, IC tasarımının parazitik ekstraksiyonu, bir entegre devreden iyi bir çalışma performansı elde etmek için çok önemli bir adımdır.

(Parazitik çıkarma aracı: Synopsys Star-RCXT)

Fiziksel Doğrulama

Entegre devre yerleşim tasarımının fiziksel doğrulaması, IC tasarım sürecinde hayati öneme sahip bir adımdır. Bu aşama, şematik tasarımın ardından gerçekleştirilir ve genellikle LVS (Yerleşim-Şematik Karşılaştırması) doğrulaması, DRC (Tasarım Kuralı Denetleyicisi) ve ERC (Elektriksel Kural Denetleyicisi) kullanımını içerir. LVS doğrulaması, fiziksel düzenin şematik tasarımla eşleştiğini doğrular. DRC, üretim süreci tarafından belirlenen tasarım kurallarının ihlallerini kontrol ederken, ERC ise elektriksel hataları kontrol eder. Tüm bu kontroller, tasarımın doğru ve üretime hazır olduğundan emin olmak için önemlidir. Fiziksel doğrulama, IC tasarımının istenen özellikleri ve gereksinimleri karşıladığından emin olunmasına yardımcı olur.

(Fiziksel doğrulama aracı: Synopsys'in Hercules ürünü)

Fiziksel düzen doğrulamasının tamamlanması, çip tasarım aşamasının tamamlandığı anlamına gelir; bundan sonra çip üretimi gelir.

IC Tasarımı İpuçları ve Püf Noktaları

– Proje gereksinimlerini ayrıntılı olarak

anlayın.- Tasarımı bloklara ayırın ve görevleri

dağıtın.- Güç gereksinimlerini analiz edin ve doğru bileşenleri

seçin.- Tasarım kurallarını göz önünde bulundurarak

devreyi özenle tasarlayın.- Simülasyonlarla tasarımı

doğrulayın.- Tasarımda hata ayıklama yapın ve yerleşim optimizasyonu

gerçekleştirin.- GDS dosyası oluşturun ve tasarımı hedef kartta doğrulayın.

– Güç tahmin ve optimizasyon tekniklerini

kullanın.- Doğru bileşenleri

seçin.- Zamanlama ve güç kısıtlamalarını göz önünde

bulundurun.- Tasarım otomasyon araçlarından yararlanın.- Doğrulama ve tasarım

hata ayıklaması

yapın.- Gelişmiş IC tasarım araçlarından

yararlanın.- Karmaşık tasarımlar için hiyerarşik

tasarım kullanın.- Güç, alan ve performans arasındaki dengeleri göz önünde

bulundurun.- Test edilebilirlik ve hata ayıklanabilirlik için tasarım

yapın.- Kapsamlı bir tasarım dokümantasyonu oluşturun.