SWD e JTAG são interfaces de depuração populares para MCUs baseadas em Cortex-M. Mas essas duas interfaces são diferentes tanto em estrutura quanto em aplicações. Neste artigo, apresentaremos seus pinos, princípio de funcionamento, prós e contras.

Interface SWD

SWD, Serial Wire Debug, é um protocolo projetado pela ARM para programação e depuração de seus microcontroladores. Ele se baseia na arquitetura de depuração ARM CoreSight e permite a leitura e gravação de registros de chip por meio de pacotes de dados. O SWD é um protocolo de dois fios para acessar interfaces de depuração ARM. Faz parte da Especificação da Arquitetura de Interface de Depuração ARM e serve como alternativa ao JTAG. Em casos em que o layout da placa de circuito impresso é limitado e os recursos de pinos são restritos, o SWD é uma boa escolha. Muitos depuradores no mercado suportam interfaces de depuração SWD, como ST-Link, J-Link, e-Link, GD-Link e outros.

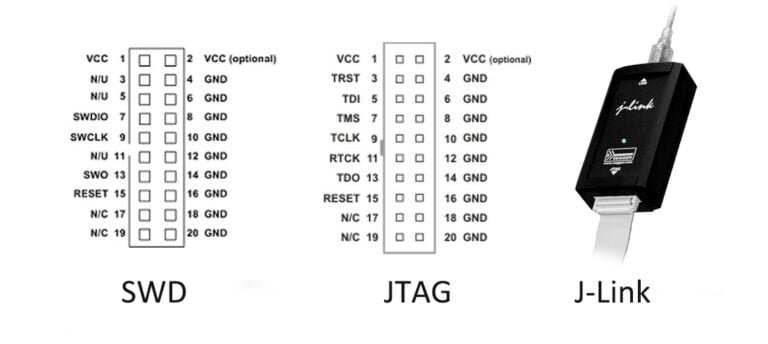

Pinos SWD

SWDIO: Entrada/saída de dados em fio serial, pino de entrada e saída

de dados em série SWCLK: Relógio em fio serial, pino do relógio da linha serial

Para SWDIO, é um pino de dados bidirecional (entrada e saída), e a linha deve ser puxada para cima na placa de circuito (a ARM recomenda 100 K).

Como funciona o SWD?

Dispositivos externos, como sondas de depuração, conectam-se ao SWDIO/SWCLK para acessar diretamente a porta de depuração serial (SW-DP). A SW-DP pode acessar uma ou várias portas de acesso (APs) e, por meio das APs, é possível acessar os demais registros do sistema. Uma AP importante para CPUs da série Cortex M é a AHB-AP, que atua como mestre no barramento AHB interno. Em outras palavras, a AHB-AP pode acessar o mapa de memória do núcleo interno. Como o flash interno, a SRAM, os componentes de depuração e os dispositivos periféricos são todos mapeados na memória, a AHB-AP pode controlar todo o dispositivo, incluindo sua programação. Todo o processo de operação SWD é hierárquico, com sinais de clock de entrada do pino SWCLK e sinais de dados de entrada/saída do pino SWDIO. Inicialmente, o depurador opera no SW-DP para determinar os parâmetros dos registros AP, permitindo a manipulação do mapa de memória Cortex.

Vantagens do SWD

- Contagem de sinais reduzida

- Confiabilidade em altas velocidades

- Probabilidade reduzida de falhas

- Compatibilidade com simulações JTAG

- Requer menos pinos para operação

Interface JTAG

O JTAG, Joint Test Action Group, era originalmente usado para testar chips. Esse grupo iniciou discussões no final da década de 1980 e lançou formalmente documentos interpretando os padrões IEEE em 1990. (IEEE significa Institute of Electrical and Electronics Engineers, uma organização internacional responsável pela publicação de padrões como WiFi e Bluetooth.) O protocolo proposto por eles foi documentado na norma IEEE 1149.1 em 1990. Desde então, esse documento passou por revisões e melhorias, sendo a norma mais recente, até o momento da redação deste artigo, a IEEE 1149.7.

Pinos JTAG

- TDI: Entrada de dados de teste, um pino de entrada serial.

- TDO: Saída de dados de teste, um pino de saída serial.

- TCK: Relógio de teste, um pino de relógio.

- TMS: Seleção do modo de teste, um pino de seleção de modo (sinal de controle).

- TRST: Reinicialização de teste, um pino de reinicialização.

Como funciona o JTAG?

O princípio do JTAG envolve a definição de uma Porta de Acesso de Teste (TAP) dentro do dispositivo. Isso permite o teste de nós internos usando ferramentas de teste JTAG especializadas. O teste JTAG permite que vários dispositivos sejam conectados em série por meio de uma interface JTAG, formando uma cadeia JTAG para o teste individual de dispositivos. Atualmente, as interfaces JTAG também são comumente usadas para operações programáveis no sistema (ISP), como a programação de dispositivos FLASH. Em termos de estrutura de hardware, a interface JTAG consiste em duas partes: a porta JTAG e o controlador. Os dispositivos compatíveis com a interface JTAG podem ser microprocessadores (MPUs), microcontroladores (MCUs), PLDs, CPLDs, FPGAs, DSPs, ASICs ou outros chips compatíveis com as especificações IEEE 1149.1. A norma IEEE 1149.1 exige a presença de uma unidade de registro de deslocamento chamada Unidade de Varredura de Limite (BSU) para cada pino de um chip de circuito integrado digital. Ela conecta o circuito JTAG ao circuito lógico central, isolando o circuito lógico central dos pinos do chip. Todas as Unidades de Varredura de Limite do chip constituem o Registro de Varredura de Limite (BSR). O circuito do Registro de Varredura de Limite fica ativo apenas durante o teste JTAG e não afeta a funcionalidade do chip durante a operação normal.

O protocolo JTAG controla a transição da máquina de estado TAP através do sinal TMS. Após a inicialização do sistema, o controlador TAP entra primeiro no estado Test-Logic Reset (Redefinição da lógica de teste) e, em seguida, passa sequencialmente pelos estados Run-Test/Idle (Executar teste/Inativo), Select-DR-Scan (Selecionar varredura DR), Select-IR-Scan (Selecionar varredura IR), Capture-IR (Capturar IR), Shift-IR (Deslocar IR), Exit1-IR (Sair 1-IR) e Update-IR (Atualizar IR) antes de retornar ao estado Run-Test/Idle (Executar teste/Inativo). Durante esse processo, as transições de estado são acionadas pelo sinal TCK (borda ascendente), com os sinais TMS usados para selecionar o estado TAP. No estado Capture-IR, uma sequência lógica específica é carregada no registro de instruções; no estado Shift-IR, uma instrução específica pode ser transferida para o registro de instruções; e no estado Update-IR, a instrução recém-inserida no registro de instruções é usada para atualizar o registro de instruções. Finalmente, o sistema retorna ao estado Run-Test/Idle, onde a instrução entra em vigor, completando o acesso à instrução e aos registros. Após retornar ao estado Run-Test/Idle, com base no conteúdo do registro de instruções, o registro de dados necessário é selecionado e o trabalho nos registros de dados é iniciado.

Vantagens do JTAG

- O JTAG não se limita aos chips ARM; ele é compatível com chips além do ARM, como o conhecido MSP430.

- O JTAG tem uma ampla gama de aplicações para programação, depuração e testes de produção.

- O JTAG é um grupo independente que evolui com o desenvolvimento do protocolo.

Conclusão

JTAG e SWD são duas interfaces importantes para a depuração de sistemas embarcados, cada uma com seus pontos fortes e fracos. A escolha da interface depende dos requisitos do projeto, do suporte de hardware e das necessidades de desempenho. Para sistemas complexos, o JTAG pode ser necessário para obter mais controle e funcionalidade, enquanto o SWD pode ser mais adequado para sistemas com recursos limitados. Considerar esses fatores coletivamente pode ajudá-lo a tomar decisões informadas para um desenvolvimento e depuração mais eficazes de sistemas embarcados.