Análise de falhas de circuitos integrados

Recurso técnico abrangente sobre metodologias, ferramentas e estudos de caso para análise de falhas em semicondutores.

O que é Análise de Falhas em Circuitos Integrados?

A Análise de Falhas em Circuitos Integrados (CI) é um processo sistemático utilizado para identificar, isolar e determinar a causa raiz de falhas em dispositivos semicondutores. Essa disciplina crítica da engenharia combina técnicas avançadas de imagem, testes elétricos e ciência dos materiais para solucionar problemas em circuitos integrados em diversos setores industriais.

Uma análise de falhas eficaz melhora a confiabilidade do produto, reduz os custos de fabricação, acelera o tempo de lançamento no mercado e garante a conformidade com os padrões da indústria. Ela desempenha um papel vital no controle de qualidade, na engenharia de confiabilidade e nos ciclos de melhoria de produtos.

Objetivos principais da análise de falhas de circuitos integrados

- Identificar as causas principais das falhas dos circuitos integrados por meio de investigação sistemática.

- Determine se as falhas têm origem no projeto, na fabricação ou na aplicação.

- Desenvolver ações corretivas para evitar falhas futuras.

- Validar a confiabilidade e o desempenho de circuitos integrados.

- Apoiar a elaboração de relatórios de falhas e a análise de dados de confiabilidade.

Guias e metodologias técnicas

Fluxograma de diagnóstico

Abordagem sistemática desde a identificação do sintoma da falha até a identificação da causa raiz.

Sem caminho para falha de energia/saída

- 1. Verificar danos por descarga eletrostática (ESD) usando análise SEM/EDS.

- 2. Verificar juntas de solda com inspeção por raios X 3D.

- 3. Teste de ruptura do óxido de porta usando EMMI

- 4. Realize testes de continuidade com OBIRCH

- 5. Analise a integridade da embalagem com C-SAM

Caminho de falha de falhas intermitentes

- 1. Excluir microfissuras em BGA usando C-SAM

- 2. Verifique o estresse térmico com imagens infravermelhas.

- 3. Teste de latch-up relacionado ao projeto por meio de simulação de circuito.

- 4. Verificar a integridade da rede de distribuição de energia

Guia de Operação EMMI

Fluxograma passo a passo para análise por Microscopia de Emissão

Preparação do dispositivo

Ligue o dispositivo no estado em que a falha ocorre e assegure-se de que ele esteja sendo resfriado adequadamente.

Configuração de câmara escura

Posicione o dispositivo sob o microscópio EMMI e assegure o alinhamento correto.

Configuração da câmera

Defina o tempo de exposição apropriado (normalmente de 10 a 60 segundos) e a sensibilidade.

Aquisição de Imagens

Capture várias imagens com tempos de exposição variados para obter resultados ideais.

Análise e sobreposição

Sobreponha os pontos de emissão ao layout do projeto para identificar estruturas com falhas.

Dica de solução de problemas

Caso não apareçam pontos quentes, verifique se o chip está em um estado que reproduz a falha e verifique se o mecanismo de falha produz emissões de fótons (circuitos abertos normalmente não produzem).

Armadilhas comuns na análise de falhas

Ignorar danos causados por descarga eletrostática

Não levar em consideração os danos por descarga eletrostática durante o manuseio, especialmente em chips CMOS. Sempre verifique a funcionalidade da pulseira antiestática e os protocolos de aterramento.

Redução de potência inadequada

Queima do resistor devido à operação com carga de potência acima de 80%. A prática recomendada é reduzir a potência nominal em 50% para garantir a confiabilidade em condições variáveis.

Reprodução incorreta de falha

Analisar dispositivos em condições que não reproduzem com precisão o cenário de falha em campo, levando à identificação incorreta da causa raiz.

Ignorando problemas de embalagem

Focando exclusivamente em problemas no nível do chip, enquanto se ignoram falhas relacionadas à embalagem, como delaminação, corrosão dos terminais ou fadiga das juntas de solda.

Documentação insuficiente

A falta de documentação completa de cada etapa da análise dificulta a replicação dos resultados ou a realização de análises de tendências em múltiplas falhas.

Problemas de calibração de ferramentas

O uso de equipamentos calibrados incorretamente leva a medições imprecisas e conclusões incorretas na análise de falhas.

Estudos de Caso da Indústria

Falha do módulo IGBT em veículos elétricos

Sintoma

Perda repentina de energia durante o carregamento, sem danos externos visíveis ao sistema de propulsão do veículo elétrico.

Processo de análise

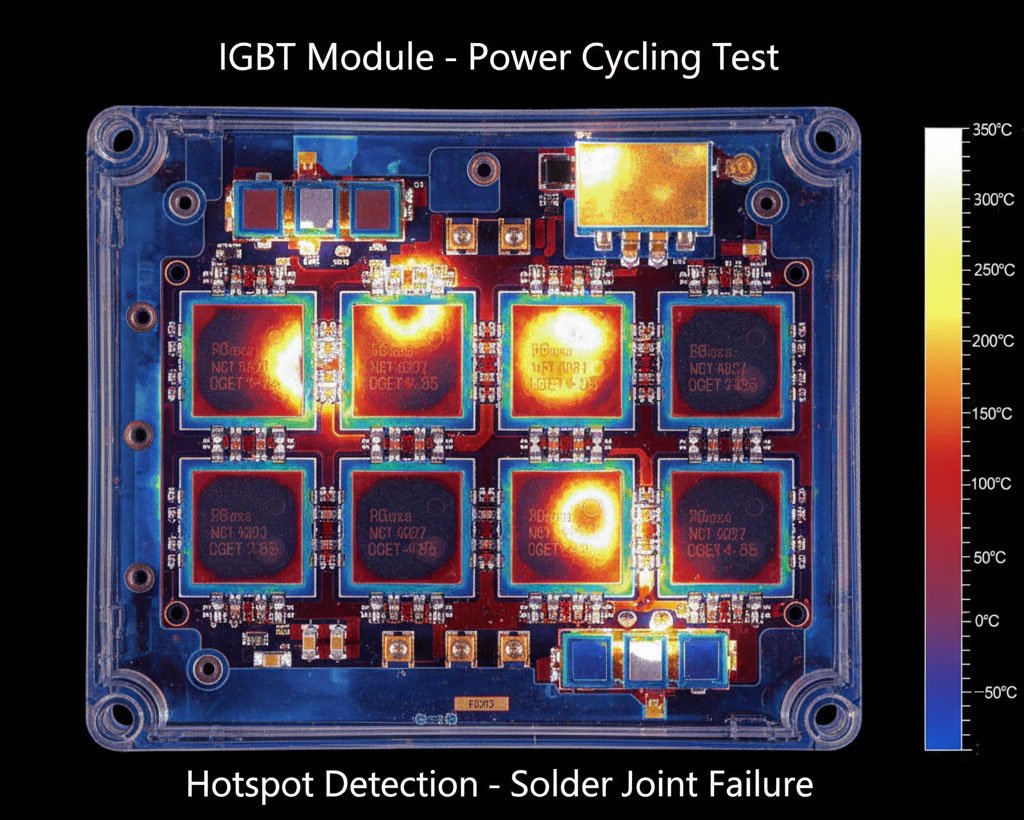

- A termografia revelou pontos quentes no módulo IGBT durante o ciclo de energia.

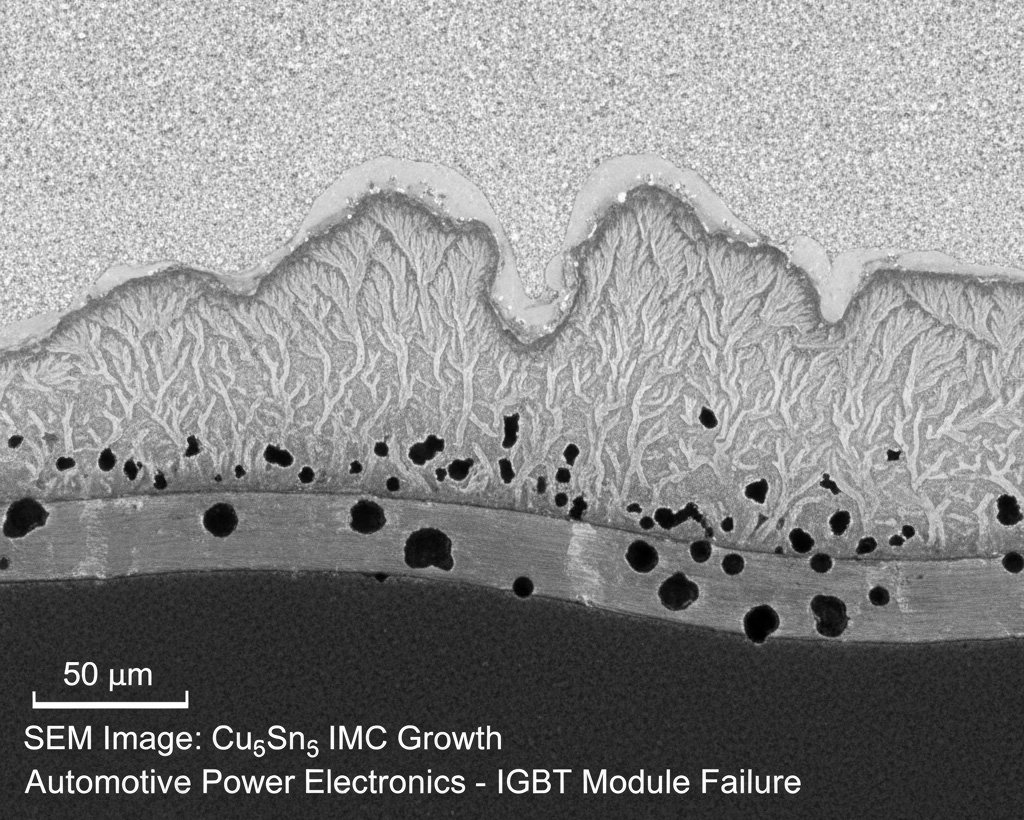

- A análise SEM/EDS identificou crescimento excessivo de IMC (Cu₆Sn₅) nas juntas de solda.

- A análise por secção transversal revelou a formação de vazios de Kirkendall na interface solda-substrato.

- A simulação por elementos finitos (FEA) associou a falha a um perfil de refluxo de solda insuficiente.

Solução e Resultado

Perfil de refluxo ajustado para garantir a molhagem adequada e adição de pads niquelados para controlar o crescimento da camada intermetálica.

Resultado: A taxa de falhas em campo foi reduzida em 0,58% ao ano, gerando uma economia de US$ 2 milhões em custos de garantia.

Normas relevantes

Resultados de imagens térmicas

Imagem SEM do crescimento de IMC

Falha do amplificador GaAs em AAUs 5G

Sintoma

Falhas em campo nas Unidades de Antena Ativa (AAUs) 5G nos primeiros 6 meses de implantação, resultando em degradação do sinal.

Processo de análise

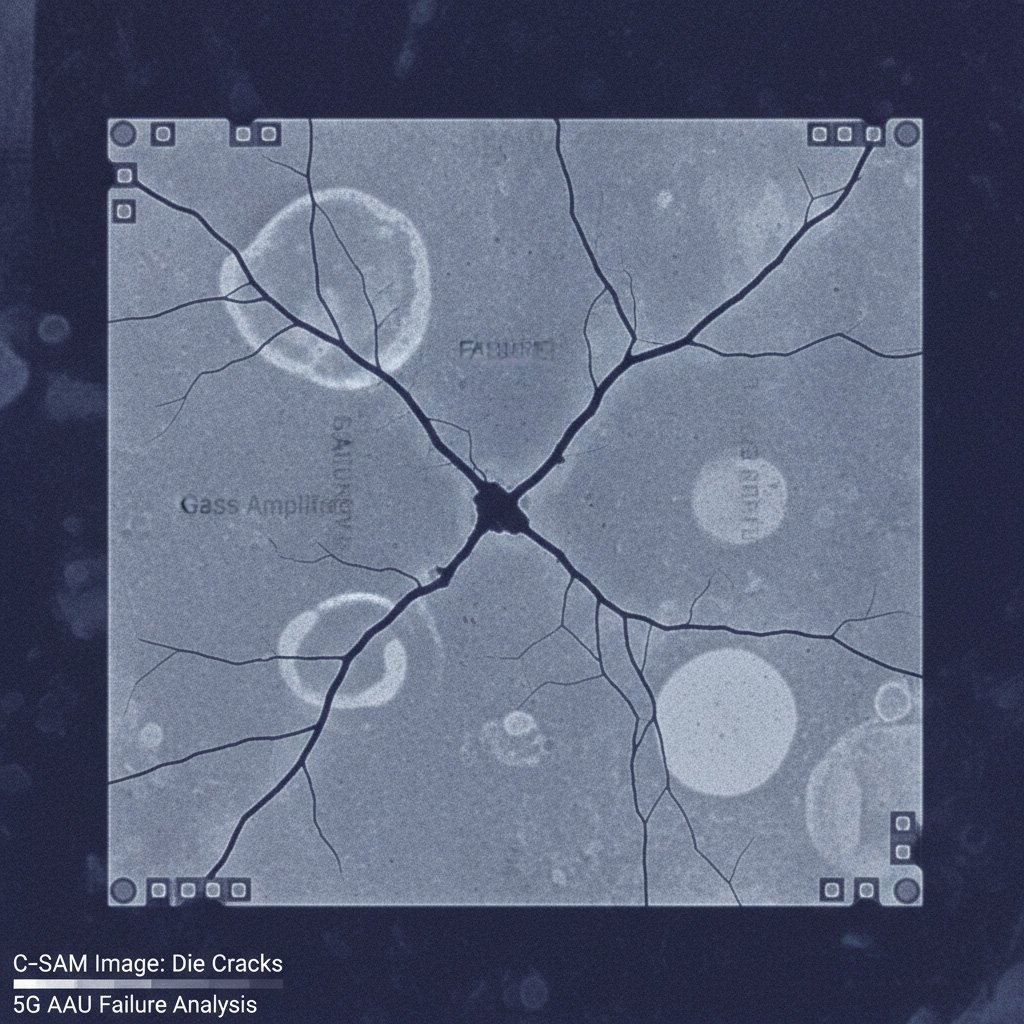

- A inspeção C-SAM detectou rachaduras nos chips dos amplificadores de potência de GaAs.

- Uma auditoria de embalagem detectou marcas anormais de ejeção na parte traseira do molde.

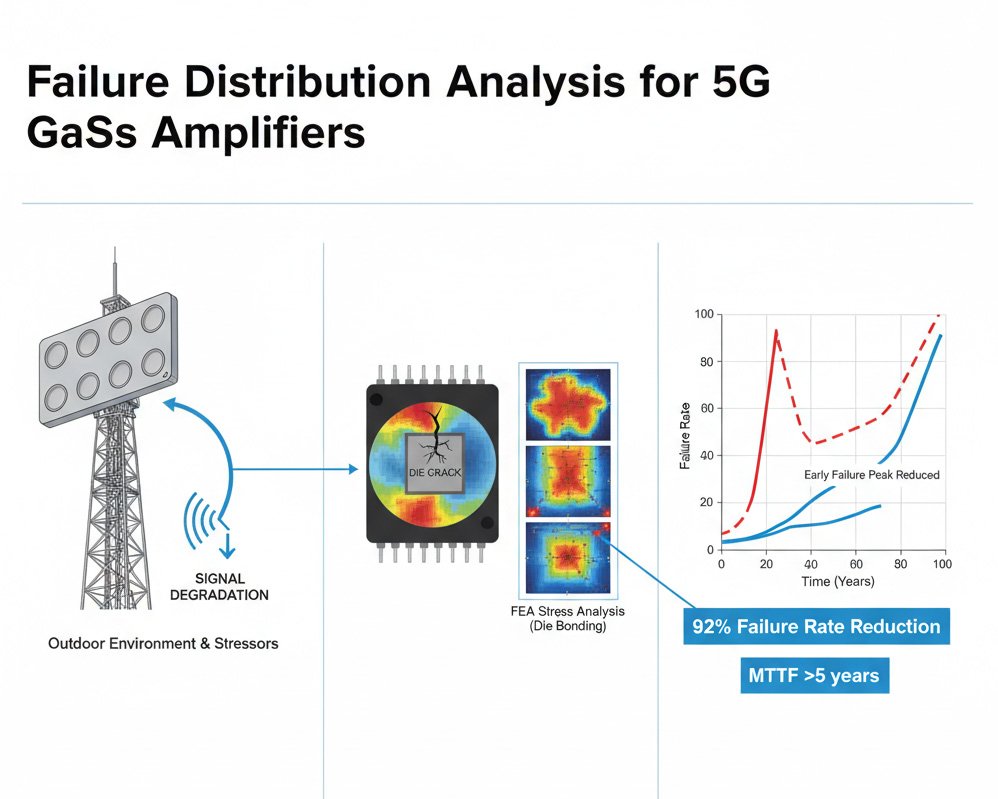

- A análise dos dados de confiabilidade mostrou que a distribuição de falhas se encaixa no modo de falha precoce.

- A análise de elementos finitos confirmou a tensão mecânica durante a colagem do chip.

Solução e Resultado

Modificação da película azul de colagem do chip para reduzir o estresse mecânico e implementação de inspeção pós-colagem em 100% dos casos utilizando inspeção óptica automatizada.

Resultado: A taxa de falhas foi reduzida em 92%, aumentando o tempo médio entre falhas para mais de 5 anos.

Normas relevantes

Imagem C-SAM de trincas na matriz

Análise de Distribuição de Falhas

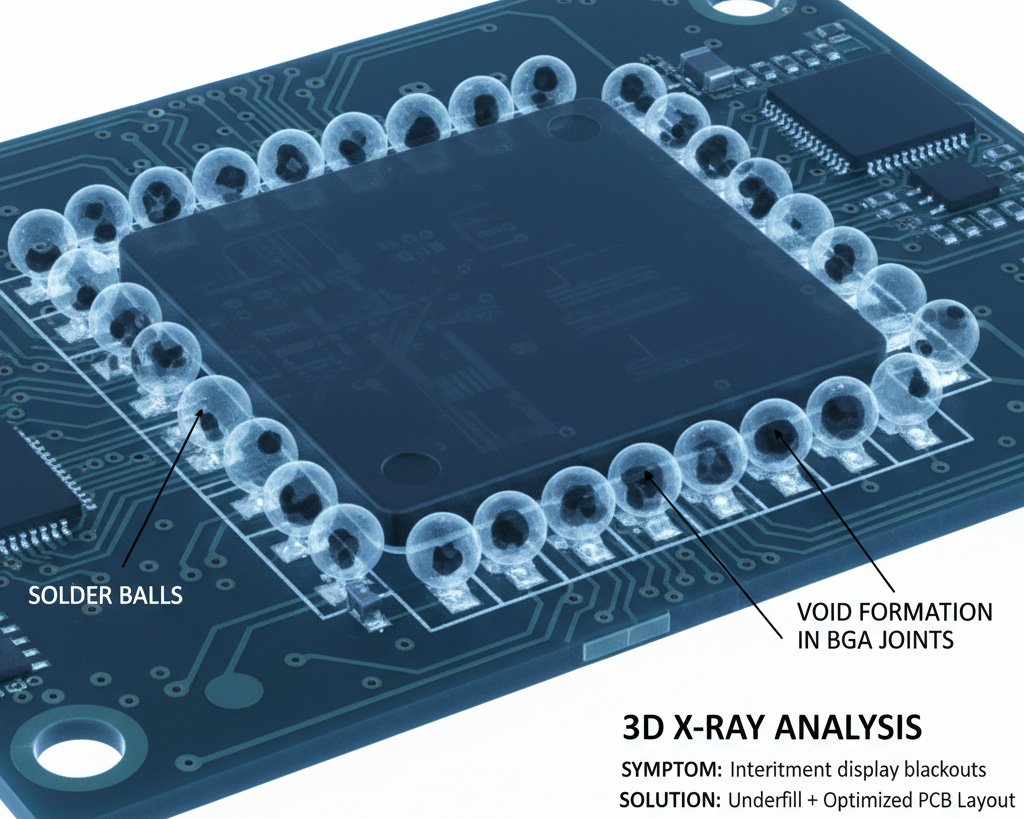

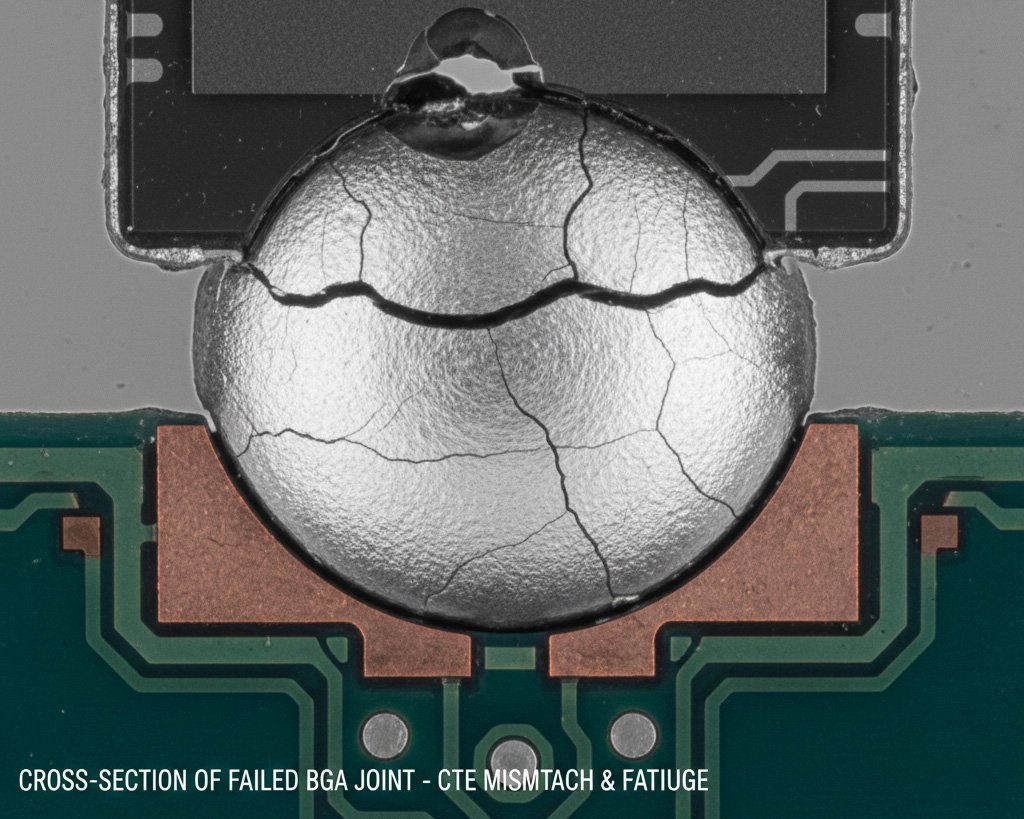

Falha de BGA em smartphones

Sintoma

Apagões intermitentes na tela e tela sensível ao toque que não responde em smartphones de última geração após 6 a 8 meses de uso.

Processo de análise

- O ciclo térmico (de -40 °C a 85 °C) reproduziu a falha observada em condições de laboratório.

- A microscopia acústica de varredura (SAM) revelou fadiga na junta de solda.

- A análise da secção transversal confirmou a incompatibilidade do CTE (Coeficiente de Expansão Térmica).

- A análise tridimensional por raios X quantificou a formação de vazios em 18% das juntas BGA.

Solução e Resultado

Implementamos um material de preenchimento com Tg (Temperatura de Transição Vítrea) mais alta e otimizamos o layout da placa de circuito impresso para reduzir os gradientes térmicos.

Resultado: Redução de 76% nas devoluções em campo, sem relatos de falhas após 18 meses de uso.

Normas relevantes

Radiografia 3D de vazios BGA

Secção transversal de uma junta danificada

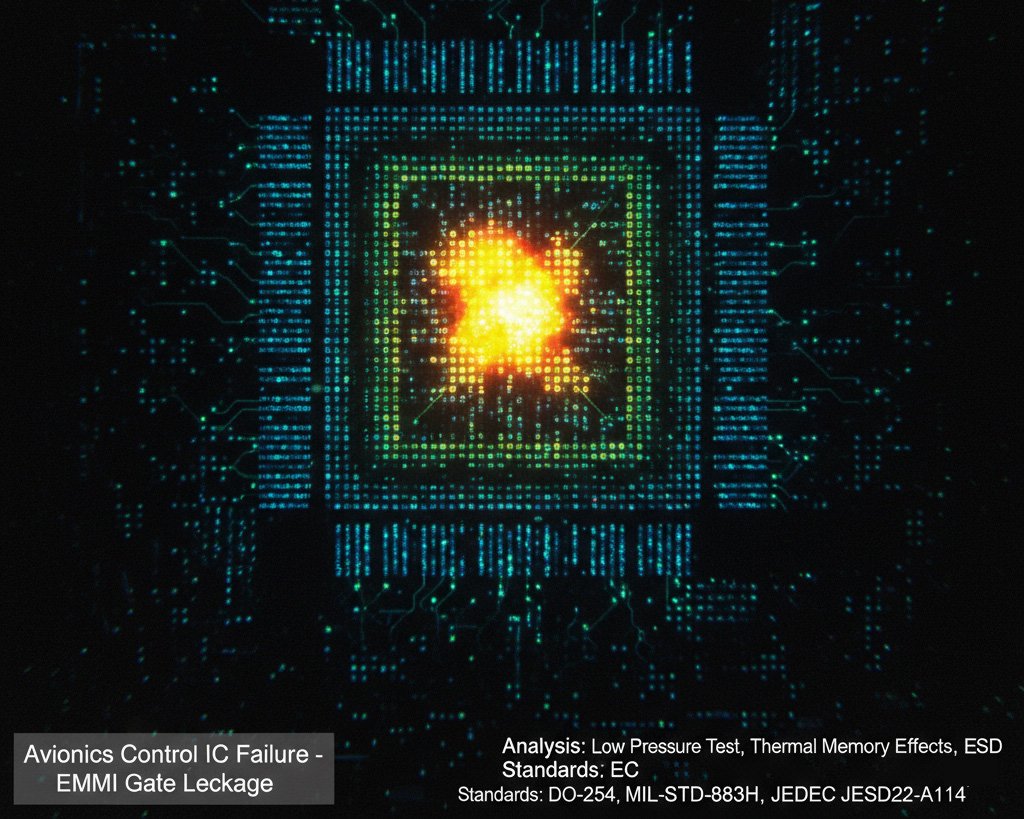

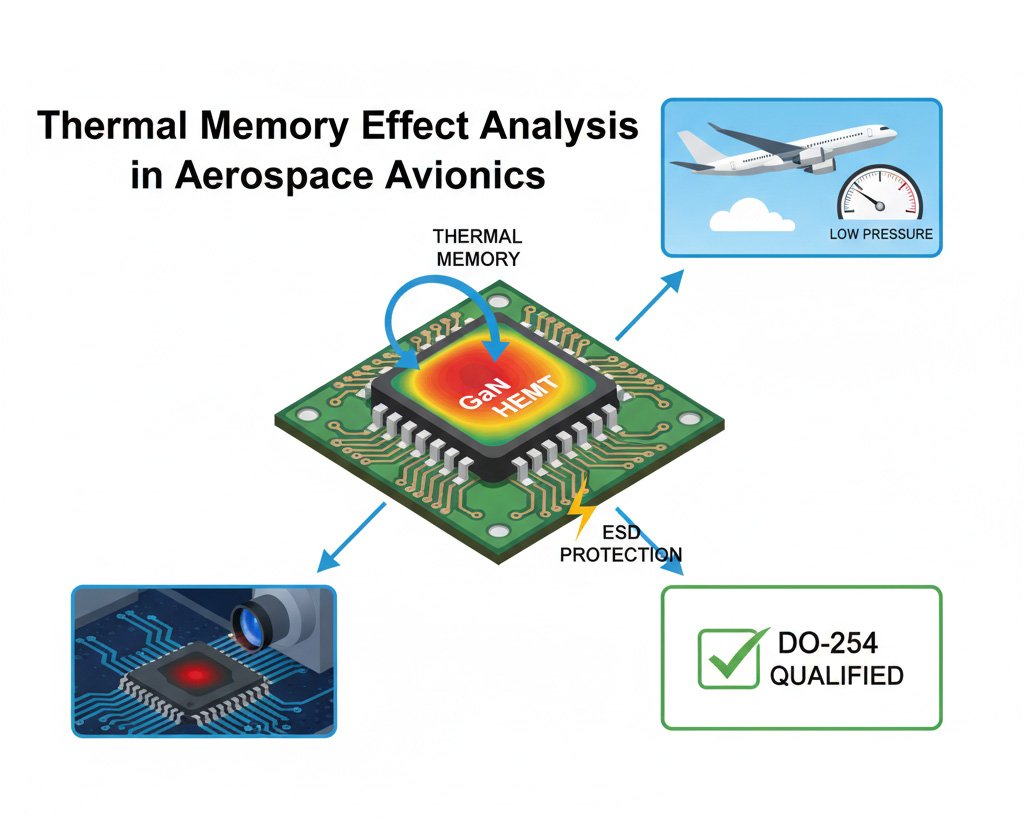

Falha no CI de controle de aviônica

Sintoma

Reinicializações aleatórias do sistema nos módulos de controle da aviônica durante voos em grandes altitudes, sem um padrão claro.

Processo de análise

- Os testes ambientais reproduziram a falha em condições de baixa pressão (alta altitude).

- A EMMI detectou vazamento intermitente no gate do circuito integrado de gerenciamento de energia.

- A modelagem IC-CAP identificou efeitos de memória térmica não modelados em HEMTs de GaN.

- Os testes de ESD revelaram proteção insuficiente nos circuitos de entrada.

Solução e Resultado

Modelo ASM-HEMT atualizado para incluir efeitos de memória térmica e circuitos de proteção ESD aprimorados.

Resultado: Eliminação completa das reinicializações em voo, com qualificação bem-sucedida segundo as normas DO-254.

Normas relevantes

Imagem EMMI de vazamento de porta

Análise do Efeito de Memória Térmica

Ferramentas e equipamentos

| Ferramenta | Caso de uso principal | Limite de resolução | Ideal para | Limitação |

|---|---|---|---|---|

| EMMI | Localização de pontos críticos (vazamentos, falhas) | ~1μm | CMOS/FinFETs | Sem sinal para circuitos abertos |

| C-SAM | Detecção de delaminação/vazios | 50nm | Flip-chip, BGA | Requer acoplamento líquido |

| Tomografia computadorizada de raios X 3D | Inspeção de matrizes TSV/empilhadas | 100nm | CIs 3D | Alto custo para alta resolução |

| Termografia de bloqueio | Mapeamento térmico sub-°C | 0,1°C | Circuitos integrados de potência (IGBTs) | Tempo de digitalização lento |

| SEM/EDS | Caracterização de materiais, imagem de defeitos | 1-5nm | Análise física ao nível do chip | Requer revestimento condutor para isoladores. |

| FIB-SEM | Seccionamento transversal, edição de circuitos | 5nm | Circuitos integrados 3D, embalagens avançadas | Destrutivo, demorado |

Guia de Combinação de Ferramentas e Técnicas

A utilização das ferramentas adequadas a cenários de falha específicos garante uma análise de causa raiz eficiente e precisa:

Análise de danos por descarga eletrostática

- Comece com o EMMI para localizar pontos de vazamento.

- Em seguida, utilize FIB-SEM para obter imagens em nanoescala dos danos.

- Utilize EDS para verificar a presença de contaminação nos locais de falha.

- Verificar com testes elétricos (análise da curva IV)

Rachaduras TSV em CI 3D

- Utilize a tomografia computadorizada de raios X 3D para inspeção não destrutiva.

- Validar com seccionamento transversal por FIB em locais críticos.

- Realizar imagens de MEV (Microscopia Eletrônica de Varredura) para caracterizar a morfologia da trinca.

- Aplicar a análise de elementos finitos para determinar as origens das tensões.

Falhas relacionadas à temperatura

- Comece com a termografia lock-in para mapeamento térmico.

- Utilize o C-SAM para verificar a delaminação devido ao estresse térmico.

- Realizar cortes transversais para examinar a integridade da junta de solda.

- Validar com testes de ciclagem térmica

Falhas intermitentes

- Utilize uma câmara ambiental para reproduzir as condições de falha.

- Aplique o OBIRCH para análise dinâmica do caminho da corrente.

- Utilize imagens térmicas durante testes de estresse.

- Verifique com testes de vibração se houver suspeita de tensão mecânica.

Ferramentas e tecnologias emergentes

EMMI aprimorado por IA

Algoritmos de aprendizado de máquina que distinguem automaticamente padrões de emissão de fótons normais de anormais, reduzindo o tempo de análise em até 70%.

Rotulagem de pontos quânticos

Marcadores fluorescentes em nanoescala que destacam regiões com defeitos em semicondutores, permitindo a detecção precoce de potenciais pontos de falha.

Plataformas de Análise Preditiva

Sistemas integrados que combinam dados de fabricação, relatórios de falhas em campo e IA para prever possíveis mecanismos de falha antes que eles ocorram.

Normas e Conformidade

Padrões JEDEC

JESD22-A121: Teste ESD

Define os procedimentos para testes de descarga eletrostática em modelos de corpo humano (HBM), modelos de máquinas (MM) e modelos de dispositivos carregados (CDM).

JESD47: Métodos de teste de estresse para circuitos integrados

Norma abrangente que engloba diversos testes de estresse, incluindo ciclos térmicos, tensão-temperatura, eletromigração e ruptura dielétrica dependente do tempo.

JESD22-A104: Ciclos de temperatura

Norma específica para testes de ciclagem térmica para avaliar a confiabilidade de componentes sob condições de estresse térmico.

Normas específicas da indústria

AEC-Q100: Circuitos Integrados Automotivos

Especificação de qualificação para circuitos integrados utilizados em aplicações automotivas, com requisitos de confiabilidade rigorosos.

DO-254: Aviônica Aeroespacial

Diretrizes de garantia de projeto para hardware eletrônico embarcado, incluindo circuitos integrados usados em sistemas críticos de voo.

Telcordia GR-468: Telecomunicações

Requisitos para garantir a confiabilidade de dispositivos semicondutores usados em equipamentos de telecomunicações.

Análise de dados de confiabilidade

Uma análise de falhas eficaz requer a análise estatística de dados de confiabilidade para compreender a distribuição das falhas e prever a vida útil do produto:

Distribuições de falhas

- Distribuição log-normal: comum em falhas de semicondutores.

- Distribuição de Weibull: Útil para analisar falhas precoces, aleatórias e por desgaste.

- Distribuição exponencial: Adequada para regiões com taxa de falha constante.

Métricas principais

- MTBF (Tempo Médio Entre Falhas)

- Taxa de falhas (λ) - normalmente expressa em FITs (Falhas no Tempo: 1 FIT = 1 falha por 10^9 horas de funcionamento do dispositivo)

- Fatores de conversão para Testes de Vida Acelerada (ALT)

Exemplo de análise da taxa de falhas

Tendências Futuras na Análise de Falhas de Circuitos Integrados

Nós de processo avançados (2nm/1nm)

Os desafios da análise em escala atômica, com os efeitos quânticos se tornando fatores significativos nos mecanismos de falha.

Principais desafios

- • Efeitos de tunelamento quântico

- • Defeitos no fornecimento de energia pela parte traseira

- • Detecção de contaminação em nível atômico

Soluções emergentes

- • Microscopia eletrônica de transmissão criogênica para inspeção em nível atômico

- • Técnicas de nanossondagem baseadas em IA

- • Tomografia avançada de sonda atômica

Circuitos Integrados 3D e Integração Heterogênea

Modos de falha complexos em arquiteturas de chips empilhados que exigem novas técnicas de análise não destrutivas.

Principais desafios

- • Rachaduras em TSV (Through-Silicon Via)

- • Delaminação de enchimento insuficiente em matrizes empilhadas

- • Problemas de gerenciamento térmico

Soluções emergentes

- • Tomografia computadorizada de raios X 3D avançada com resolução mais alta

- • Técnicas de imagem multimodal

- • Projeto para testabilidade em circuitos integrados 3D

IA e Aprendizado de Máquina

Detecção e classificação automatizadas de falhas para lidar com a crescente complexidade dos circuitos integrados.

Principais aplicações

- • Classificação automatizada de defeitos em imagens de MEV (Microscopia Eletrônica de Varredura).

- • Análise preditiva de falhas a partir de dados de fabricação

- • Detecção de anomalias em dados de teste de wafers

Benefícios

- • Redução de 50 a 70% no tempo de análise

- • Maior precisão na identificação da causa raiz

- • Previsão precoce de falhas antes da implantação em campo