SWD e JTAG sono interfacce di debug popolari per i microcontroller basati su Cortex-M. Ma queste due interfacce sono diverse sia nella struttura che nelle applicazioni. In questo articolo, introdurremo i loro pin, il principio di funzionamento, i pro e i contro.

Interfaccia SWD

SWD, Serial Wire Debug, è un protocollo progettato da ARM per la programmazione e il debug dei loro microcontrollori. Si basa sull’architettura di debug ARM CoreSight e consente la lettura e la scrittura dei registri del chip tramite pacchetti di dati. SWD è un protocollo a due fili per accedere alle interfacce di debug ARM. Fa parte delle specifiche dell’architettura dell’interfaccia di debug ARM e serve come alternativa a JTAG. Nei casi in cui il layout della PCB è limitato e le risorse dei pin sono vincolate, SWD è una buona scelta. Molti debugger sul mercato supportano le interfacce di debug SWD, come ST-Link, J-Link, e-Link, GD-Link e altri.

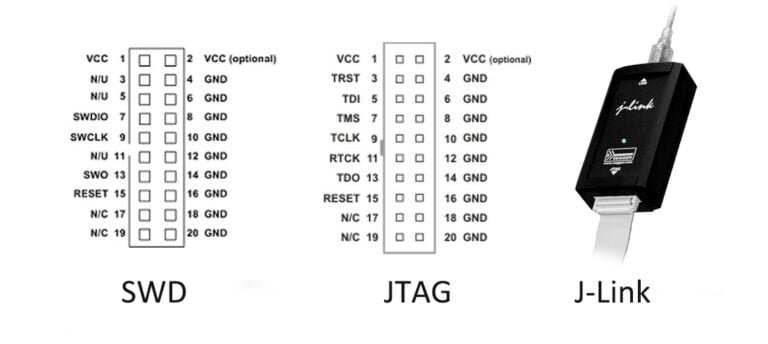

Pin SWD

SWDIO: Serial Wire Data Input Output, pin di ingresso e uscita dati seriali

SWCLK: Serial Wire Clock, pin di clock della linea seriale

Per SWDIO, è un pin dati bidirezionale (ingresso e uscita) e la linea deve essere tirata verso l’alto sulla scheda circuitale (ARM raccomanda 100 K).

Come funziona SWD?

I dispositivi esterni, come le sonde di debug, si connettono a SWDIO/SWCLK per accedere direttamente alla porta di debug Serial Wire (SW-DP). SW-DP può accedere a una o più porte di accesso (AP) e, tramite AP, è possibile accedere ai registri del resto del sistema. Un AP importante per le CPU della serie Cortex M è AHB-AP, che funge da master sul bus AHB interno. In altre parole, AHB-AP può accedere alla mappa di memoria del core interno. Poiché la flash interna, la SRAM, i componenti di debug e i dispositivi periferici sono tutti mappati in memoria, AHB-AP può controllare l’intero dispositivo, inclusa la sua programmazione. L’intero processo di funzionamento SWD è gerarchico, con segnali di clock in ingresso dal pin SWCLK e segnali dati in ingresso/uscita dal pin SWDIO. Inizialmente, il debugger opera su SW-DP per determinare i parametri dei registri AP, consentendo la manipolazione della mappa di memoria Cortex.

Vantaggi di SWD

- Conteggio dei segnali ridotto

- Affidabilità ad alta velocità

- Probabilità di guasti ridotta

- Compatibilità con le simulazioni JTAG

- Richiede meno pin per il funzionamento

Interfaccia JTAG

JTAG, Joint Test Action Group, era originariamente utilizzato per testare i chip. Questo gruppo ha avviato discussioni alla fine degli anni ’80 e ha rilasciato formalmente documenti che interpretano gli standard IEEE nel 1990. (IEEE sta per Institute of Electrical and Electronics Engineers, un’organizzazione internazionale responsabile della pubblicazione di standard come WiFi e Bluetooth.) Il protocollo che hanno proposto è stato documentato in IEEE 1149.1 nel 1990. Questo documento è stato successivamente rivisto e migliorato, con l’ultimo standard alla data di questa scrittura che è IEEE 1149.7.

Pin JTAG

- TDI: Test Data In, un pin di ingresso seriale.

- TDO: Test Data Out, un pin di uscita seriale.

- TCK: Test Clock, un pin di clock.

- TMS: Test Mode Select, un pin di selezione della modalità (segnale di controllo).

- TRST: Test Reset, un pin di reset.

Come funziona JTAG?

Il principio di JTAG prevede la definizione di una porta di accesso ai test (TAP) all’interno del dispositivo. Ciò consente di testare i nodi interni utilizzando strumenti di test JTAG specializzati. Il test JTAG consente di collegare più dispositivi in serie tramite un’interfaccia JTAG, formando una catena JTAG per il test dei singoli dispositivi. Oggi, le interfacce JTAG sono anche comunemente utilizzate per operazioni di programmazione In-System (ISP), come la programmazione di dispositivi FLASH. In termini di struttura hardware, l’interfaccia JTAG è composta da due parti: la porta JTAG e il controller. I dispositivi compatibili con l’interfaccia JTAG possono essere microprocessori (MPU), microcontrollori (MCU), PLD, CPLD, FPGA, DSP, ASIC o altri chip conformi alle specifiche IEEE 1149.1. IEEE 1149.1 impone la presenza di un’unità di registro a scorrimento chiamata Boundary Scan Unit (BSU) per ogni pin di un chip di circuito integrato digitale. Collega il circuito JTAG con il circuito logico principale isolando il circuito logico principale dai pin del chip. Tutte le unità Boundary Scan del chip costituiscono il Boundary Scan Register (BSR). Il circuito Boundary Scan Register è attivo solo durante il test JTAG e non influisce sulla funzionalità del chip durante il funzionamento normale.

Il protocollo JTAG controlla la transizione della macchina di stato TAP tramite il segnale TMS. Dopo l’accensione del sistema, il controller TAP entra prima nello stato Test-Logic Reset, quindi passa sequenzialmente attraverso Run-Test/Idle, Select-DR-Scan, Select-IR-Scan, Capture-IR, Shift-IR, Exit1-IR e Update-IR stati prima di tornare a Run-Test/Idle. Durante questo processo, le transizioni di stato sono guidate dal segnale TCK (fronte di salita), con i segnali TMS utilizzati per selezionare lo stato TAP. Nello stato Capture-IR, una specifica sequenza logica viene caricata nel registro delle istruzioni; nello stato Shift-IR, una specifica istruzione può essere spostata nel registro delle istruzioni; e nello stato Update-IR, l’istruzione appena inserita nel registro delle istruzioni viene utilizzata per aggiornare il registro delle istruzioni. Infine, il sistema torna allo stato Run-Test/Idle, dove l’istruzione ha effetto, completando l’accesso all’istruzione e ai registri. Dopo essere tornati allo stato Run-Test/Idle, in base al contenuto del registro delle istruzioni, viene selezionato il registro dati richiesto e si inizia a lavorare sui registri dati.

Vantaggi di JTAG

- JTAG non è limitato ai chip ARM; è supportato in chip oltre ARM, come il noto MSP430.

- JTAG ha un’ampia gamma di applicazioni per la programmazione, il debug e i test di produzione.

- JTAG è un gruppo indipendente che si evolve con lo sviluppo del protocollo.

Conclusione

JTAG e SWD sono entrambe importanti interfacce di debug dei sistemi embedded, ognuna con i propri punti di forza e di debolezza. La scelta dell’interfaccia dipende dai requisiti del progetto, dal supporto hardware e dalle esigenze di prestazioni. Per sistemi complessi, JTAG potrebbe essere necessario per ottenere più controllo e funzionalità, mentre SWD potrebbe essere più adatto per sistemi con risorse limitate. Considerare collettivamente questi fattori può aiutarti a prendere decisioni informate per uno sviluppo e un debug del sistema embedded più efficaci.