Introduzione al chip STM32F030

Il chip STM32F030 è un microcontrollore ARM Cortex-M0 a 32 bit a basso costo di STMicroelectronics. Dispone di fino a 32 KB di Flash e 4 KB di SRAM e può funzionare fino a 48 MHz. Include una varietà di periferiche, come comparatori analogici, timer e interfacce I2C e SPI. L’STM32F030 supporta anche applicazioni di controllo motore e dispone di un’ampia gamma di periferiche analogiche e digitali integrate. Le dimensioni ridotte e il basso consumo energetico del chip lo rendono ideale per l’uso in una varietà di applicazioni, dall’elettronica di consumo ai sistemi medici e industriali. Il prezzo e le prestazioni del chip rendono l’STM32F030 una scelta eccellente per gli sviluppatori attenti ai costi. Con il supporto di una varietà di strumenti di sviluppo, tra cui STM32Cube e lo strumento di configurazione grafica STM32CubeMX, è facile iniziare a lavorare con l’STM32F030 e sviluppare applicazioni innovative.

Parametri

– CPU: core ARM Cortex-M0 con architettura RISC a 32 bit

– Frequenza operativa: fino a 48 MHz

– Memoria programma: fino a 32 KB Flash

– RAM: fino a 4 KB

– Sorgente di clock: 8 MHz interna o 32 kHz esterna

– Uscita di clock: 2 x 32 kHz

– I/O digitali: fino a 36 pin I/O

– Ingressi analogici: fino a 8 canali ADC a 12 bit

– Timer: fino a 3 timer a 16 bit

– Interfacce di comunicazione: fino a 2 x I2C, 2 x USART, SPI, CAN

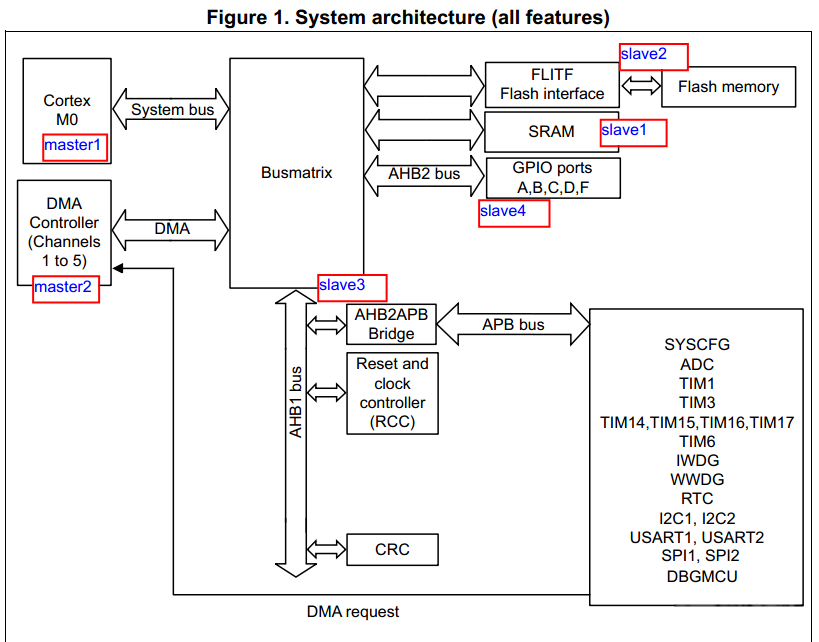

Architettura del sistema

Il framework di sistema interno di STM32F030 può essere semplicemente diviso in 2 sistemi master e 4 sistemi slave. I concetti di master e slave qui sono relativi a Busmatrix:

- Master

- Bus AHB del core Cortex-M0

- GP-DMA

- Slave

- SRAM interna

- Flash interna

- AHB2APB

- AHB alle porte GPIO

La relazione tra 2 master e 4 slave è mostrata nella figura seguente in modo più dettagliato e contrassegnata:

Per il bridge AHB2APB, se si desidera utilizzare le periferiche connesse al bus APB, è necessario chiamare un registro come RCC_AHBENR per abilitare prima il clock della periferica e la periferica è il driver della periferica. Questi dettagli sono generalmente gestiti nell’API del driver ST.

Panoramica della memoria

Nel programma STM32F030, dati, registri e porte IO sono tutti mappati allo spazio di indirizzi di 4 GB (macchina a 32 bit). La mappa della memoria di STM32F030 è dettagliata nella scheda tecnica.

SRAM

La SRAM STM32F030 ha una dimensione di 8 KB e può essere acceduta in unità di byte, word e half-word. Questa sezione viene utilizzata per memorizzare il codice compilato e collegato, i dati e lo stack del programma durante l’esecuzione. I dati vengono costantemente letti o scritti in questa SRAM durante l’esecuzione del programma.

Flash

La memoria flash interna della STM32F030 è generalmente sufficiente per l’uso, poiché è progettata per questo scopo. Ha 64KB di spazio flash utente. La flash all’interno del chip è chiamata flash interna o ROM (ROM e flash differiscono nel fatto che la ROM non può essere cancellata dall’utente ed è fissa durante la produzione del chip, mentre la flash può essere cancellata e riscritta in qualsiasi momento).

La memoria flash interna della STM32F030 è divisa in due tipi:

- 64KB di spazio flash utente: utilizzato per scaricare il codice .bin generato dalla compilazione e dal linking dell’utente.

- Info flash: include byte di opzione e memoria di sistema.

I byte di opzione possono essere utilizzati per configurare alcune funzioni del CI.

La memoria di sistema è la memoria del CI, che contiene un segmento di codice fisso durante la produzione del CI che non è open source e il cui funzionamento può essere solo ipotizzato. Lo scopo della memoria di sistema è quello di agire come un bootloader integrato. Generalmente, non viene utilizzato per il debug. L’uso tipico è collegare un debugger tramite un’interfaccia SWD al CI e scaricare e debuggare facilmente il codice. Tuttavia, per i prodotti, l’interfaccia SWD potrebbe non essere esposta. In questo caso, il codice .bin del prodotto può essere scaricato ed eseguito tramite il bootloader di memoria di sistema interno del CI tramite un’interfaccia seriale, che è il processo tipico per gli aggiornamenti del firmware. STM fornirà l’interfaccia e la demo di utilizzo del bootloader di memoria di sistema e ci sono molte documentazioni correlate che spiegano come utilizzarlo.

Configurazione del Boot

Il debug tramite SWD è chiamato “programmazione di sistema,” mentre il caricamento e l’avvio dei programmi utilizzando un bootloader è considerato “programmazione applicativa.” STM ha tre modalità di boot configurabili per diversi scenari applicativi.

Configurazione della modalità di boot:

Innanzitutto, c’è un pin di boot che si connette a livelli alti o bassi. Quando il chip si avvia, controlla il livello del pin di boot e passa alla modalità di boot corrispondente. Inoltre, nBOOT1 può essere configurato nel byte di opzione per selezionare la modalità di boot corrispondente.

Classificazione delle modalità di boot:

Ci sono tre tipi: Boot flash utente, che è il più comune; dopo la compilazione e il linking, scaricare il codice, ripristinare ed eseguire il proprio codice flash. Boot memoria di sistema, che utilizza il bootloader interno del CI. Boot SRAM.

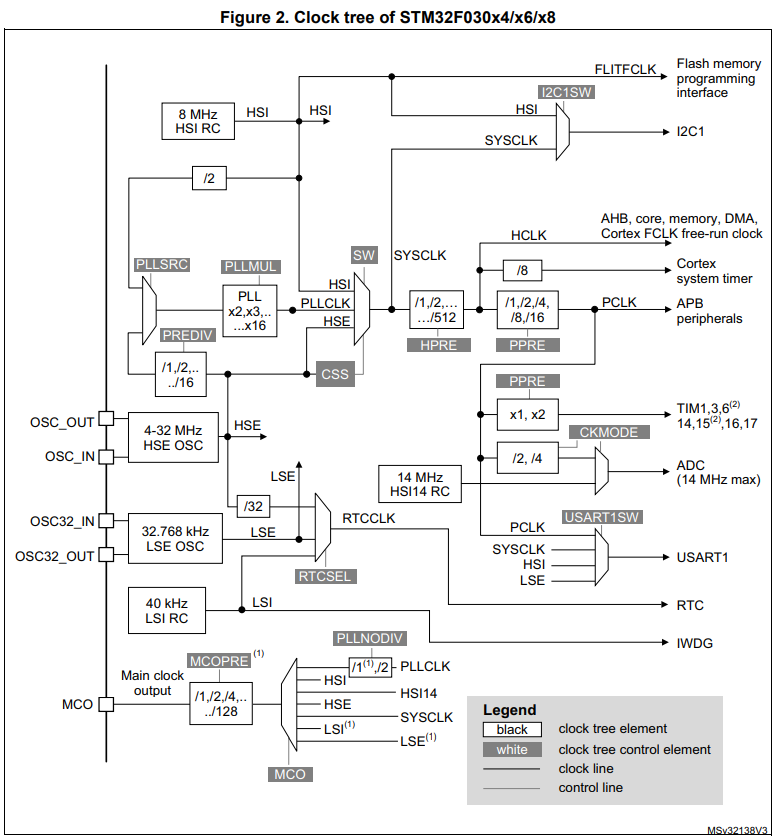

Frame di Clock

Il frame di clock della STM32F030 è il seguente e qui ci sono alcune definizioni di essi:

- HSI: chiamato clock interno ad alta velocità, è composto da oscillatore RC.

- HSE: chiamato clock esterno ad alta velocità, può essere collegato a un risonatore di quarzo/ceramica esterno, o a una sorgente di clock esterna.

- LSI: chiamato clock interno a bassa velocità, composto da un oscillatore RC, ha una bassa frequenza e la STM32F030 è di 40kHz.

- LSE: chiamato clock esterno a bassa velocità, generalmente collegato con un cristallo di quarzo con una frequenza esterna di 32.768kHz.

- PLL: è l’uscita moltiplicatore del loop a fase chiusa.

- HSI14 RC: la sorgente di clock può essere utilizzata per ADC da solo.

Le periferiche che non sono specificamente indicate utilizzano generalmente PCLK. Ecco un breve elenco delle situazioni che devono essere abilitate con AHB/APB in base al codice specifico:

- Utilizzare AHB come sorgente di clock: GPIOA-F, TS, CRC, FLITF, SRAM, DMA1.

- Utilizzare APB1 come sorgente di clock: TIM2, TIM3, TIM6, TIM14, WWDG, SPI2, USART2, I2C1, I2C2, PWR, DAC, CEC.

- Utilizzare APB2 come sorgente di clock: SYSCFG, ADC1, TIM1, SPI1, USART1, TIM15, TIM16, TIM17, DBGMCU.

Funzione di reset

Il reset è una parte cruciale dell’avvio del sistema MCU. Quando il CI inizia a eseguire il programma, inizia dal reset, che è il primo passo dopo l’accensione del sistema.

Meccanismo di reset di Cortex-M0

Nel file di avvio di Cortex-M0, vedrai sempre il reset_handler, che si trova nella prima posizione della tabella dei vettori. L’indirizzo di Cortex-M0 è 0x0000 0004 e il valore PC quando Cortex-M0 inizia a funzionare è questo indirizzo. Nel reset_handler, viene generalmente chiamata la funzione SystemInit implementata dall’utente, che imposta il clock dei vari componenti necessari per il corretto funzionamento del sistema, facilitando il normale funzionamento del sistema in seguito. Quindi, viene chiamata la voce __main nella libreria, che dovrebbe eseguire un’elaborazione iniziale della libreria di runtime C e impostare lo stack.

Tipi di reset

Esistono tre tipi principali di reset per STM32F030: reset di alimentazione, reset di sistema e reset del dominio RTC.

Il reset di alimentazione è correlato all’alimentazione del CI. Questo reset è attivato dall’accensione e dal risveglio dallo standby e l’inizializzazione del sistema inizia dopo il reset.

Il reset di sistema è attivato dal sistema. Cioè, l’alimentazione è normale, ma se viene premuto il pulsante di reset, il registro corrispondente viene resettato dal software o il Watchdog viene attivato, questo reset si verificherà. Quando si verifica questo reset, l’unica differenza rispetto al reset di alimentazione è che il bit rilevante nel registro RCC_CSR utilizzato per indicare la sorgente del reset non verrà resettato, mentre tutti gli altri registri verranno resettati allo stato immediatamente dopo l’accensione.

L’attivazione del reset del dominio RTC è anche un trigger software. È attivato scrivendo nel bit corrispondente nel registro RCC_BDCR. Tuttavia, questo tipo di reset influisce solo su RTC e cristallo LSE, ecc.

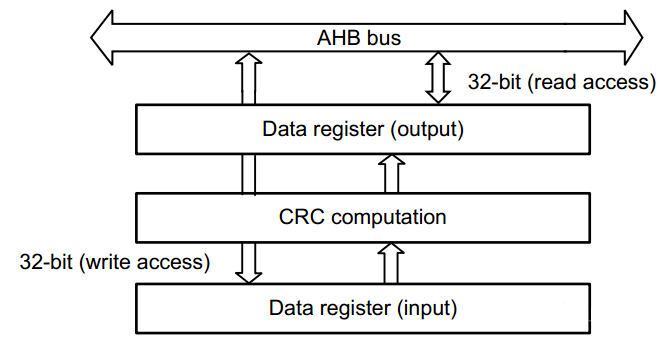

CRC

CRC, il controllo di ridondanza ciclico, è un algoritmo di controllo che verifica l’integrità dei dati trasmessi/memorizzati. Poiché può essere utilizzato in molti posti, STM32F030 implementa questo algoritmo con un’unità di calcolo hardware CRC nel CI. Quando un’applicazione deve utilizzare CRC, l’unità hardware può essere controllata dal software per realizzare i requisiti (ovviamente CRC può anche essere implementato via software, ma la velocità non è sicuramente veloce quanto la CRC hardware).

Il processo CRC è implementato all’interno del CI, quindi devi solo sapere come usarlo ed è molto semplice da usare. Scrivi i dati di origine che devono essere calcolati dal registro Dati (input), avvia il calcolo dell’unità di calcolo CRC, quindi leggi i risultati calcolati nel registro Dati (output).

In realtà, l’input e l’output del registro Dati CRC di STM32F030 utilizzano lo stesso registro, perché deve essere inserito prima e l’output può essere ottenuto prima di continuare al successivo input. Da questo processo si può vedere che l’input e l’output non vengono utilizzati contemporaneamente, quindi è possibile utilizzare direttamente un registro per multiplexare le due funzioni. Il registro può essere operato in 32 bit, 16 bit, 8 bit, che può soddisfare requisiti diversi.

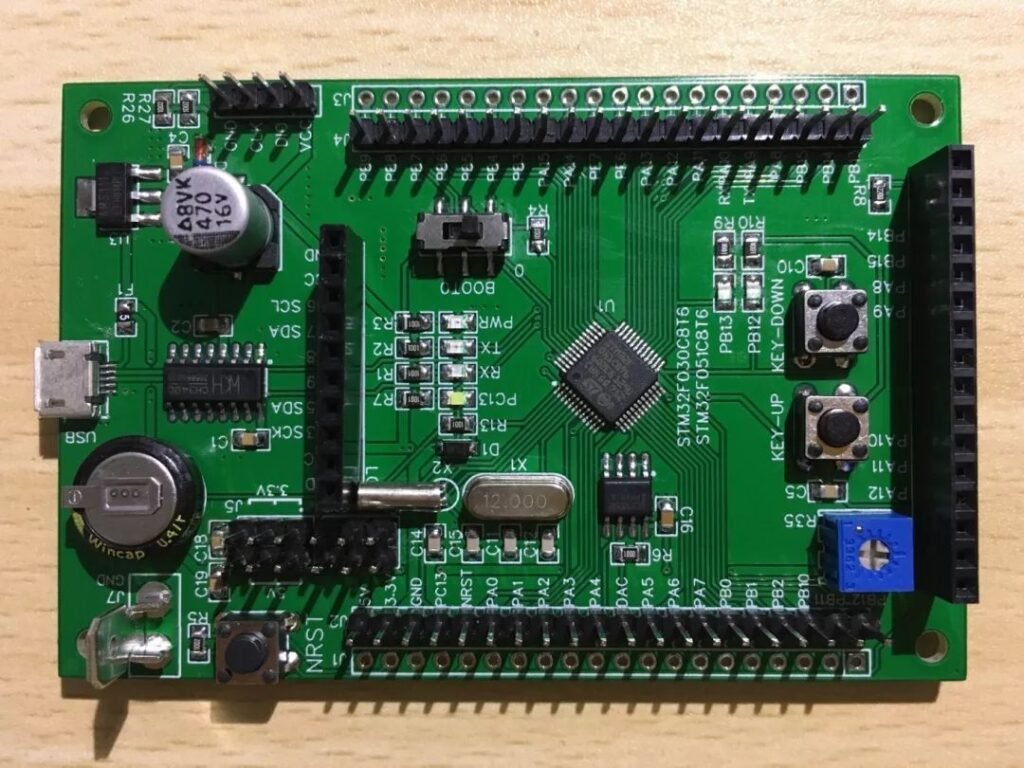

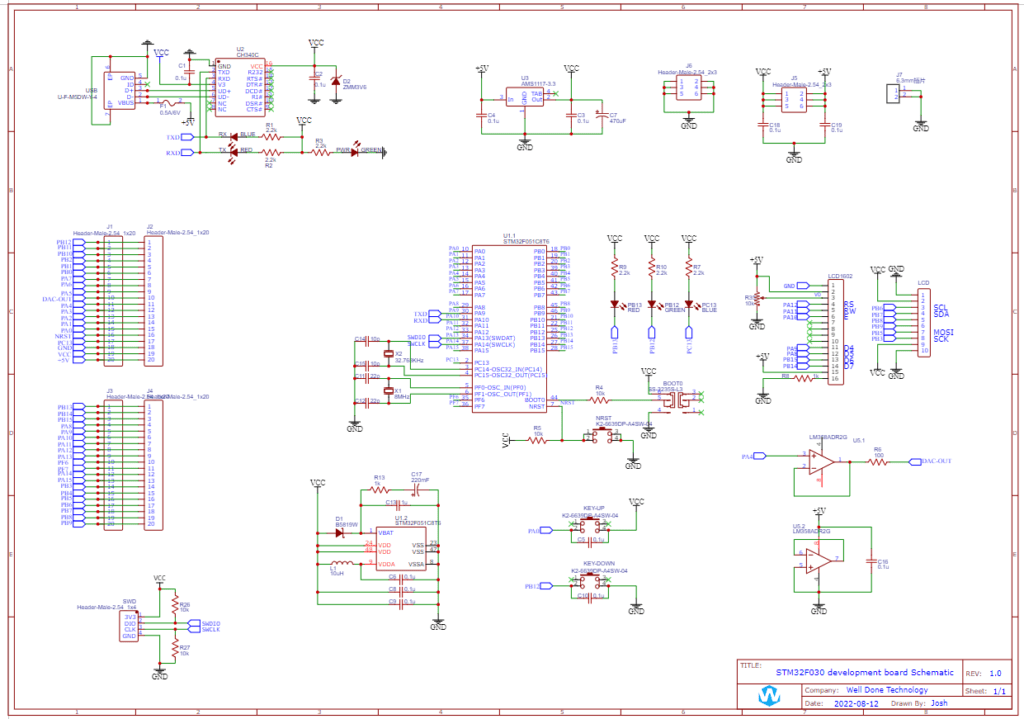

Scheda di sviluppo STM32F030 - STM32f0308 Discovery

Lo sviluppo di questo microcontrollore STM32F030 si basa sull’ultima libreria HAL di STM32, sul codice di inizializzazione generato da STM32CubeMX e il suo compilatore è GCC. Di seguito è riportato il suo schema, il diagramma PCB e la scheda assemblata. STM32 fornisce molte schede di sviluppo di livello base, come le serie Discovery e Nucleo. L’stm32f0308 discovery è una delle schede della serie Discovery, che è dotata del chip STM32F030.

Le funzioni e le caratteristiche di base delle schede di sviluppo della serie Discovery sono simili, ma le capacità dei chip di accompagnamento possono variare. Le caratteristiche dell’stm32f0308 discovery sono le seguenti:

Estensione comoda della porta IO: Con un solo cavo USB collegato a un PC, lo sviluppo può essere eseguito. Le porte IO del chip STM32F030 sulla scheda di sviluppo sono estese, rendendo facile la connessione a diversi dispositivi utilizzando cavi DuPont.

Interfaccia di debug: La scheda di sviluppo è dotata di un’interfaccia di debug SWD integrata, che viene implementata utilizzando un altro chip Cortex-M3 di ST (attualmente, la versione v9 di JLINK sul mercato dovrebbe utilizzare anche il chip Cortex-M3 di ST). Questa interfaccia di debug SWD può essere utilizzata separatamente tramite il collegamento di un cappuccio di salto, il che significa che l’stm32f0308-discovery può essere utilizzato come debugger SWD autonomo.

Alimentazione flessibile: La scheda di sviluppo è alimentata da USB, ma ha un circuito di conversione di tensione che può fornire alimentazione a 5V e 3V per l’uso da parte di dispositivi esterni (nota che la corrente di alimentazione è ancora limitata). Generalmente, piccoli moduli e interfacce possono essere alimentati direttamente da esso.

Periferiche a livello di scheda: Poiché si tratta di una scheda di sviluppo entry-level e a basso costo, le periferiche integrate sono molto semplici, costituite da due pulsanti e quattro LED. Dei due pulsanti, uno è utilizzato per il reset e l’altro è un pulsante programmabile dall’utente. Dei quattro LED, uno è un indicatore di alimentazione, uno è un indicatore di stato di debug SWD e i restanti due possono essere programmati per il controllo. Quindi, in realtà, le periferiche integrate che possono essere programmate per il controllo sono solo un pulsante utente e due LED utente.

Prestazioni

- Interfaccia SWD riservata per il debug tramite ST-LINK;

- L’interfaccia PA4 (uscita DAC) con elevata capacità di pilotaggio della porta;

- Due pulsanti touch leggeri e 3 LED per un facile debug;

- Interfaccia LCD1602 e un’interfaccia compatibile con LCD TFT comuni;

- Utilizzare un supercondensatore come alimentazione di backup RTC;

- Interfaccia USB con protezione dell’alimentazione;

- Diversi punti di test dell’alimentazione per oscilloscopio o multimetro.