Con l’aumento della velocità di commutazione dell’uscita dei circuiti integrati e l’aumento della densità delle schede PCB, l’integrità del segnale è diventata uno dei problemi che devono essere considerati nella progettazione di PCB digitali ad alta velocità. Poiché i problemi di integrità del segnale possono causare l’emissione di dati errati da parte del sistema, il circuito non funziona correttamente o addirittura non funziona affatto. Quindi, come considerare appieno il fattore di integrità del segnale nel processo di progettazione della scheda PCB e adottare misure di controllo efficaci? Si prega di leggere ulteriormente questo articolo.

Cos'è l'integrità del segnale PCB?

L’integrità del segnale PCB si riferisce alla capacità del segnale di rispondere con il tempo e la tensione corretti nel circuito. È uno stato in cui il segnale non è danneggiato e indica la qualità del segnale sulla linea di segnale.

Diversi problemi di integrità del segnale

I problemi di integrità del segnale possono causare o portare direttamente a distorsioni del segnale, errori di temporizzazione, dati, linee di indirizzo e di controllo errati, malfunzionamenti del sistema e persino arresti anomali del sistema. I principali problemi di integrità del segnale includono: ritardo, riflessione, rumore di commutazione sincrono, oscillazione, rimbalzo di massa, diafonia, ecc.

Ritardo

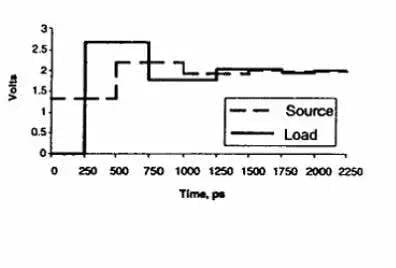

Il ritardo significa che il segnale viene trasmesso a una velocità limitata sui fili della scheda PCB e il segnale viene inviato dall’estremità di invio all’estremità di ricezione e c’è un ritardo di trasmissione tra di loro. Il ritardo del segnale influirà sulla temporizzazione del sistema e il ritardo di trasmissione dipende principalmente dalla lunghezza del filo e dalla costante dielettrica del mezzo attorno al filo. In un sistema digitale ad alta velocità, la lunghezza della linea di trasmissione del segnale è il fattore più diretto che influisce sulla differenza di fase dell’impulso di clock. La differenza di fase dell’impulso di clock significa che i due segnali di clock generati contemporaneamente non sono sincronizzati quando arrivano all’estremità di ricezione. La differenza di fase dell’impulso di clock riduce la prevedibilità dell’arrivo del bordo del segnale. Se la differenza di fase dell’impulso di clock è troppo grande, verrà generato un segnale errato all’estremità di ricezione. Come mostrato nella figura seguente, il ritardo della linea di trasmissione è diventato una parte importante del ciclo dell’impulso di clock.

Riflessione

La riflessione è l’eco sulla sottolinea di trasmissione. Quando il tempo di ritardo del segnale è molto più lungo del tempo di transizione del segnale, la linea del segnale deve essere considerata una linea di trasmissione. Quando l’impedenza caratteristica della linea di trasmissione non corrisponde all’impedenza di carico, una parte della potenza del segnale (tensione o corrente) viene trasmessa sulla linea e raggiunge il carico, ma una parte viene riflessa. Se l’impedenza di carico è inferiore all’impedenza originale, la riflessione è negativa. Altrimenti, la riflessione è positiva. Le variazioni della geometria del routing, la terminazione impropria della linea di trasmissione, la trasmissione attraverso i connettori e le discontinuità nei piani di alimentazione possono causare tali riflessioni.

Rumore di commutazione simultaneo (SSN)

Il rumore di commutazione simultaneo verrà generato se molti segnali digitali sulla PCB vengono commutati in modo sincrono (come il bus dati della CPU, il bus degli indirizzi, ecc.). Questo perché c’è impedenza sulla linea di alimentazione e a terra e ci sarà rimbalzo di massa sul piano di massa. La forza di SSN e del rimbalzo di massa dipende anche dalle caratteristiche I/O del circuito integrato, dall’impedenza dello strato di alimentazione e del piano PCB e dal layout e dal routing dei dispositivi ad alta velocità sulla PCB.

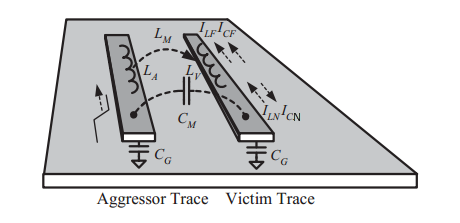

Diafonia

Il crosstalk è l’accoppiamento tra due linee di segnale e l’induttanza mutua e la capacità mutua tra le linee di segnale causano rumore sulla linea. L’accoppiamento capacitivo induce una corrente accoppiata mentre l’accoppiamento induttivo induce una tensione accoppiata. Il rumore di crosstalk ha origine dall’accoppiamento elettromagnetico tra reti di segnale, tra sistemi di segnale e sistemi di distribuzione dell’alimentazione e tra le vias. Il cross-winding può causare falsi clock, errori di dati intermittenti, ecc. e influire sulla qualità della trasmissione dei segnali adiacenti. In realtà, non è necessario eliminare completamente il crosstalk, ma mantenerlo entro la tolleranza del sistema. I parametri della scheda PCB, la spaziatura delle linee di segnale, le caratteristiche elettriche del driver e del ricevitore e il metodo di terminazione della linea di base hanno tutti un certo impatto sul crosstalk.

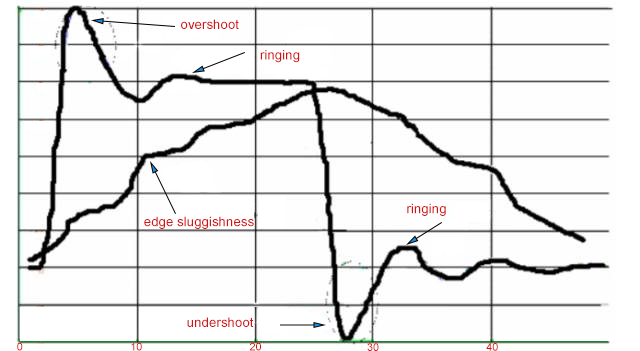

Overshoot e Undershoot

L’overshoot è il primo picco o valle che supera la tensione impostata. Per i fronti di salita, si riferisce alla tensione più alta e per i fronti di discesa, si riferisce alla tensione più bassa. L’undershoot si verifica quando il successivo valle o picco supera la tensione impostata. Un overshoot eccessivo può causare il funzionamento dei diodi di protezione, portando al loro guasto prematuro. Un undershoot eccessivo può causare errori di clock o dati spurii (gestione errata).

Ringing e Arrotondamento

Il fenomeno di oscillazione è l’overshoot e l’undershoot ripetuti. L’oscillazione del segnale è l’oscillazione causata dall’induttanza e dalla capacità di transizione sulla linea, che appartiene allo stato sottosmorzato. L’oscillazione di contorno è uno stato sovrasmorzato. Oscillazioni e oscillazioni orbitali, come le riflessioni, sono causate da una varietà di fattori. L’oscillazione può essere ridotta con una terminazione adeguata, ma non può essere completamente eliminata.

Rumore di Bounce a Massa e Rumore di Ritorno

Rumore di Bounce a Massa

Quando c’è un grande picco di corrente nel circuito, causerà rumore di bounce del piano di massa. Ad esempio, se le uscite di un gran numero di chip vengono accese contemporaneamente, ci sarà una grande corrente transitoria che scorre attraverso il piano di alimentazione del chip e della scheda. Rumore dell’alimentazione è quindi indotto dall’induttanza e dalla resistenza del package del chip e del piano di alimentazione, che crea fluttuazioni di tensione e variazioni sul vero piano di massa (O V). Questo rumore influisce sul funzionamento di altri componenti. Un aumento della capacità di carico, una diminuzione della resistenza di carico, un aumento dell’induttanza di massa e un aumento del numero di dispositivi di commutazione porteranno tutti a un aumento del bounce a massa.

Rumore di Ritorno

Il rumore di ritorno del piano di massa viene generato quando i segnali digitali viaggiano nell’area di massa analogica. Questo può essere causato dalla divisione del piano di massa (inclusi alimentazione e massa), ad esempio, il piano di massa è diviso in massa digitale, massa analogica, massa di schermatura, ecc. Allo stesso modo, i piani di alimentazione possono anche essere suddivisi in 2,5 V, 3,3 V, 5 V, ecc. Pertanto, nella progettazione di PCB multi-tensione, dobbiamo prestare particolare attenzione al rumore di bounce e al rumore di ritorno del piano di massa.

Cause dei Problemi di Integrità del Segnale

Fattori come i parametri dei componenti e delle schede PCB, il layout dei componenti sulle schede PCB e il cablaggio delle linee di segnale ad alta velocità causeranno problemi di integrità del segnale. Per il layout del PCB, l’integrità del segnale deve fornire Per il layout del circuito, l’integrità del segnale richiede componenti di terminazione, strategie di posizionamento e informazioni di routing.

Come Ottimizzare l'Integrità del Segnale?

Il problema dell’integrità del segnale non è causato da un singolo fattore, ma causato da molteplici fattori nella progettazione a livello di scheda. Pertanto, dobbiamo utilizzare metodi diversi per migliorare l’integrità del segnale in base a situazioni specifiche.

Analisi del Crosstalk

La dimensione delle interferenze è inversamente proporzionale alla spaziatura delle linee e proporzionale alla lunghezza parallela della linea e alla frequenza del segnale. Le interferenze variano in base al carico del circuito. Per la stessa topologia e situazione di cablaggio, maggiore è il carico, maggiori sono le interferenze. Nei circuiti digitali, il cambiamento del bordo del segnale ha il maggiore impatto sulle interferenze e più velocemente cambiano i bordi, maggiori sono le interferenze. Alla luce delle caratteristiche di cui sopra, possiamo utilizzare i seguenti metodi per ridurre le interferenze:

- Scegliere un dispositivo lento per ridurre la velocità di transizione del bordo del segnale;

- Evitare di mescolare diversi tipi di segnali;

- Ridurre le interferenze di accoppiamento riducendo il carico;

- Minimizzare la lunghezza parallela tra le linee di trasmissione adiacenti;

- Aumentare la distanza tra i conduttori dove può verificarsi un accoppiamento capacitivo;

- Un approccio più efficace è isolare i fili con fili di massa;

- Inserire un filo di massa tra i fili di segnale adiacenti;

- Minimizzare il numero di loop e l’area del loop;

- Evitare di condividere lo stesso filo per il loop del segnale;

- I livelli di segnale di due strati adiacenti dovrebbero evitare il cablaggio parallelo il più possibile;

- I segnali sensibili alle interferenze dovrebbero essere disposti il più possibile nello strato interno;

analisi della riflessione

Le riflessioni si verificano ogni volta che un segnale incontra una variazione di impedenza mentre viaggia lungo una linea di trasmissione. Il modo principale per risolvere il problema della riflessione è eseguire l’adattamento dell’impedenza di terminazione. Esistono solitamente due strategie per la terminazione della linea di trasmissione: terminazione parallela e terminazione seriale.

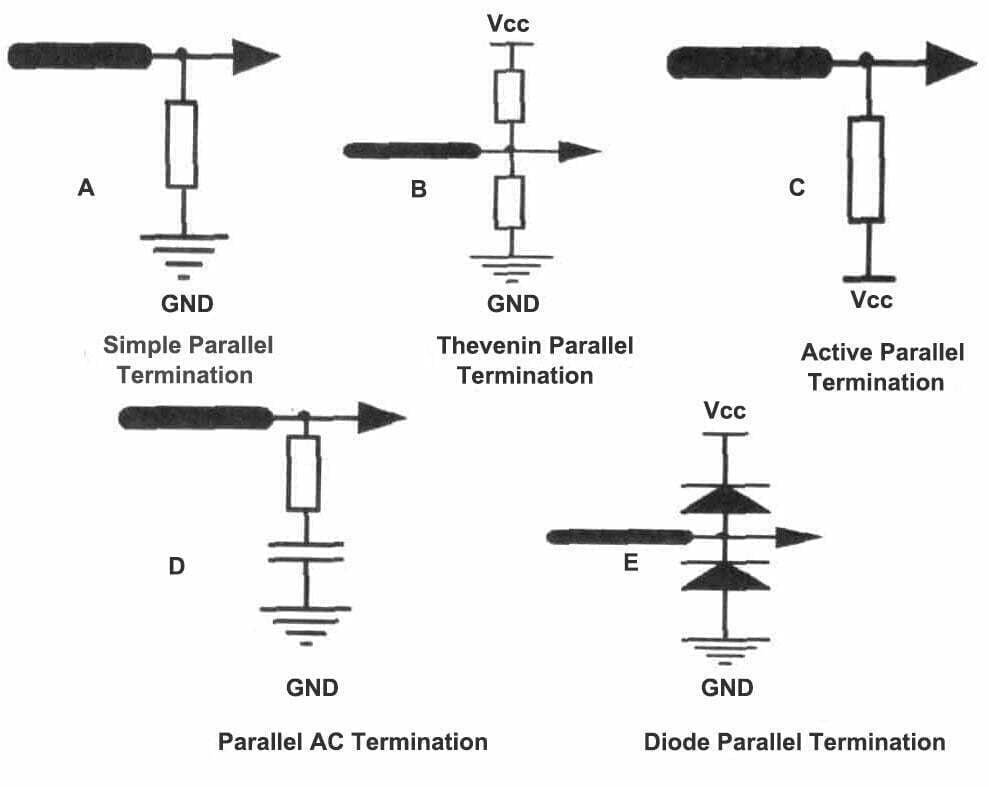

Terminazione Parallela

La terminazione parallela consiste principalmente nel collegare l’impedenza di pull-up o pull-down il più vicino possibile al carico finale per ottenere l’adattamento dell’impedenza del terminale. A seconda dei diversi ambienti applicativi, la terminazione parallela può essere suddivisa in diversi tipi come mostrato nella figura seguente.

Terminazione Seriale

La terminazione seriale si ottiene inserendo in serie una resistenza nella linea di trasmissione il più vicino possibile alla sorgente. La terminazione seriale consiste nell’adattare l’impedenza della sorgente del segnale, la resistenza della resistenza seriale inserita più l’impedenza di uscita della sorgente di pilotaggio dovrebbe essere maggiore o uguale all’impedenza della linea di trasmissione. Questa strategia sopprime il segnale riflesso dal carico rendendo il coefficiente di riflessione dell’estremità della sorgente pari a zero (l’ingresso dell’estremità del carico è ad alta impedenza e non assorbe energia) e quindi si riflette nuovamente all’estremità del carico dall’estremità della sorgente.

Modellazione dell'Analisi dell'Integrità del Segnale

Una corretta modellazione e simulazione del circuito è la soluzione di integrità del segnale più comune. Nella progettazione di circuiti ad alta velocità, l’analisi della simulazione sta sempre più dimostrando la sua superiorità. Perché può fornire ai progettisti risultati di progettazione accurati e intuitivi. In questo modo, possiamo rilevare i problemi in anticipo e correggerli in tempo. Esistono tre metodi di modellazione del circuito comunemente utilizzati: modello SPICE, modello IBIS e modello Verilog-A.

Modello SPICE

SPICE è un potente simulatore di circuiti analogici di uso generale. È costituito da due parti: Equazione del Modello e Parametri del Modello. Poiché viene fornita l’equazione del modello, il modello SPICE può essere strettamente collegato all’algoritmo del simulatore e possono essere ottenute una migliore efficienza analitica e risultati analitici.

Modello IBIS

Il modello IBIS è un modello utilizzato specificamente per l’analisi dell’integrità del segnale digitale a livello di scheda PCB e a livello di sistema. Utilizza la forma di tabelle I/V e V/T per descrivere le caratteristiche delle celle e dei pin di I/O dei circuiti integrati digitali. L’accuratezza dell’analisi del modello IBIS dipende principalmente dal numero di punti dati e dall’accuratezza dei dati nelle tabelle I/V e V/T. Rispetto al modello SPICE, il carico di calcolo del modello IBIS è molto piccolo.

Conclusione

Con il continuo sviluppo della microelettronica, l’uso di dispositivi ad alta velocità e la progettazione di sistemi digitali ad alta velocità sono in aumento. Anche le velocità dei dati di sistema, le frequenze di clock e le densità dei circuiti sono in aumento. Pertanto, i requisiti di progettazione per la scheda PCB sono sempre più elevati, in particolare il problema dell’integrità del segnale. Per garantire che la PCB abbia una buona integrità del segnale, è necessario considerare in modo completo una varietà di fattori che la influenzano.